华为Verilog基础教程:详解语句与建模

需积分: 0 10 浏览量

更新于2024-07-25

收藏 390KB PDF 举报

本华为Verilog教程是一份内部公开的入门指南,主要针对华为员工学习和理解Verilog高级硬件描述语言(HDL)设计。教程分为多个章节,涵盖了Verilog语言的基础知识和核心概念。

1. 章节概览:

- 第1章介绍了Verilog HDL的基本介绍,包括设计方法学和数字电路设计的基本原理,以及HDL在现代电子设计中的作用。

- 从第2章起,逐步深入到语言的结构:第3章讲述了模块设计,包括模块的定义、语法和简单的示例,强调了模块的结构化、数据流和行为描述方式。

- 第4章详细讲解了运算符和表达式的使用,涉及算术运算符、逻辑运算符、关系运算符以及不同类型的变量(如寄存器和线网类型)和数据类型。

- 行为建模是教程的重要部分,包括case和if-else语句、顺序语句块、过程赋值语句以及具体实例分析,展示了如何用Verilog描述系统的动态行为。

- 数据流建模部分介绍了如何利用连续信号和事件驱动的编程风格。

- 最后,附录A列出了Verilog保留字,便于读者查阅,而习题部分则提供了实践练习的机会。

2. 重要知识点:

- 语法基础:包括标识符的定义、书写规范、保留字和关键词的使用。

- 数据类型:理解不同类型的变量和数据结构,如整型、布尔型等。

- 运算符:掌握算术、逻辑、关系和条件运算符的用法,以及连接运算符在实际设计中的应用。

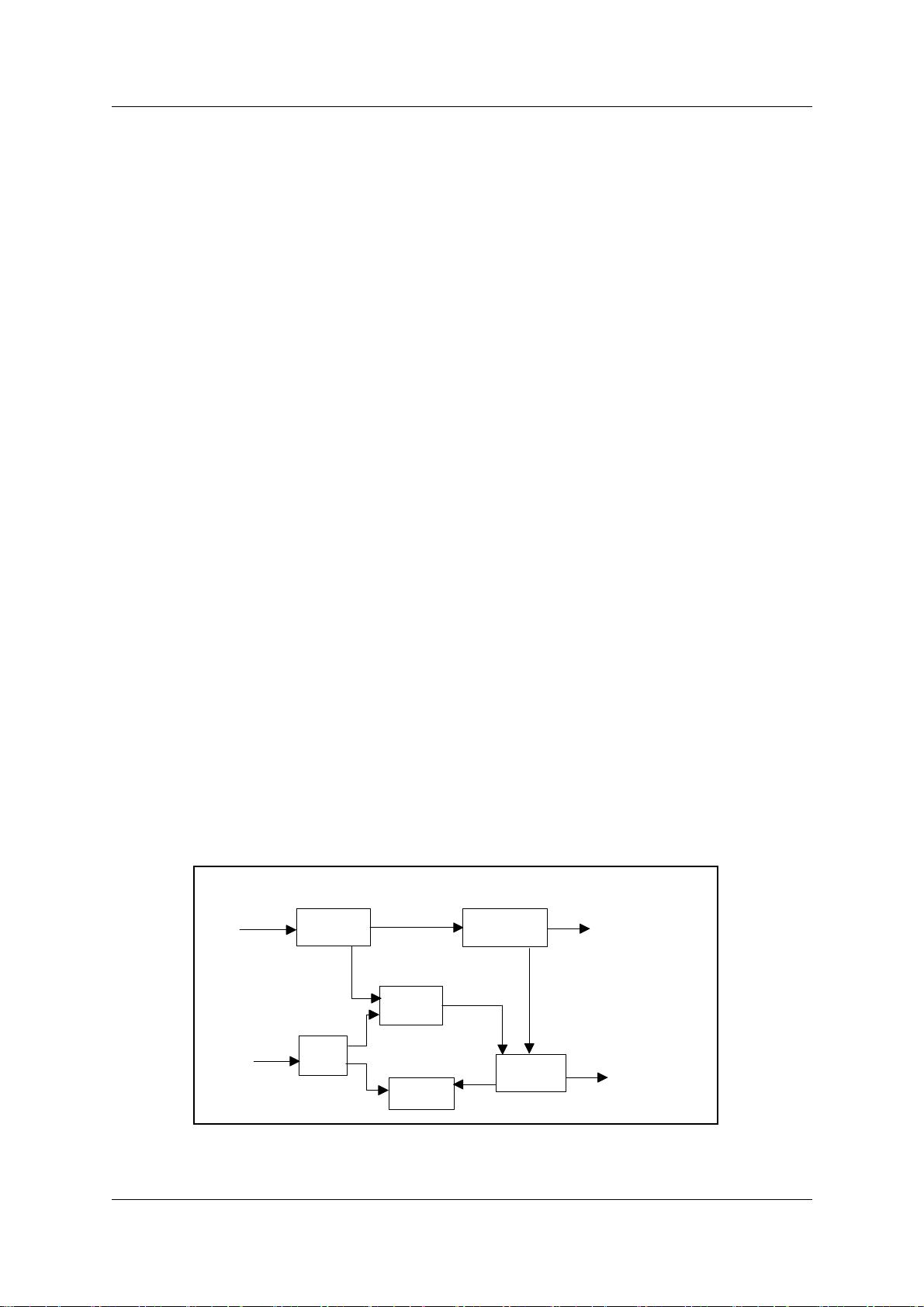

- 模块设计:模块的定义、结构和功能描述,以及如何进行混合、行为和数据流三种建模方式的选择。

- 行为建模:流程控制结构(如case和if-else)的使用,以及如何通过事件驱动实现系统行为的模拟。

- 调试与实践:通过习题和实例来巩固理论知识,提高编程能力。

3. 学习价值:

该教程对于希望学习或深入理解华为内部使用的Verilog设计语言的工程师具有很高的实用价值。它不仅提供了一套系统的学习路径,还为实际项目中的问题解决提供了指导,帮助工程师提升硬件描述能力,提高设计效率和代码质量。

这是一份全面且实用的华为Verilog教程,适合对HDL有初步了解的工程师作为进一步深入学习的参考资料。

点击了解资源详情

点击了解资源详情

101 浏览量

2012-03-09 上传

112 浏览量

2013-10-07 上传

2014-05-28 上传

120 浏览量

258 浏览量

redp

- 粉丝: 0

最新资源

- 掌握dig命令:Windows 10 BIND工具的安装与应用

- LBPhotoBrowser: 实现iOS下类似微信和今日头条的图片浏览器

- 易语言初级应用:掌握如果真命令例程

- 实现线性回归和逻辑回归类的关键技术分析

- 深入浅出MFC资料系列之必读

- 深度解析CSS在Portfolio制作中的应用技巧

- TheTracer路由跟踪工具:实用便捷的网络分析解决方案

- Python实现的Yahtzee游艇游戏解析

- 解码汉字:Unicode编码大全及其在Java中的应用

- iOS自适应表单封装:编辑与附件功能详细介绍

- 安卓与服务端通信技术实现及源码分析

- AR.js库新进展:实现60fps移动增强现实体验

- CSFramework: 强大的C/S模式中间件,支持灵活扩展和二次开发

- 微软Windows运行库合集2015.01版完整下载

- 实现aui-tab底部选项卡内容动态切换的开发示例

- Java应用程序:Anagram字谜查找器使用指南