详解DDR内存时序:提升系统性能的关键

需积分: 48 33 浏览量

更新于2024-09-15

收藏 138KB DOC 举报

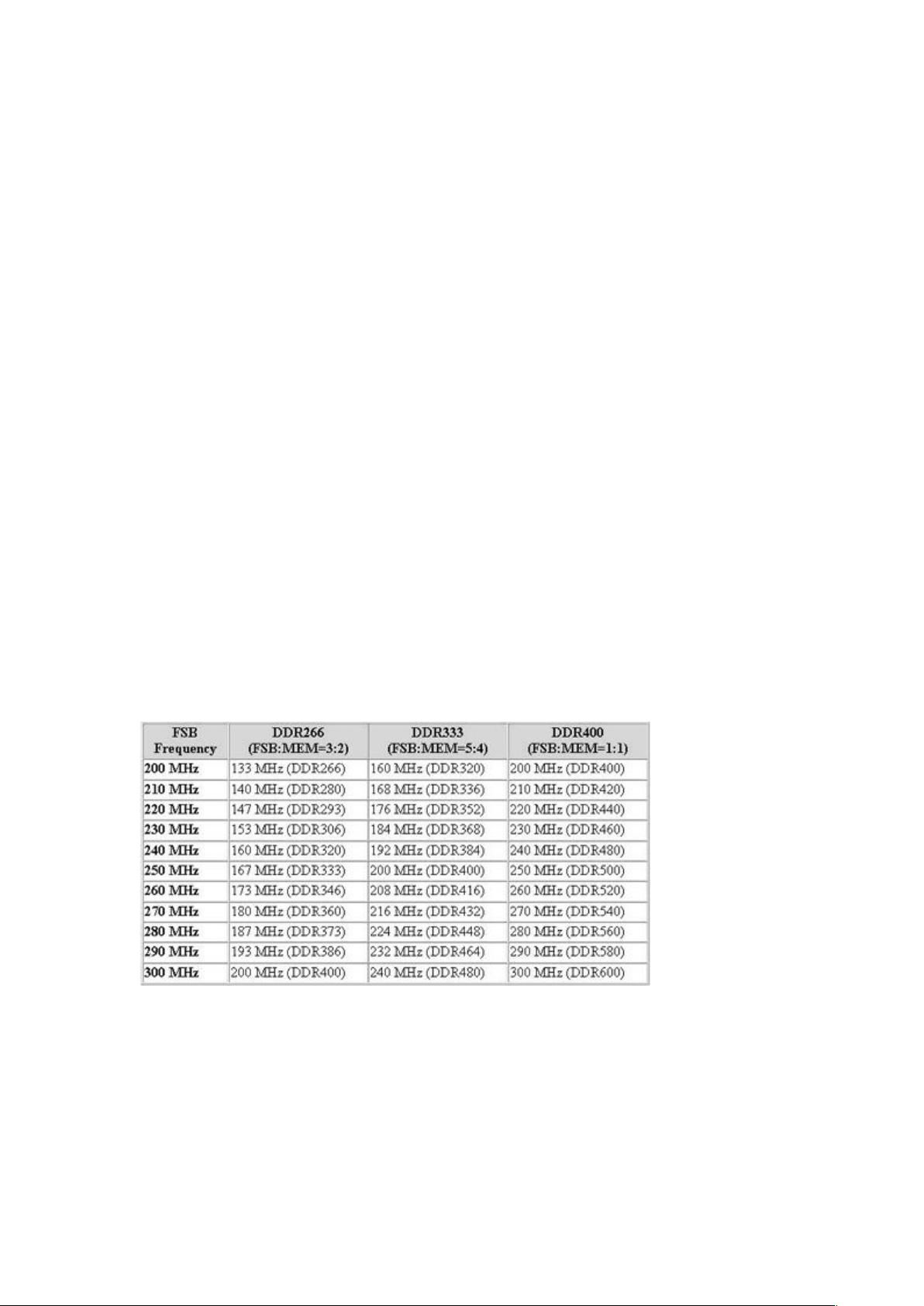

本文详细讲解了内存时序在现代DDR内存系统中的关键作用,特别是它与传统SDRAM的区别。DDR(双倍速率SDRAM)通过在时钟信号上升和下降边缘分别传输数据,实现了数据传输速率的翻倍,例如DDR400的实际工作频率仅为400MHz而非400MHz。理解FSB(前端总线)与内存频率之间的关系至关重要,同步设置(例如1:1)通常能最大化性能,比如DDR400需与200MHz FSB同步以达到480MHz的运行频率。

内存时序设置包括多个参数,如Command Per Clock (CPC)、CAS Latency Control (tCL)、RAS to CAS Delay (tRCD)、Min RAS Active Timing (tRAS)、Row Precharge Timing (tRP)、Row Cycle Time (tRC)、Row Refresh Cycle Time (tRFC)、Row to Row Delay (tRRD)以及Write Recovery Time (tWR)等。这些参数的准确设置直接影响系统的稳定性和性能提升。CPC是一个可选项,支持自动、启用单周期模式(1T)和禁用双周期模式(2T)。

在进行内存参数设置时,了解并优化这些时序参数对于充分利用内存带宽,提升系统的读写速度和响应能力至关重要。例如,合理的tCL值能控制内存数据访问延迟,tRP则控制行预充电时间以确保数据可靠读取,而tRFC则关乎内存刷新周期,避免数据丢失。每个参数都与内存操作的效率紧密相连,因此,根据具体硬件配置和应用需求进行精细化调整是提高计算机性能的关键步骤。

内存时序是理解现代内存技术的核心要素,通过深入学习和适当地调整这些参数,可以显著改善系统的性能表现,为用户提供流畅的计算体验。

1856 浏览量

2454 浏览量

173 浏览量

2012-11-06 上传

2728 浏览量

2009-12-21 上传

211 浏览量

hmanhcc

- 粉丝: 1

- 资源: 16

最新资源

- lppractice

- udacDescStats:Udacity 描述性统计课程的在线小程序

- amazing-compass.github.io:Gridea_blog

- 企业培训五大误区DOC

- Thermistor_library:热敏电阻非常简单但完整且可配置的热敏电阻库

- Java项目之移动ssh项目(struts+spring+hibernate+oracle)源代码

- alan:用于响应的UI组件

- hello-world-angular

- fort-w2021.github.io:202021 年高级编程课程网站

- latexdiff所需安装包.rar

- gap-tmbundle:用于GAP计算机代数系统的TextMate软件包

- 交流技巧培训DOC

- jdk-8u151-i586.zip

- alltrailstest

- intensity_interferrometry_layout_benchmark

- Closing:它是图像处理工具的基础,包括打开和关闭。-matlab开发