89C52单片机驱动电子秒表设计详解与应用

需积分: 10 122 浏览量

更新于2024-07-31

收藏 324KB DOC 举报

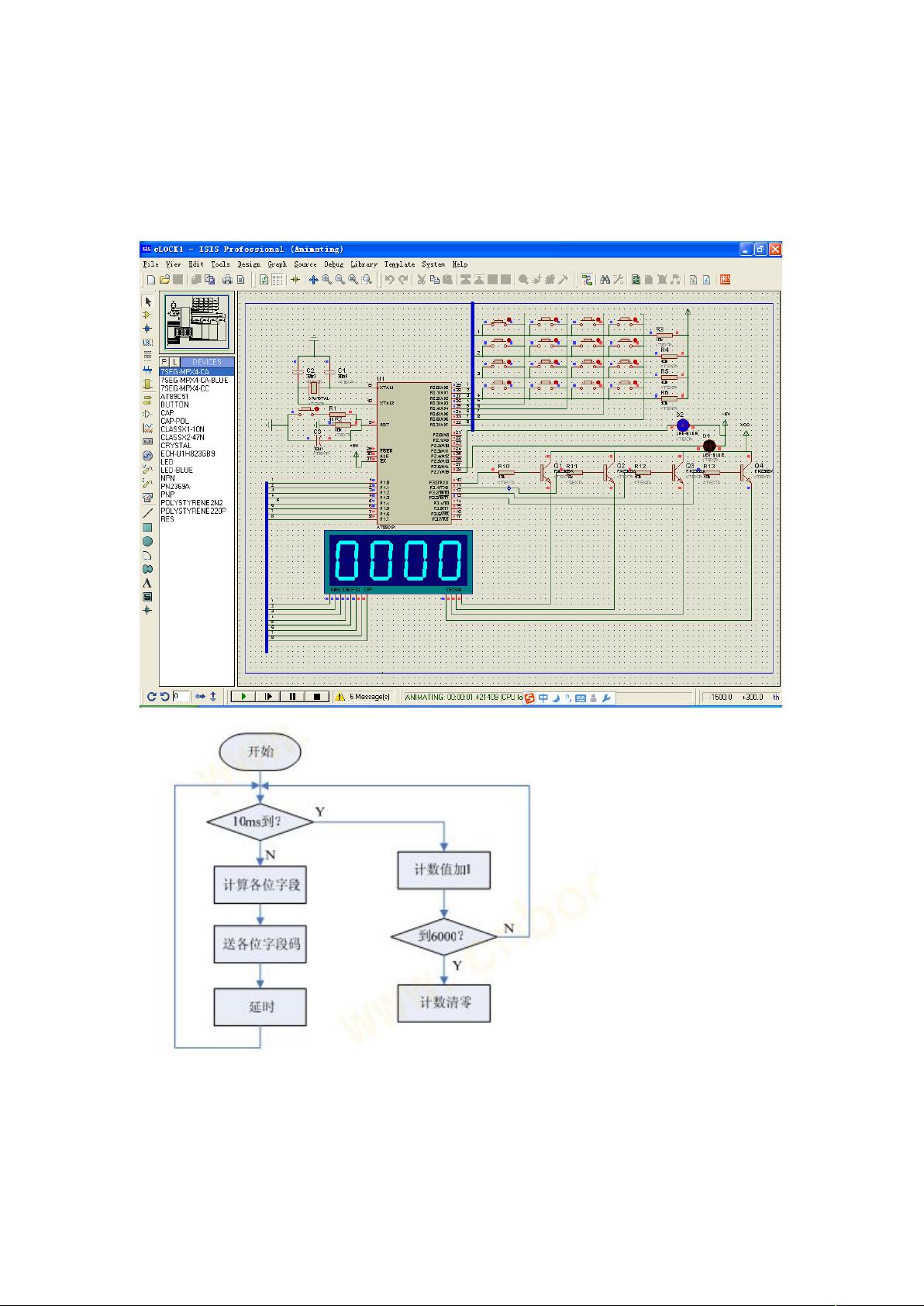

本文主要探讨的是基于单片机的电子秒表设计,其核心目标是通过构建一个能够计时99:99秒的秒表,具备启停复位和倒计时功能,以此深入理解单片机最小系统的工作原理以及单片机的关键功能模块,如定时器和中断处理。设计过程涵盖了以下几个关键知识点:

1. 单片机最小系统:电子秒表的设计首先从单片机最小系统出发,这是由电源、单片机、晶振、复位电路和输入输出接口等基本组件组成的基础平台,这些部分共同确保了单片机的正常运行。

2. 定时器应用:电子秒表的核心功能依赖于单片机的定时器,通过精确控制时间间隔,实现了秒表的计时和倒计时功能。通过实际操作,学习者能够深入理解定时器的原理和编程方法。

3. 中断功能:电子秒表中的开关控制、计时模式切换和倒计时设置涉及到中断技术的运用。中断使得单片机能在处理其他任务的同时,响应外部事件,如按键输入,确保操作的灵活性。

4. 键盘控制:文章中提到的独立式键盘设计,包括启动/停止/复位功能,以及计时模式选择和倒计时值设定,这些都是通过键盘接口实现的,展示了如何将用户输入转化为单片机内部的操作指令。

5. LED显示:四位一体共阳极LED显示器的使用,涉及LED显示原理和编程技巧。无论是静态显示还是动态显示,都需要掌握如何通过单片机控制LED的亮灭,以显示数字和字符。

6. 硬件选型与设计:文中明确了89C52系列单片机的选择,以及LED显示器的结构和工作方式,强调了硬件选择对整体设计的影响。

本文不仅提供了一个实际的电子秒表设计案例,还深入剖析了单片机技术在其中的应用,有助于读者提升对单片机系统设计和编程的理解。通过这个项目,学习者可以锻炼自己的硬件布局、软件算法和系统集成能力。

2016-04-14 上传

2023-02-27 上传

2024-10-31 上传

2024-10-31 上传

2023-06-10 上传

2024-10-31 上传

2024-10-27 上传

2024-10-27 上传

wzh0521

- 粉丝: 0

- 资源: 3

最新资源

- BottleJS快速入门:演示JavaScript依赖注入优势

- vConsole插件使用教程:输出与复制日志文件

- Node.js v12.7.0版本发布 - 适合高性能Web服务器与网络应用

- Android中实现图片的双指和双击缩放功能

- Anum Pinki英语至乌尔都语开源词典:23000词汇会话

- 三菱电机SLIMDIP智能功率模块在变频洗衣机的应用分析

- 用JavaScript实现的剪刀石头布游戏指南

- Node.js v12.22.1版发布 - 跨平台JavaScript环境新选择

- Infix修复发布:探索新的中缀处理方式

- 罕见疾病酶替代疗法药物非临床研究指导原则报告

- Node.js v10.20.0 版本发布,性能卓越的服务器端JavaScript

- hap-java-client:Java实现的HAP客户端库解析

- Shreyas Satish的GitHub博客自动化静态站点技术解析

- vtomole个人博客网站建设与维护经验分享

- MEAN.JS全栈解决方案:打造MongoDB、Express、AngularJS和Node.js应用

- 东南大学网络空间安全学院复试代码解析