LVDS接口终端匹配技术探讨

"LVDS终端阻抗匹配"

在电子通信领域,LVDS(Low Voltage Differential Signaling,低电压差分信号)是一种广泛应用于高速数据传输的标准,尤其在显示系统中非常常见。LVDS的优势在于其低功耗、高数据速率、低噪声免疫能力以及对热插拔的支持。本文主要探讨了LVDS接口的终端阻抗匹配技术和相应的抗噪声措施。

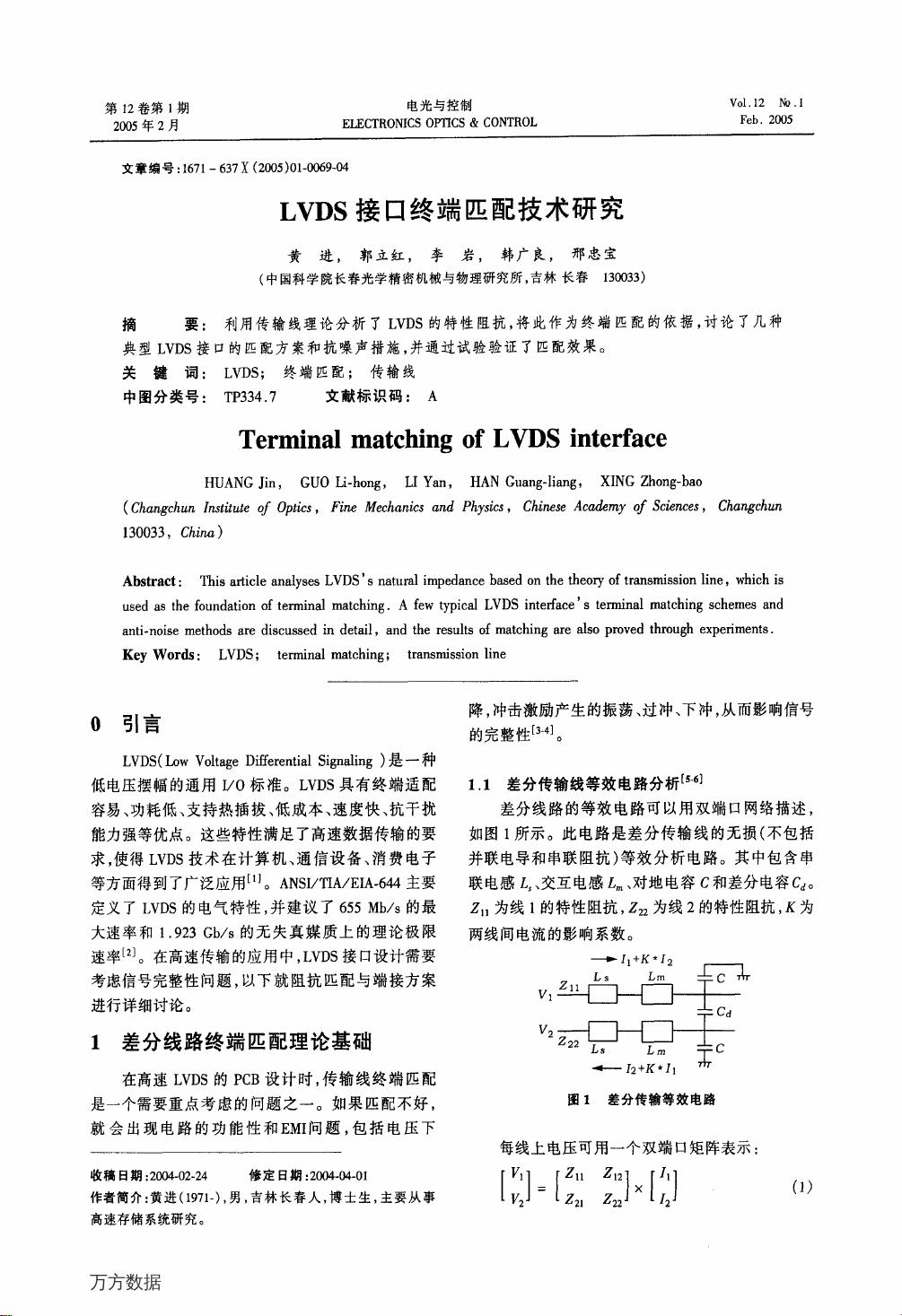

LVDS的工作原理基于传输线理论,其信号通过一对差分线进行传输,差分信号在两条线上同时以相反相位传播,这样可以极大地减少电磁干扰(EMI)并提高信号的完整性。LVDS信号的幅度通常非常低,这有助于降低功耗和电磁辐射。为了确保信号在传输过程中不发生反射和失真,终端阻抗匹配至关重要。

首先,我们需要理解LVDS的特性阻抗,这是传输线理论中的一个关键概念。特性阻抗是信号在传输线中遇到的一个理想阻抗值,当负载阻抗等于特性阻抗时,可以实现无反射传输。对于LVDS,这个特性阻抗通常为100欧姆,但具体数值可能会因不同的设计和应用而略有不同。因此,设计LVDS接口时,确保信号源、传输线路和接收端的阻抗都匹配于这个特性阻抗至关重要。

文章中提到了几种典型的LVDS接口匹配方案,包括使用电阻网络、变压器以及专用的LVDS收发器。例如,使用终端电阻是最常见的方法,通常在每个通道的接收端并联一个100欧姆的电阻到地,以模拟理想的差分负载。此外,通过变压器进行阻抗匹配可以进一步隔离信号源和负载,提供额外的噪声抑制。

在抗噪声措施方面,文章可能讨论了以下几点:

1. 屏蔽:使用屏蔽电缆和屏蔽层可以减少外部电磁干扰对LVDS信号的影响。

2. 布线技巧:遵循PCB布线规则,保持差分对的间距恒定,避免过大的回路面积以减少辐射和耦合。

3. 电源去耦:在电源引脚附近添加适当的去耦电容,以稳定电源电压,减少电源噪声对信号质量的影响。

4. 接地设计:良好的接地策略是减少噪声的关键,包括单点接地和星形接地等方法。

实验验证部分,作者可能通过实际测试评估了各种匹配方案的效果,包括信号完整性的改善、噪声抑制程度以及系统性能的提升。实验结果通常会展示匹配后的信号波形、眼图分析以及其他相关指标,以证明所提出的匹配方法的有效性。

LVDS终端阻抗匹配是确保高速数据传输可靠性和效率的关键技术,而有效的抗噪声措施则进一步增强了系统的稳定性。理解和掌握这些技术对于设计和优化LVDS系统至关重要。

5603 浏览量

290 浏览量

点击了解资源详情

点击了解资源详情

236 浏览量

199 浏览量

394 浏览量

265 浏览量

moc_book

- 粉丝: 0

最新资源

- BMP转JPG完整版模块压缩文件介绍

- VC++使用OpenGL制作屏幕对话框实例教程

- 掌握Netperf:网络性能测量的利器

- Mastercam 2D高速铣削技术手册详解

- 商务PPT专用:50个精致白色细线图标素材

- MSP430单片机编程:创建动态眨眼玩具项目

- Office 2007兼容包的安装与使用指南

- FXTableFilter: 强化HTML表格过滤功能的JQuery插件

- Java设计模式解析与应用大全

- 在Windows上使用mingW编译live555库

- 灰色细线风格商务PPT图标素材套装下载

- Rexams创建的Intro-stats教学材料:结合R语言、电子表格和Shiny应用

- 防止网页文字被复制的HTML与jQuery实现方法

- 模似点击按钮技术分享与应用

- 探索TypeScript在蛋糕店应用的实践

- VB专题播放器:以《壁花少年》为例制作教程