高精度SAR ADC支持电路设计:内部与外部基准比较与故障处理策略

189 浏览量

更新于2024-09-03

收藏 901KB PDF 举报

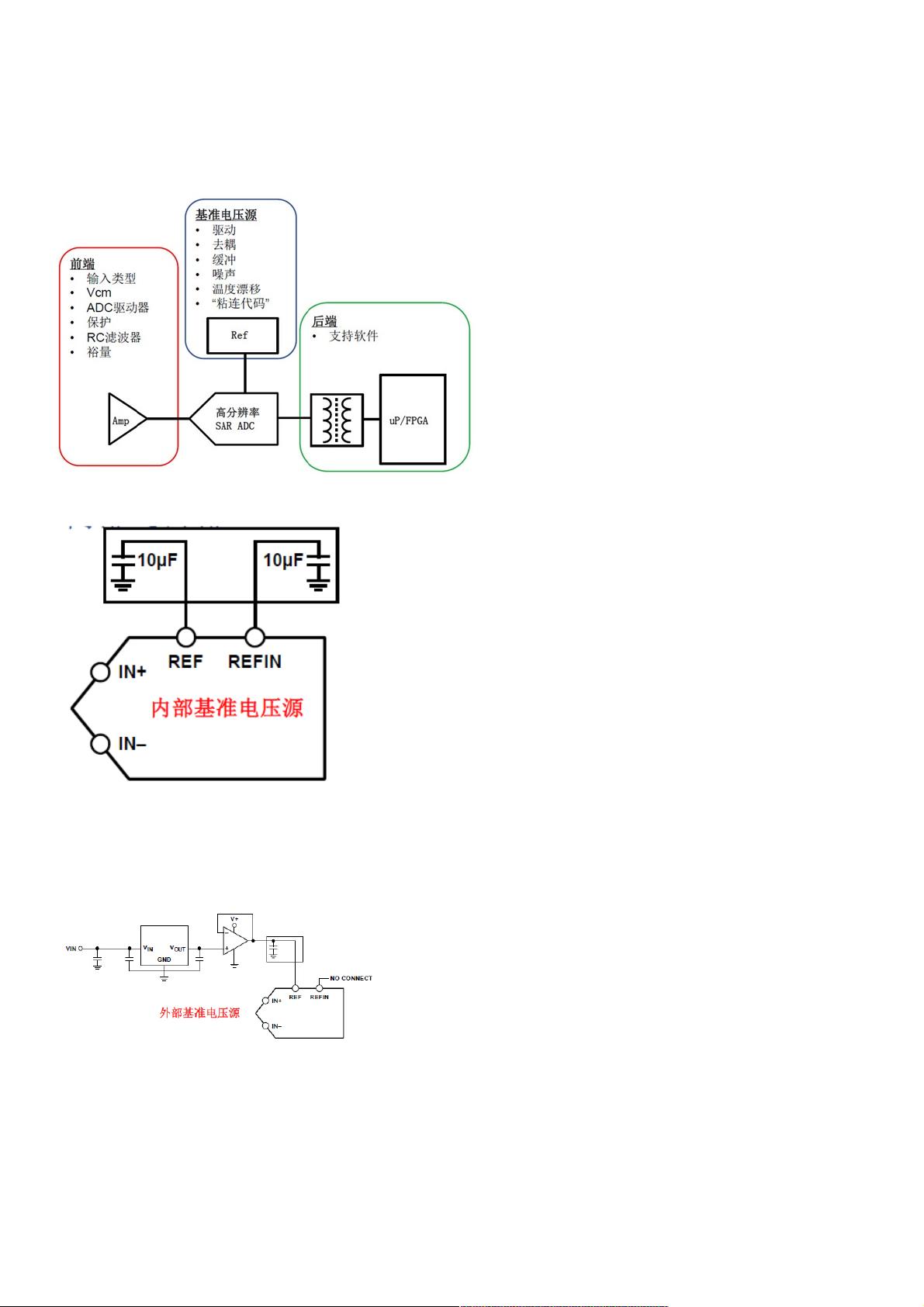

本文将深入探讨高精度逐次逼近型ADC(Successive Approximation Register, SAR)支持电路的设计以及故障排除策略。首先,我们关注的是SAR基准电压源的两种类型:内部和外部。内部基准电压源的优势在于其易用性与空间效率,它们直接集成在ADC内部,便于实现,但可能在性能上受限于集成的噪声水平、ppm/C温度漂移和初始精度。相比之下,外部基准电压源可以提供更高的性能,特别是在噪声控制和稳定性方面,但需要额外的电路设计以确保最佳效果。

SAR电路的核心组成部分包括基准电压输入(REF)与开关电容输入,后者在每次位检验阶段都会切换到REF,可能导致动态电流负载。吞吐速率和内部位检验时钟的选择对电流峰值有直接影响,特别是对于最高位(MSB),需要足够大的储能电容来保证基准电压的稳定性,通常推荐10微法特(μF)或更大。基准电压源在转换期间需为这些电容充电,同时基准电流应根据指定的吞吐速率进行调整,与之成正比。

基准电压输出驱动也是一个关键环节,可能采用带隙基准电压源配合缓冲器,如ADR43X和ADR45XX系列,以降低噪声并确保足够的电流负载能力。在突发模式下,基准电压源的性能可能会降低,因为其输出电流可能超过总输入电流的平均值,此时需要考虑基准电压源的吸电流功能,尤其是在故障条件下。

老式的基准电压源可能缺乏吸电流功能,仅提供电源电流,这在驱动多路ADC时可能成为问题。因此,针对这种情况,文章强调了基准电压缓冲器的使用,特别是在驱动多个ADC时,它能确保信号的稳定传输,抵抗高频和低频纹波,并且必须能够稳定地驱动大电容负载。此外,电路布局也很重要,比如将储能电容尽可能靠近REF引脚,以减小干扰,并通过星型连接至缓冲器以优化信号完整性。

在基准电压源补偿和噪声管理方面,文章提醒读者要考虑缓冲器本身的噪声特性,并通过适当的计算或选择来估算和减小总的噪声影响。对于同步采样型应用,每个SAR ADC都需要独立的基准电压源,确保每个电路板或系统中的信号处理一致性。

本文深入剖析了高精度逐次逼近型ADC支持电路设计的关键要素,包括基准电压源的选择、电流负载控制、噪声抑制以及故障条件下的应对策略,为工程师在实际应用中优化电路性能提供了宝贵指导。

高精度逐次逼近型SAR ADC电路设计成品:性能卓越,可应用于实际场景,含详细文档与仿真文件,高性能的16bit高精度SAR ADC电路设计成品:低功耗、适用入门学习和实践应用,16bit高精度逐次逼

2025-02-17 上传

高精度12bit逐次逼近型SAR ADC电路设计成品:全差分结构、SMIC 0.18μm工艺、低功耗与卓越性能的综合体现,高精度12bit逐次逼近型SAR ADC电路设计成品展示:SMIC 0.18μ

2025-02-19 上传

基于SMIC 0.18μm工艺的单端结构高精度SAR ADC电路设计成品:性能卓越,适用于实际应用,16bit高精度逐次逼近型SAR ADC电路设计成品 单端结构原理清晰,加上目前写过的最详细的设计与

2025-01-19 上传

2024-10-09 上传

高精度SAR ADC电路设计成品展示:专业技术的实现与应用(包括仿真文档及全差分结构设计文档),高精度12bit逐次逼近型SAR ADC电路设计成品 一款包含了第四个月学习的全部经验的高精度sarAD

2025-01-20 上传

基于台湾65nm工艺的16位SAR ADC模拟集成电路设计:高精度同步时序采样与珍贵ADC资料分享,【16位SAR ADC 逐次逼近型ADC模拟集成电路设计】 16位SAR ADC 同步时序; 采样率

2025-01-18 上传

2025-02-14 上传

2025-01-06 上传

2024-10-09 上传

weixin_38732307

- 粉丝: 13

最新资源

- JS房贷计算器使用教程与源码解析

- Nagios & Cacti监控系统安装与使用教程

- 安卓12306火车票余票查询系统源码解析

- 汇编语言教学资源:电子教案与单片机课件

- Python Divert库:网络数据转移控制技术

- Eclipse插件更新:Git 1.2.0 & SVN 1.8.4最新版本jar包

- 掌握CXF:视频教程与Spring集成实例解析

- C#实现的学校一卡通管理系统开发指南

- LED Player 3.3绿色版发布,轻量级LED控制软件

- 仿Discuz! 构建中国科技论坛源码详解

- Android录音变声及转mp3功能演示

- C语言编码转换工具:GBK与UTF-8互转

- AngelYoung团队DSC Hackathon 2021解决方案概述

- Android仿iPhone4位密码锁动画效果源码分享

- Linux之父Torvalds:编程的乐趣与人生享受

- 实现文本框监听与自动跳转功能的代码技巧