Verilog HDL时序篇探索:步骤、时钟与模块优化

需积分: 9 199 浏览量

更新于2024-07-17

收藏 9.46MB PDF 举报

"电子-VerilogHDL那些事儿时序篇.pdf,这是一本深入探讨Verilog HDL语言中时序概念的教程,由黑金动力社区荣誉出品,专注于单片机/嵌入式正点原子FPGA领域的学习。本书分为两大部分,上半部分关注‘步骤和时钟’,下半部分涉及‘综合和仿真’,旨在帮助读者更好地理解和优化Verilog HDL模块设计。"

Verilog HDL是一种广泛用于硬件描述的语言,它允许工程师构建和模拟数字系统的逻辑模型。在《Verilog HDL那些事儿-时序篇》中,作者强调了建模的重要性,尽管这只是初步创建模块的粗糙形状,但它却是设计的基础。建模后,可以通过细化进一步分析和优化模块,而这需要深入理解Verilog HDL语言。

书中上半部分的“步骤和时钟”深入探讨了这两个关键概念。在模块设计中,“步骤”可视为执行的节奏,对应着操作的过程或状态,而“时钟”则如同模块的心跳,定义了模块运行的时间基准。时钟对于模块的通信至关重要,因为它决定了数据传输的精确时刻。当设计变得更加复杂,传统的状态机可能导致模块内部结构臃肿和表达能力下降。引入“步骤”作为替代,可以实现更加灵活的建模策略,如仿顺序操作,以支持更复杂的设计需求。同时,“步骤”还有助于清晰指示模块的操作流程和状态,这对于模块的细化具有显著帮助。

另一方面,"时钟"与模块间的通信紧密相关。模块间的通信问题往往源于时钟同步问题,即一个模块可能比另一个模块提前或滞后一个时钟周期。在多模块设计中,理解和掌握时钟同步至关重要,它能帮助避免“沟通失误”,从而提高整个系统性能的稳定性和可靠性。

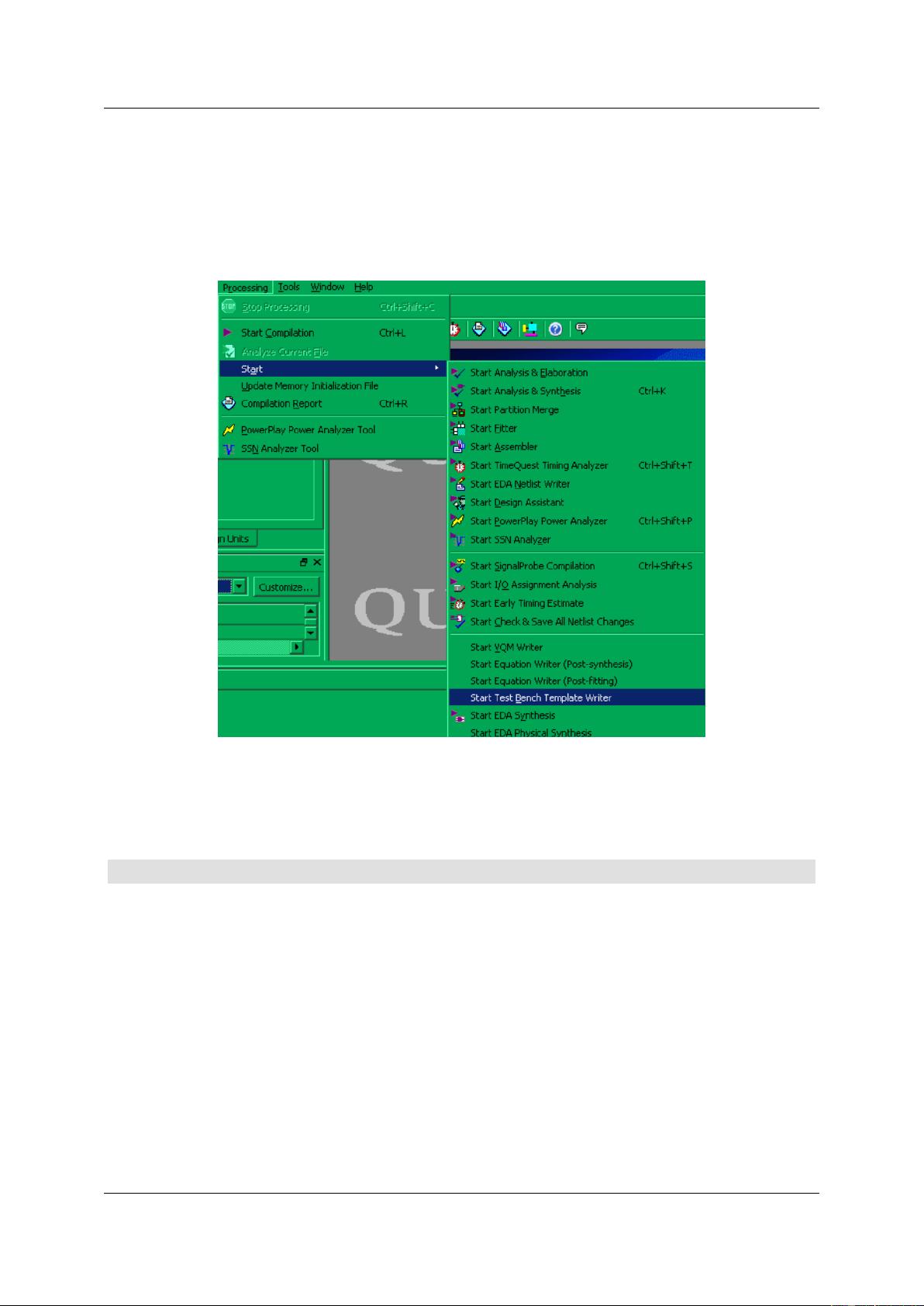

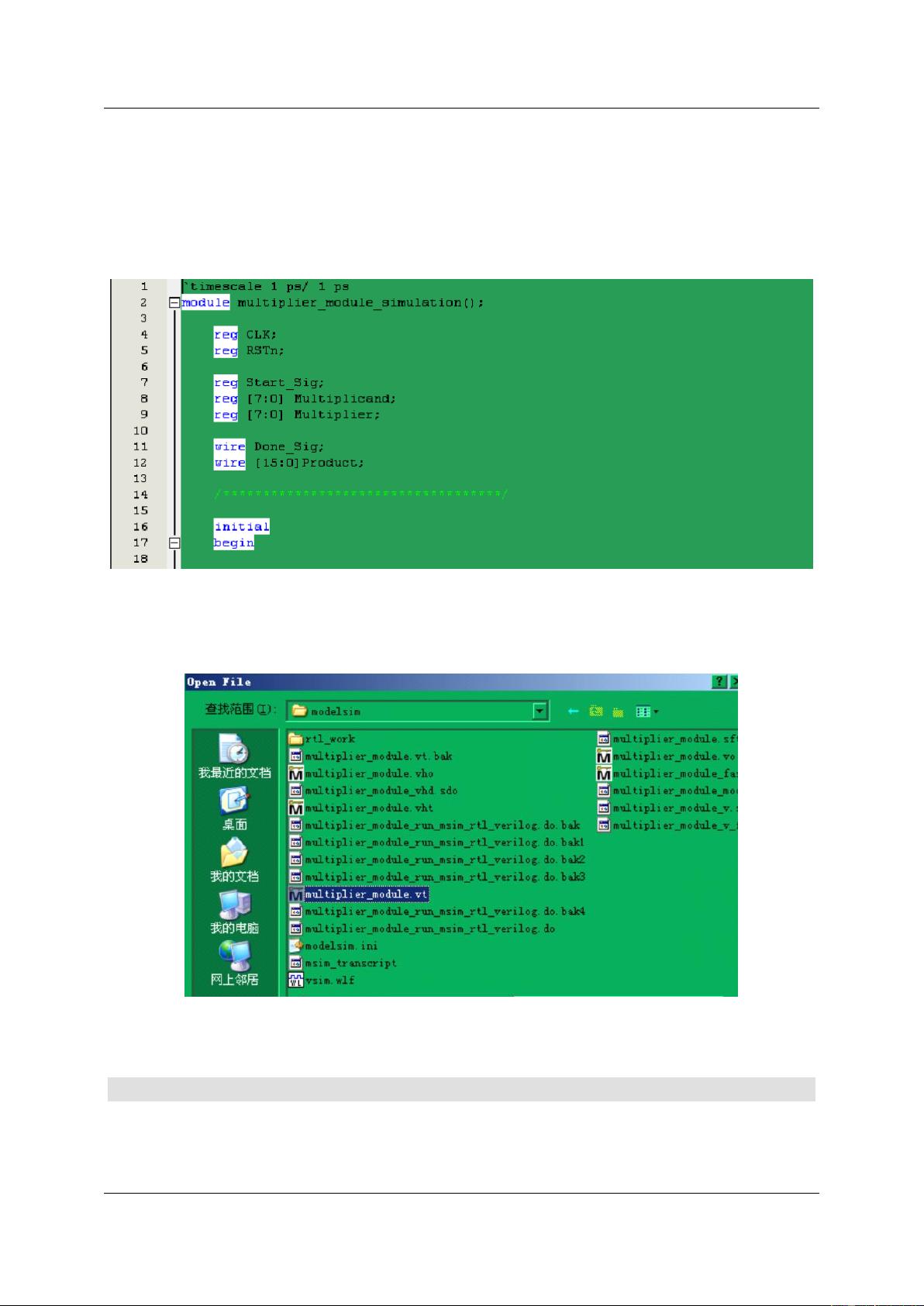

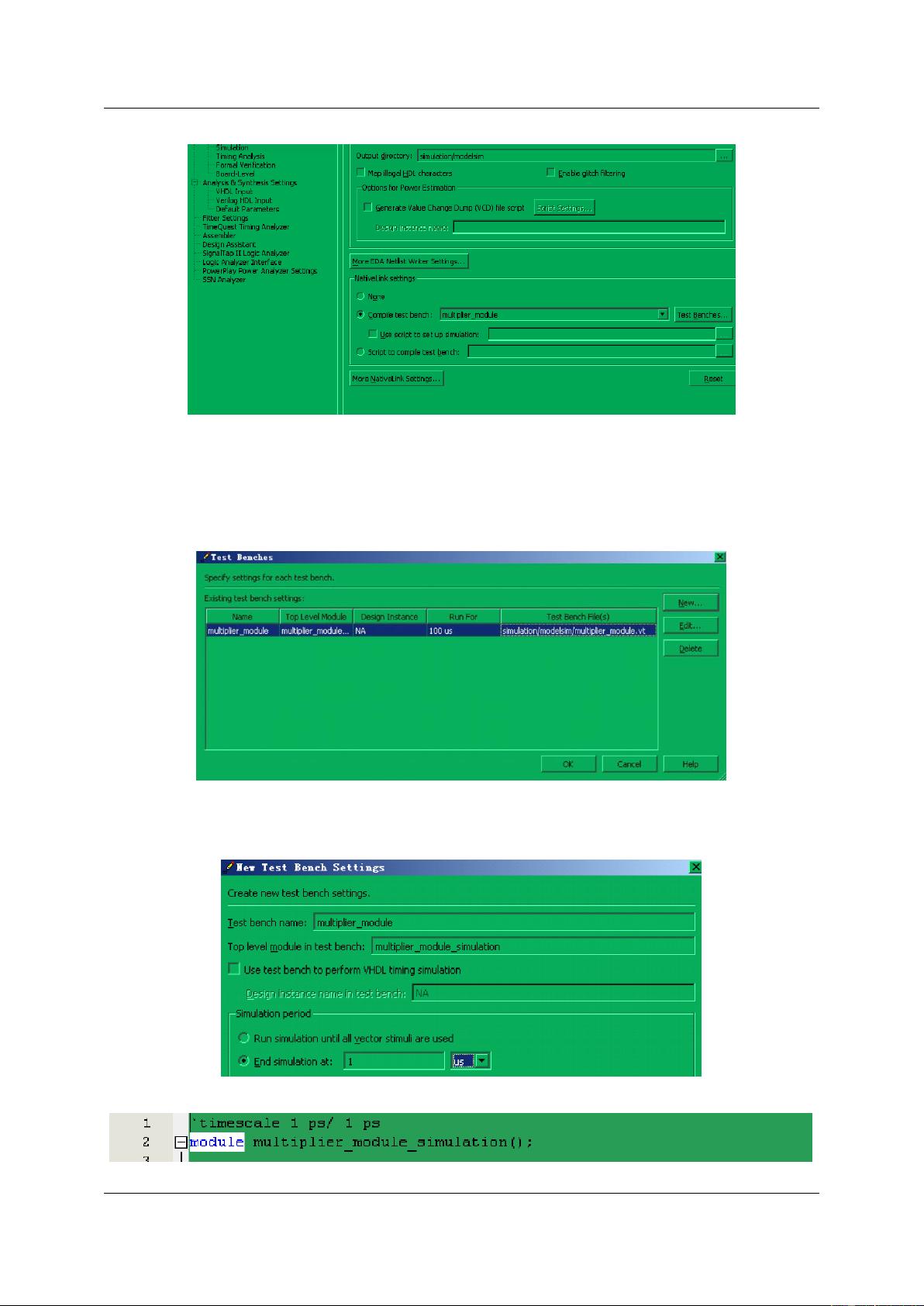

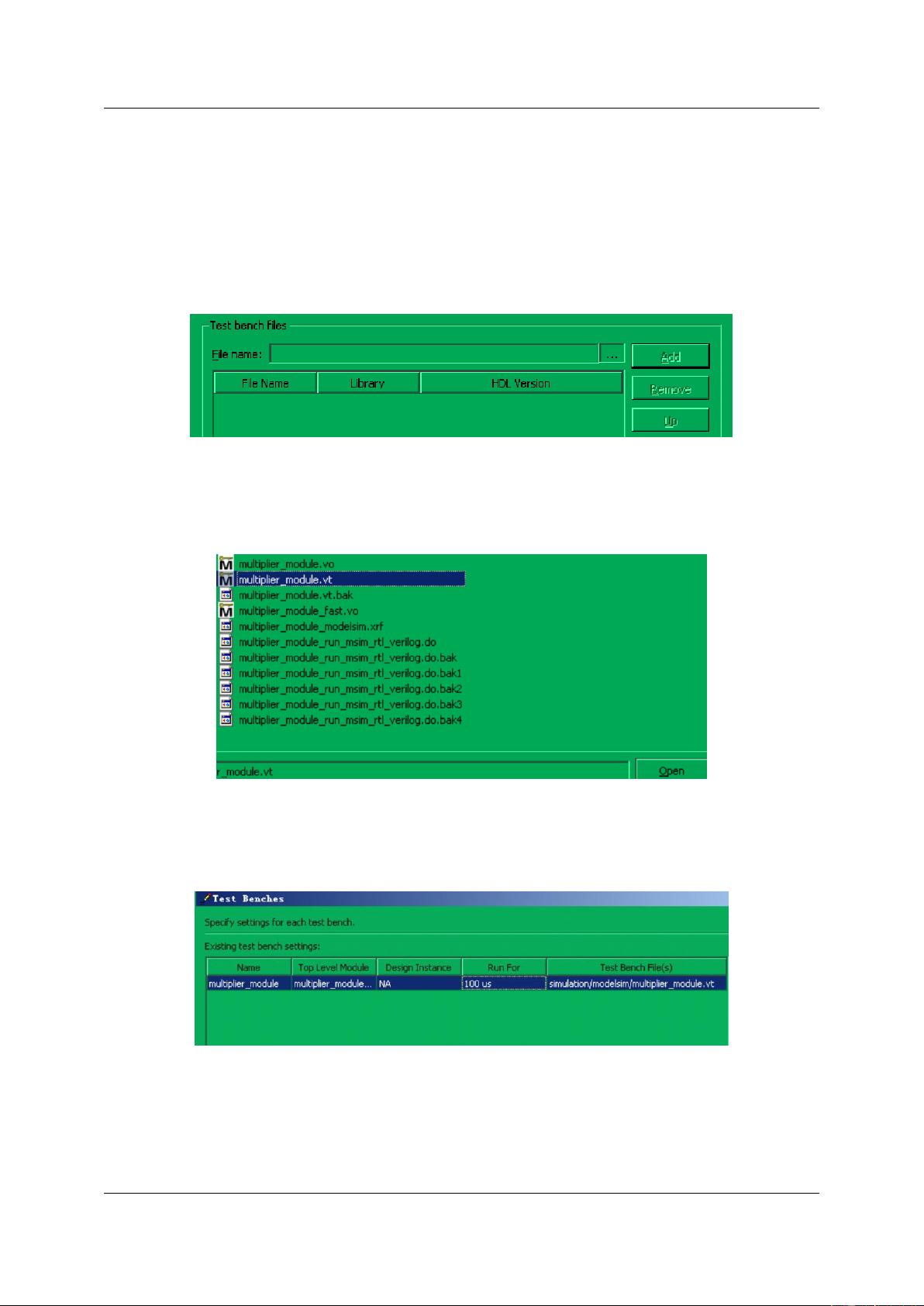

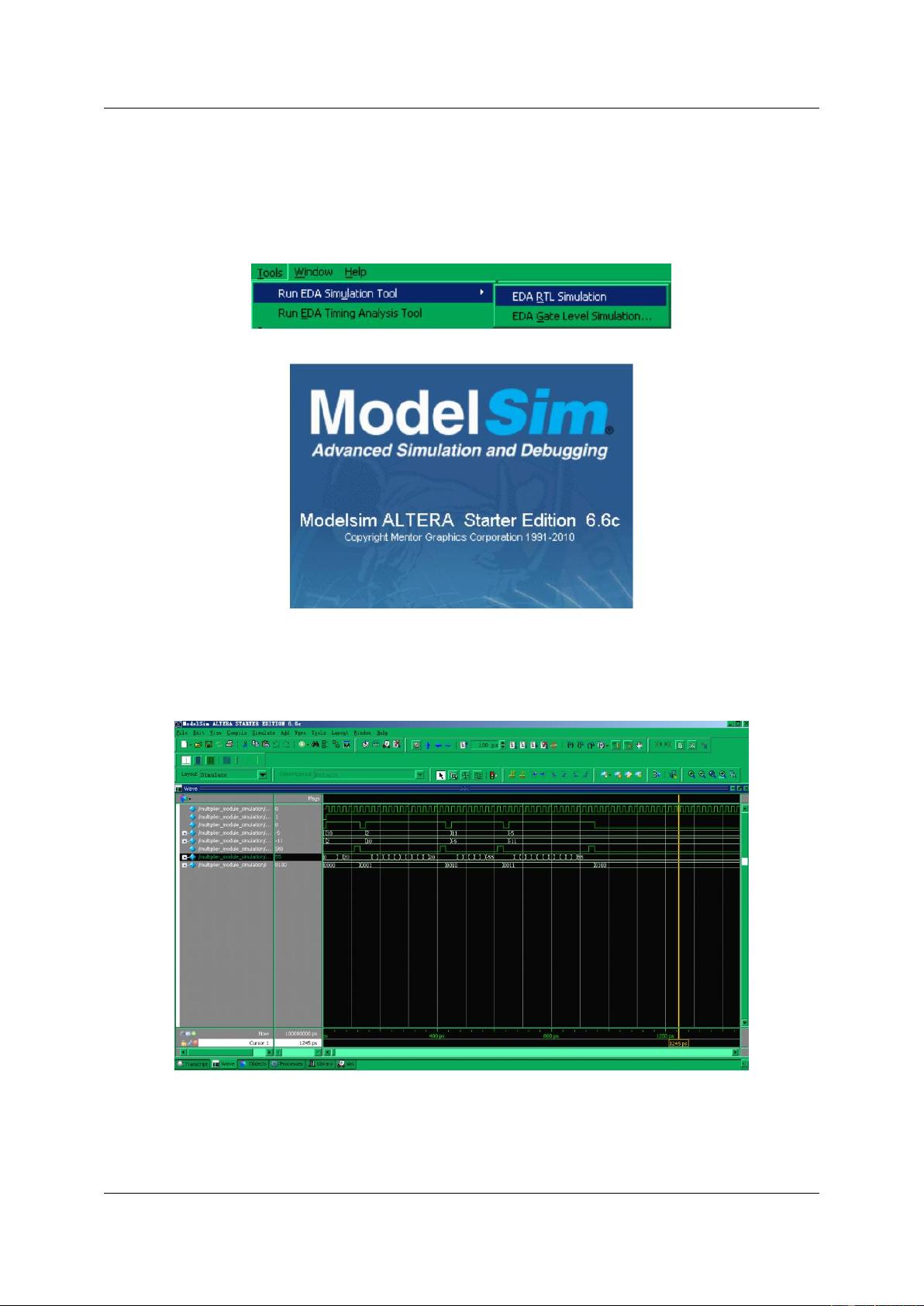

下半部分的“综合和仿真”部分,作者将这两个阶段放在一起学习,综合是将Verilog代码转化为实际电路的过程,而仿真则是验证设计功能是否符合预期的关键步骤。通过综合和仿真的结合,设计师可以更好地评估和优化模块设计,确保在真实硬件上能够正确无误地运行。

《Verilog HDL那些事儿-时序篇》是针对单片机/嵌入式正点原子FPGA设计者的一份宝贵资源,它详尽阐述了时序在Verilog HDL设计中的核心地位,提供了理解和优化数字系统设计的实用工具。通过本书的学习,读者能够提升对Verilog HDL语言的理解,提高设计效率和质量。

2019-03-11 上传

2013-11-28 上传

2011-11-10 上传

2019-07-11 上传

107 浏览量

2018-07-26 上传

2018-11-20 上传

2021-10-04 上传

weixin_38743481

- 粉丝: 696

- 资源: 4万+

最新资源

- ES管理利器:ES Head工具详解

- Layui前端UI框架压缩包:轻量级的Web界面构建利器

- WPF 字体布局问题解决方法与应用案例

- 响应式网页布局教程:CSS实现全平台适配

- Windows平台Elasticsearch 8.10.2版发布

- ICEY开源小程序:定时显示极限值提醒

- MATLAB条形图绘制指南:从入门到进阶技巧全解析

- WPF实现任务管理器进程分组逻辑教程解析

- C#编程实现显卡硬件信息的获取方法

- 前端世界核心-HTML+CSS+JS团队服务网页模板开发

- 精选SQL面试题大汇总

- Nacos Server 1.2.1在Linux系统的安装包介绍

- 易语言MySQL支持库3.0#0版全新升级与使用指南

- 快乐足球响应式网页模板:前端开发全技能秘籍

- OpenEuler4.19内核发布:国产操作系统的里程碑

- Boyue Zheng的LeetCode Python解答集