TOMATO LSI Inc. 18

PRELIMINARY Ver 0.3

128RGB x 160 Dot 1 Chip Driver with RAM and Power circuit for 65KColors TFT-LCD

(Dithering 260K Colors)

TL1771

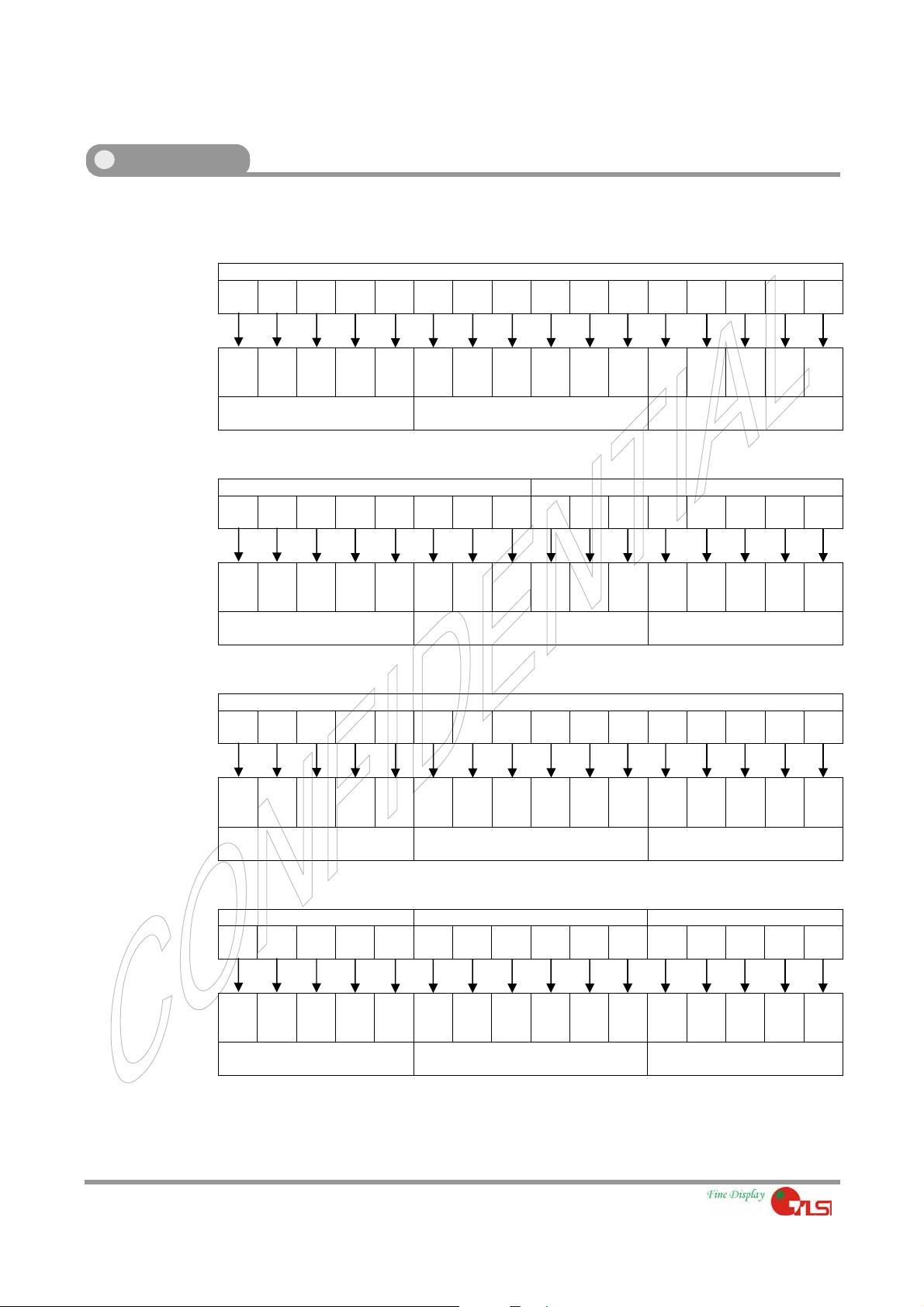

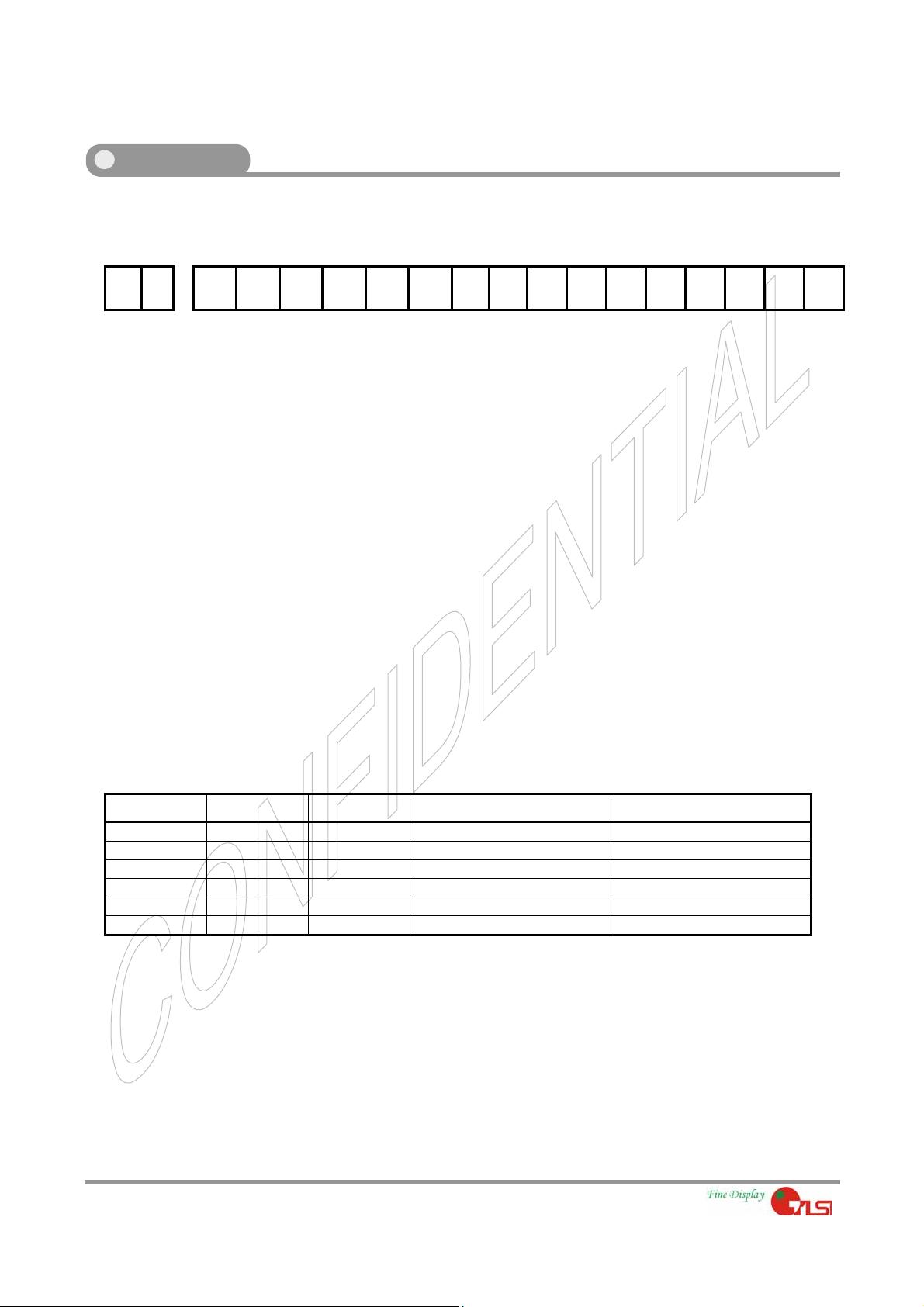

Instruction Table

Upper Code Lower Code

Reg

No.

Register Name

R/

W

R

S

IB15 IB14 IB13 IB12 IB11 IB10 IB9 IB8 IB7 IB6 IB5 IB4 IB3 IB2 IB1 IB0

IR

Index W 0 * * * * * * * * * ID6 ID5 ID4 ID3 ID2 ID1 ID0

SR

Status read R 0 L7 L6 L5 L4 L3 L2 L1 L0 0 0 0 0 0 0 0 0

EXT OSC

00h

Start power W 1 0 0 0 0 0 0 0 0 0 0 0 0 0 0

( 0 )

( 1 )

EPL SM GS SS NL3 NL2 NL1 NL0

01h

Driver output control W 1 0 0 0 0

( 0 ) ( 0 ) ( 0 ) ( 0 )

0 0 0 0

( 1 ) ( 1 ) ( 0 ) ( 0 )

F/L

02h

LCD driving-waveform

control

W 1 0 0 0 0 0 0

( 0 )

0 0 0 0 0 0 0 0 0

DIT BGR I/D1 I/D0 AM

03h

Entry mode W 1 0 0

( 0 ) ( 0 )

0 0 0 0 0 0

( 1 ) ( 1 ) ( 0 )

0 0 0

PT1 PT0 SPT GON DTE CL REV D1 D0

07h

Display control 1 W 1 0 0 0

( 0 ) ( 0 )

0 0

( 0 )

0 0

( 0 ) ( 0 ) ( 0 ) ( 0 ) ( 0 ) ( 0 )

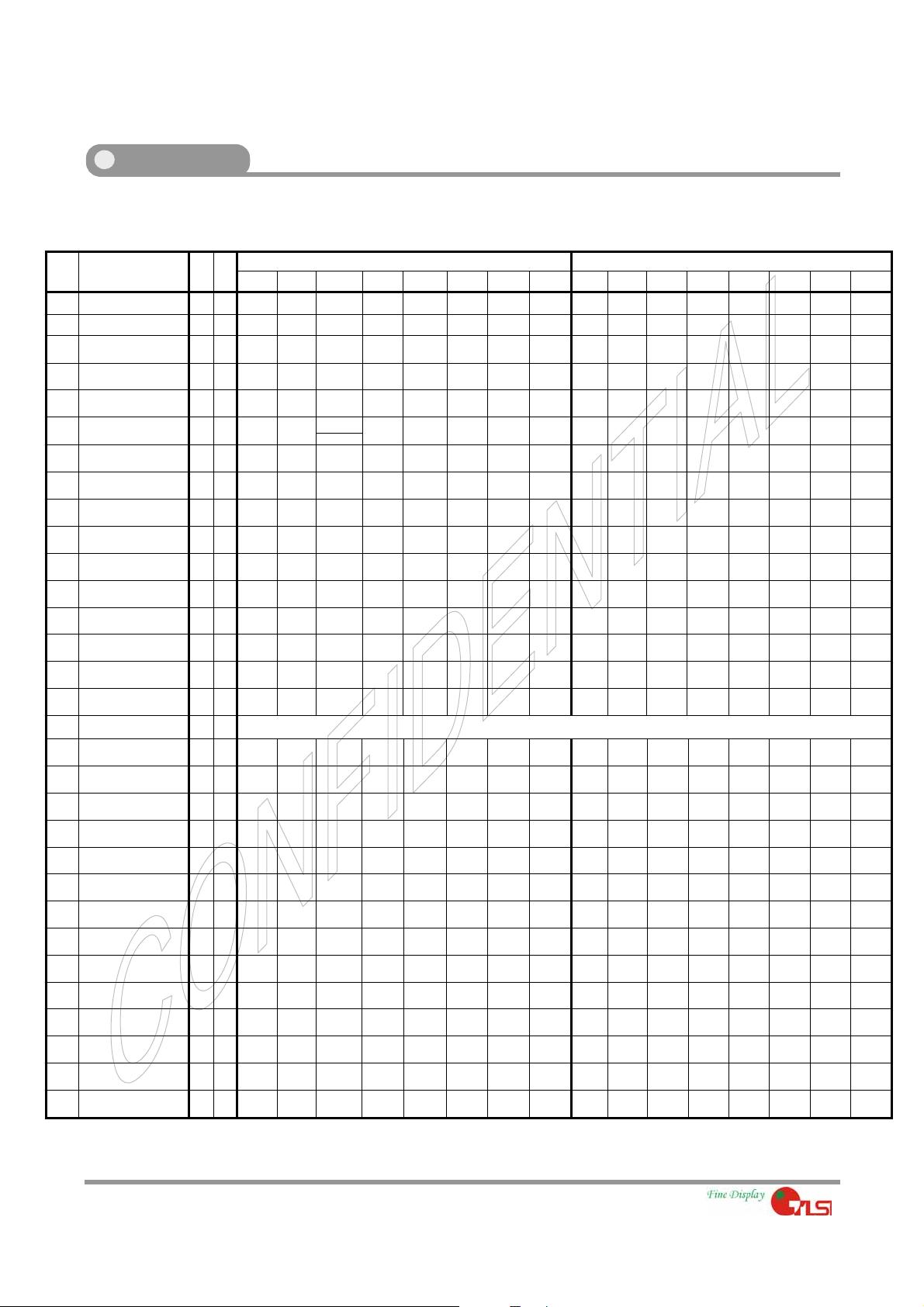

FP3 FP2 FP1 FP0 BP3 BP2 BP1 BP0

08h

Display control 2 W 1 0 0 0 0

( 0 ) ( 1 ) ( 0 ) ( 1 )

0 0 0 0

( 0 ) ( 0 ) ( 1 ) ( 1 )

DIV1 DIV0 RTN3 RTN2 RTN1 RTN0

0Bh

Frame cycle control W 1 0 0 0 0 0 0

( 0 ) ( 0 )

0 0 0 0

( 0 ) ( 0 ) ( 0 ) ( 0 )

RM DM1 DM0 RIM

0Ch

External display interface

control

W 1 0 0 0 0 0 0 0

( 0 )

0 0

( 0 ) ( 0 )

0 0 0

( 0 )

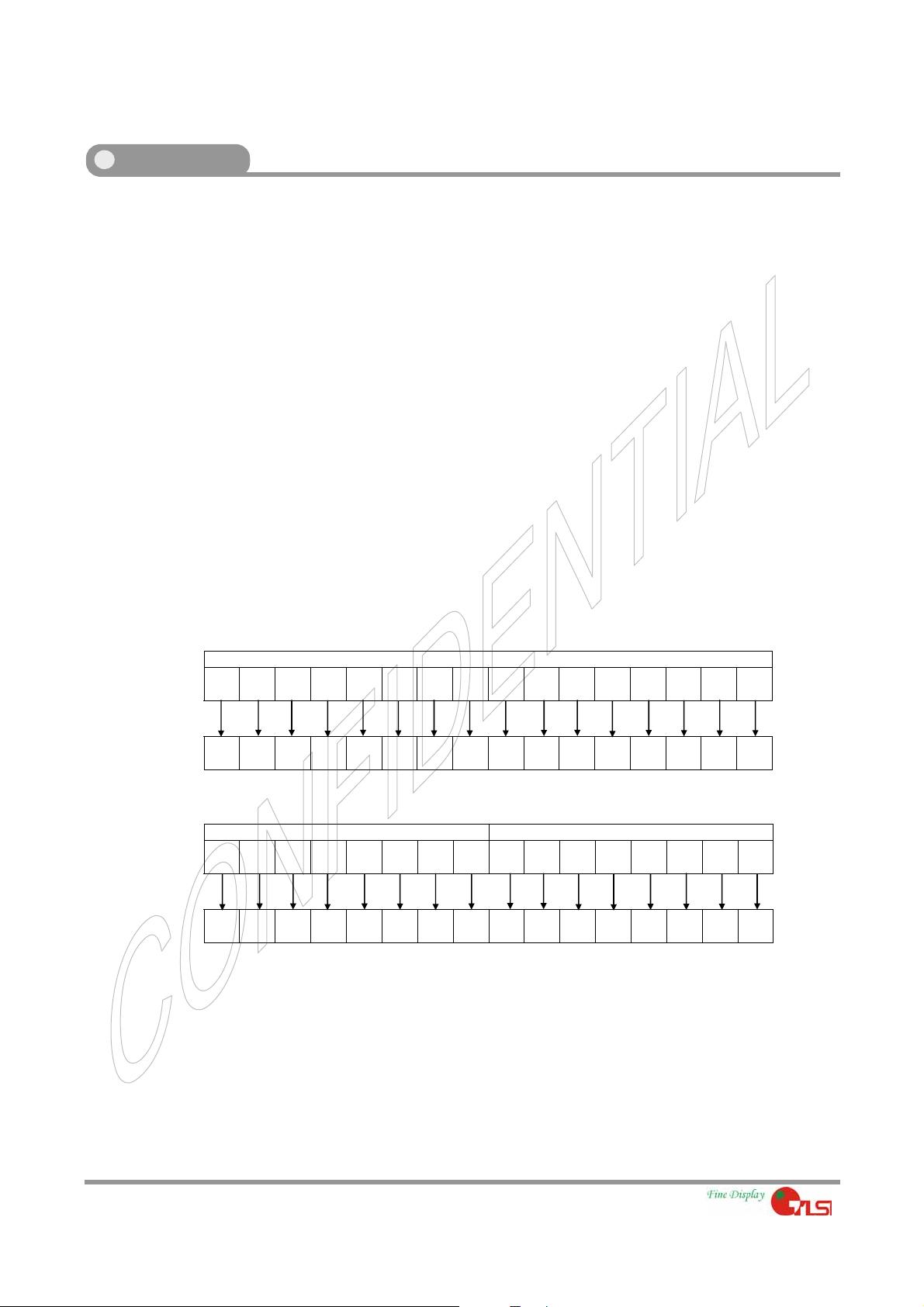

SAP2 SAP1 SAP0 BT2 BT1 BT0 DC2 DC1 DC0 AP2 AP1 AP0 SLP STB

10h

Power control 1 W 1 0 0

( 0 ) ( 0 ) ( 0 ) ( 0 ) ( 0 ) ( 0 ) ( 0 ) ( 0 ) ( 0 ) ( 0 ) ( 0 ) ( 0 ) ( 0 ) ( 0 )

VRN14 VRN13 VRN12 VRN11 VRN10 VRP14 VRP13 VRP12 VRP11 VRP10

11h

Power control 2 W 1 0 0 0

( 0 ) ( 0 ) ( 0 ) ( 0 ) ( 0 )

0 0 0

( 0 ) ( 0 ) ( 0 ) ( 0 ) ( 0 )

VC2 VC1 VC0

12h

Power control 3 W 1 0 0 0 0 0 0 0 0 0 0 0 0 0

( 0 ) ( 0 ) ( 0 )

VCMR PON VRH3 VRH2 VRH1 VRH0

13h

Power control 4 W 1 0 0 0 0

( 0 )

0 0 0 0 0 0

( 0 ) ( 0 ) ( 0 ) ( 0 ) ( 0 )

VCOMG VDV4 VDV3 VDV2 VDV1 VDV0 VCM4 VCM3 VCM2 VCM1 VCM0

14h

Power control 5 W 1 0 0

( 0 ) ( 0 ) ( 0 ) ( 0 ) ( 0 ) ( 0 )

0 0 0

( 0 ) ( 0 ) ( 0 ) ( 0 ) ( 0 )

AD15 AD14 AD13 AD12 AD11 AD10 AD9 AD8 AD7 AD6 AD5 AD4 AD3 AD2 AD1 AD0

21h

RAM address register W 1

( 0 ) ( 0 ) ( 0 ) ( 0 ) ( 0 ) ( 0 ) ( 0 ) ( 0 ) ( 0 ) ( 0 ) ( 0 ) ( 0 ) ( 0 ) ( 0 ) ( 0 ) ( 0 )

22h

RAM data write / read W 1 Write Data to RAM (WD15 -0) / Read data from RAM (RD15-0)

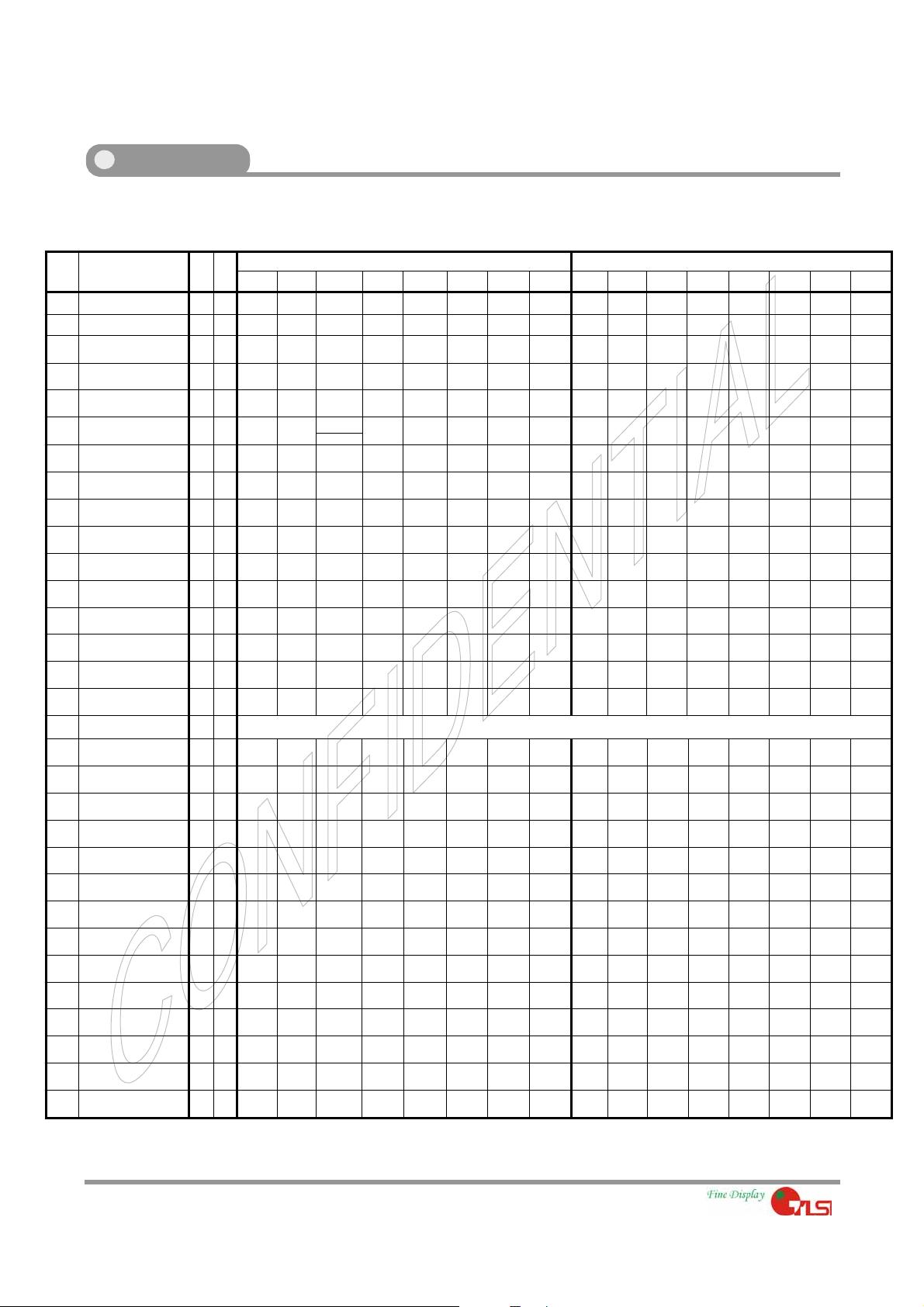

PKP12 PKP11 PKP10 PKP02 PKP01 PKP00

30h

Gamma control (1) W 1 0 0 0 0 0

( 0 ) ( 0 ) ( 0 )

0 0 0 0 0

( 0 ) ( 0 ) ( 0 )

PKP32 PKP31 PKP30 PKP22 PKP21 PKP20

31h

Gamma control (2) W 1 0 0 0 0 0

( 0 ) ( 0 ) ( 0 )

0 0 0 0 0

( 0 ) ( 0 ) ( 0 )

PKP52 PKP51 PKP50 PKP42 PKP41 PKP40

32h

Gamma control (3) W 1 0 0 0 0 0

( 0 ) ( 0 ) ( 0 )

0 0 0 0 0

( 0 ) ( 0 ) ( 0 )

PRP12 PRP11 PRP10 PRP02 PRP01 PRP00

33h

Gamma control (4) W 1 0 0 0 0 0

( 0 ) ( 0 ) ( 0 )

0 0 0 0 0

( 0 ) ( 0 ) ( 0 )

PKN12 PKN11 PKN10 PKN02 PKN01 PKN00

34h

Gamma control (5) W 1 0 0 0 0 0

( 0 ) ( 0 ) ( 0 )

0 0 0 0 0

( 0 ) ( 0 ) ( 0 )

PKN32 PKN31 PKN30 PKN22 PKN21 PKN20

35h

Gamma control (6) W 1 0 0 0 0 0

( 0 ) ( 0 ) ( 0 )

0 0 0 0 0

( 0 ) ( 0 ) ( 0 )

PKN52 PKN51 PKN50 PKN42 PKN41 PKN40

36h

Gamma control (7) W 1 0 0 0 0 0

( 0 ) ( 0 ) ( 0 )

0 0 0 0 0

( 0 ) ( 0 ) ( 0 )

PRN12 PRN11 PRN10 PRN02 PRN01 PRN00

37h

Gamma control (8) W 1 0 0 0 0 0

( 0 ) ( 0 ) ( 0 )

0 0 0 0 0

( 0 ) ( 0 ) ( 0 )

VRN04 VRN03 VRN02 VRN01 VRN00 VRP04 VRP03 VRP02 VRP01 VRP00

38h

Power control 6 W 1 0 0 0

( 0 ) ( 0 ) ( 0 ) ( 0 ) ( 0 )

0 0 0

( 0 ) ( 0 ) ( 0 ) ( 0 ) ( 0 )

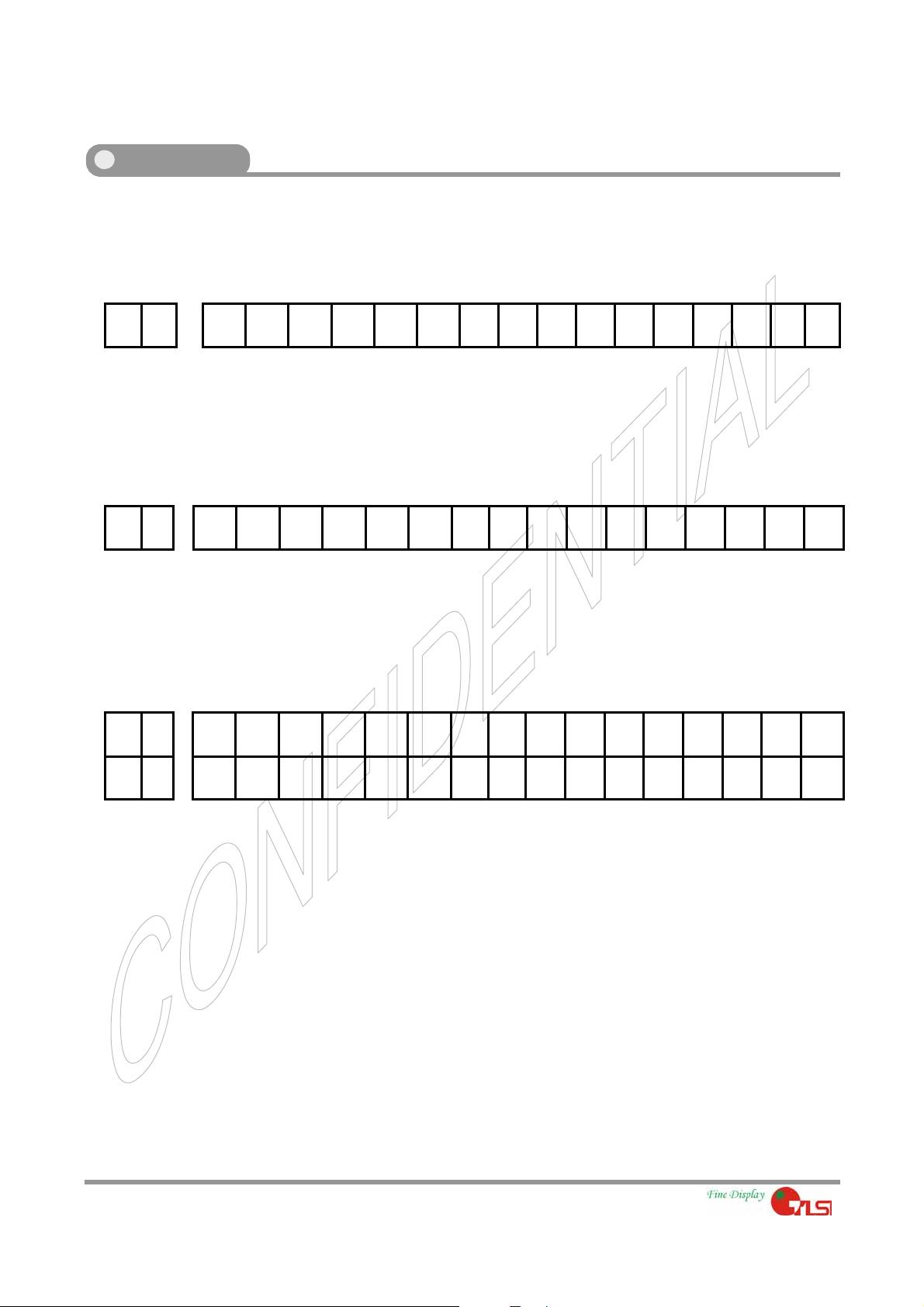

SCN4 SCN3 SCN2 SCN1 SCN0

40h

Gate scan position register W 1 0 0 0 0 0 0 0 0 0 0 0

( 0 ) ( 0 ) ( 0 ) ( 0 ) ( 0 )

SE17 SE16 SE15 SE14 SE13 SE12 SE11 SE10 SS17 SS16 SS15 SS14 SS13 SS12 SS11 SS10

42h

1’st screen driving position W 1

( 1 ) ( 0 ) ( 0 ) ( 1 ) ( 1 ) ( 1 ) ( 1 ) ( 1 ) ( 0 ) ( 0 ) ( 0 ) ( 0 ) ( 0 ) ( 0 ) ( 0 ) ( 0 )

SE27 SE26 SE25 SE24 SE23 SE22 SE21 SE20 SS27 SS26 SS25 SS24 SS23 SS22 SS21 SS20

43h

2’nd

screen driving position W 1

( 1 ) ( 0 ) ( 0 ) ( 1 ) ( 1 ) ( 1 ) ( 1 ) ( 1 ) ( 0 ) ( 0 ) ( 0 ) ( 0 ) ( 0 ) ( 0 ) ( 0 ) ( 0 )

HEA7 HEA6 HEA5 HEA4 HEA3 HEA2 HEA1 HEA0 HSA7 HSA6 HSA5 HSA4 HSA3 HSA2 HSA1 HSA0

44h

Horizontal window address W 1

( 0 ) ( 1 ) ( 1 ) ( 1 ) ( 1 ) ( 1 ) ( 1 ) ( 1 ) ( 0 ) ( 0 ) ( 0 ) ( 0 ) ( 0 ) ( 0 ) ( 0 ) ( 0 )

VEA7 VEA6 VEA5 VEA4 VEA3 VEA2 VEA1 VEA0 VSA7 VSA7 VSA5 VSA4 VSA3 VSA2 VSA1 VSA0

45h

Vertical window address W 1

( 1 ) ( 0 ) ( 0 ) ( 1 ) ( 1 ) ( 1 ) ( 1 ) ( 1 ) ( 0 ) ( 0 ) ( 0 ) ( 0 ) ( 0 ) ( 0 ) ( 0 ) ( 0 )

Note 1) Do not access to the setting-disabled indexes.