同步设计与时钟同步:RTL硬件设计解析

需积分: 7 44 浏览量

更新于2024-07-27

收藏 468KB PDF 举报

"时钟与同步-RTL硬件设计"

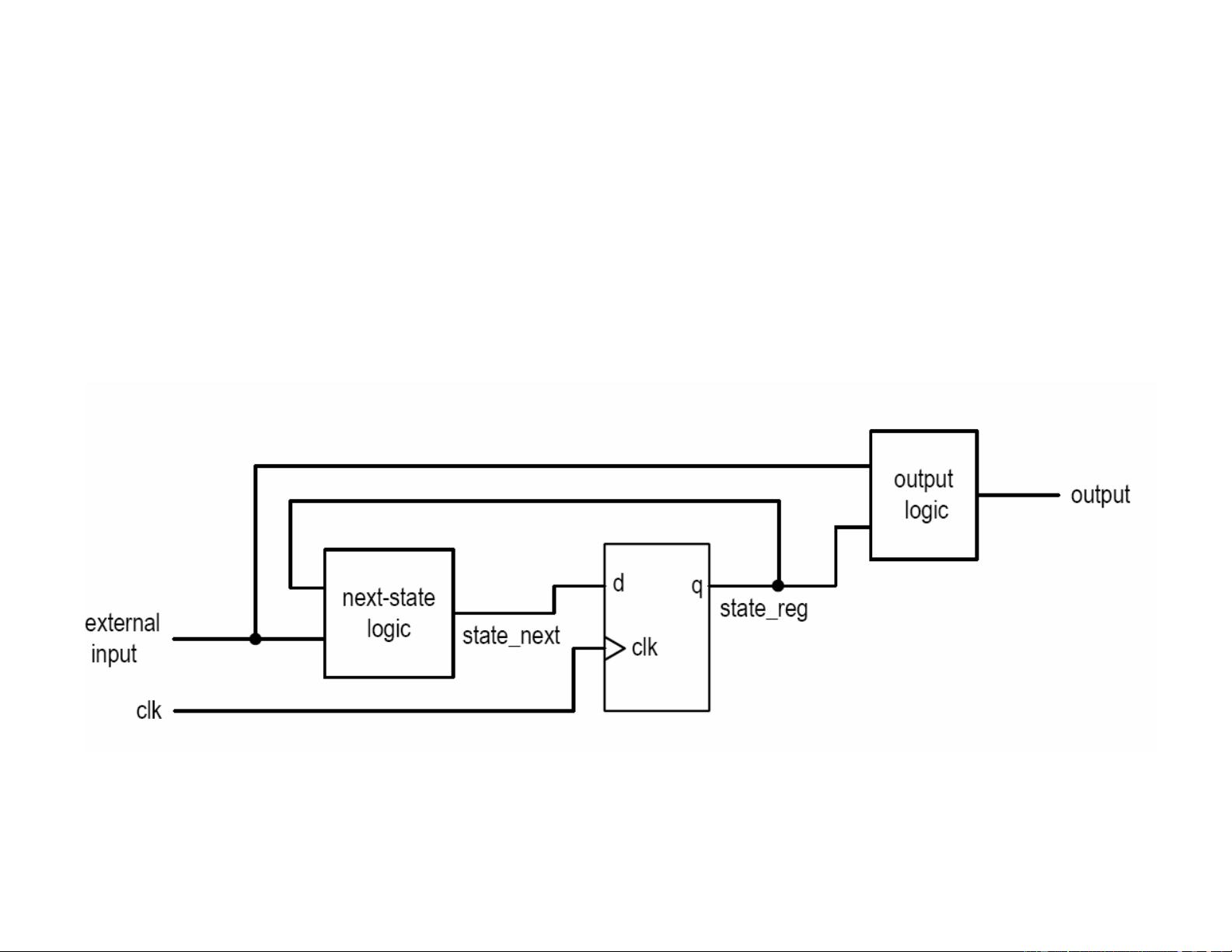

在数字电路设计中,尤其是在RTL(寄存器传输级)硬件设计中,时钟和同步扮演着至关重要的角色。本章节将探讨为什么需要采用同步设计,时钟分布网络及时钟偏移问题,多时钟系统, metastability 和同步失败,以及同步器的设计。

1. 为什么需要同步?

同步设计是数字系统的基础,它确保了系统中所有组件在同一时刻进行操作,从而避免了数据不一致和竞争条件。在同步系统中,信号的变化是由时钟边沿触发的,这样可以简化时序分析,提高系统的稳定性和可靠性。在组合逻辑电路中,时钟同步可以消除静态和动态定时危害,这些危害可能在信号的暂态期间引起错误的脉冲或毛刺。

2. 时钟分布网络和时钟偏移

时钟信号需要在整个系统中均匀地分发,以确保所有组件在同一时刻开始操作。然而,由于布线延迟,时钟信号到达不同位置的时间可能会有所差异,这称为时钟偏移或时钟 skew。时钟偏移可能导致数据传输中的错误,因此需要通过精心设计的时钟树结构和补偿技术来尽量减少这种效应。

3. 多时钟系统

在复杂的数字系统中,常常需要使用多个不同的时钟域,每个域可能有其独特的时钟频率和相位。跨时钟域的数据传输需要额外的同步机制,以确保数据在正确的时间被正确的时钟捕获,否则可能会导致 metastability 或同步失败。

4. Meta-stability 和同步失败

Meta-stability 是指数字信号在两个时钟域之间传输时可能处于不确定状态,即既非稳定状态也非非稳定状态。如果未正确处理,meta-stability 可能会导致数据错误。同步失败通常发生在接收端的寄存器未能在时钟边缘到来之前稳定,这可能导致数据丢失或损坏。

5. 同步器

为了克服 metastability 和同步失败,通常会使用同步器设计。同步器通常由多个 flip-flops 或寄存器组成,形成一个级联结构,用以捕捉和稳定跨时钟域的数据。同步器的设计必须考虑到潜在的延迟和功耗,以确保在保证系统性能的同时,提供足够的同步裕量。

时钟和同步在RTL硬件设计中至关重要,它们不仅决定了系统的时序行为,还直接影响着系统性能、稳定性和可靠性。理解和掌握这些概念对于高效、无误的数字系统设计是必不可少的。

2011-03-18 上传

2021-04-22 上传

2021-04-22 上传

2021-04-22 上传

2021-05-06 上传

2021-05-16 上传

2021-05-10 上传

2021-06-08 上传

ckairking

- 粉丝: 0

- 资源: 2

最新资源

- Cucumber-JVM模板项目快速入门教程

- ECharts打造公司组织架构可视化展示

- DC Water Alerts 数据开放平台介绍

- 图形化编程打造智能家居控制系统

- 个人网站构建:使用CSS实现风格化布局

- 使用CANBUS控制LED灯柱颜色的Matlab代码实现

- ACTCMS管理系统安装与更新教程

- 快速查看IP地址及地理位置信息的View My IP插件

- Pandas库助力数据分析与编程效率提升

- Python实现k均值聚类音乐数据可视化分析

- formdotcom打造高效网络表单解决方案

- 仿京东套餐购买列表源码DYCPackage解析

- 开源管理工具orgParty:面向PartySur的多功能应用程序

- Flutter时间跟踪应用Time_tracker入门教程

- AngularJS实现自定义滑动项目及动作指南

- 掌握C++编译时打印:compile-time-printer的使用与原理