FPGA初学者指南:逻辑设计与开发流程

需积分: 17 113 浏览量

更新于2024-07-29

收藏 672KB PDF 举报

"FPGA入门教程,涵盖了数字电路设计基础,FPGA简介,开发流程,RTL设计,QuartusⅡ工具使用以及ModelSim和Testbench的验证方法"

在电子工程领域,FPGA(Field-Programmable Gate Array)是一种可编程逻辑器件,允许工程师根据需求配置硬件逻辑功能。本入门教程旨在帮助初学者逐步了解并掌握FPGA的设计与应用。

1. 数字电路设计入门

数字电路设计是FPGA学习的基础,主要涉及逻辑门电路如与门、或门、非门、异或门等。组合逻辑电路是无记忆功能的电路,其输出仅依赖于当前的输入,而时序逻辑电路则包含存储元件(如触发器),输出不仅与输入有关,还取决于前一状态。时钟是区分两者的关键,时序逻辑电路通常由时钟边沿触发。

1.1 组合逻辑电路

组合逻辑电路不包含内部存储,由基本逻辑门构成,通过这些门的连接实现复杂的逻辑函数。例如,一个简单的逻辑电路可能由多个输入A, B, C等通过逻辑门运算得到单一输出G。

1.2 时序逻辑电路

时序逻辑电路包括触发器,如D型触发器,其状态在每个时钟周期变化。触发器的特性如建立时间(tsu)和保持时间(thold)是确保正确操作的关键,它们规定了输入数据必须在时钟沿前后保持稳定的时间。时序逻辑电路的例子如时钟分频器,可以将输入时钟频率降低为预设比例。

2. FPGA简介

FPGA是由可配置的逻辑块、输入/输出单元、布线资源等组成的芯片,允许用户根据设计需求进行定制。相比于ASIC(Application-Specific Integrated Circuit),FPGA提供了更高的灵活性,适合原型验证和小批量生产。

3. FPGA开发流程

FPGA开发通常包括以下步骤:需求分析、逻辑设计(RTL级描述)、逻辑综合、布局布线、仿真验证、硬件调试和系统集成。

4. RTL设计

RTL(Register Transfer Level)设计是用硬件描述语言(如VHDL或Verilog)描述数字系统的层次,它描述了数据在寄存器之间的转移以及转换规则。

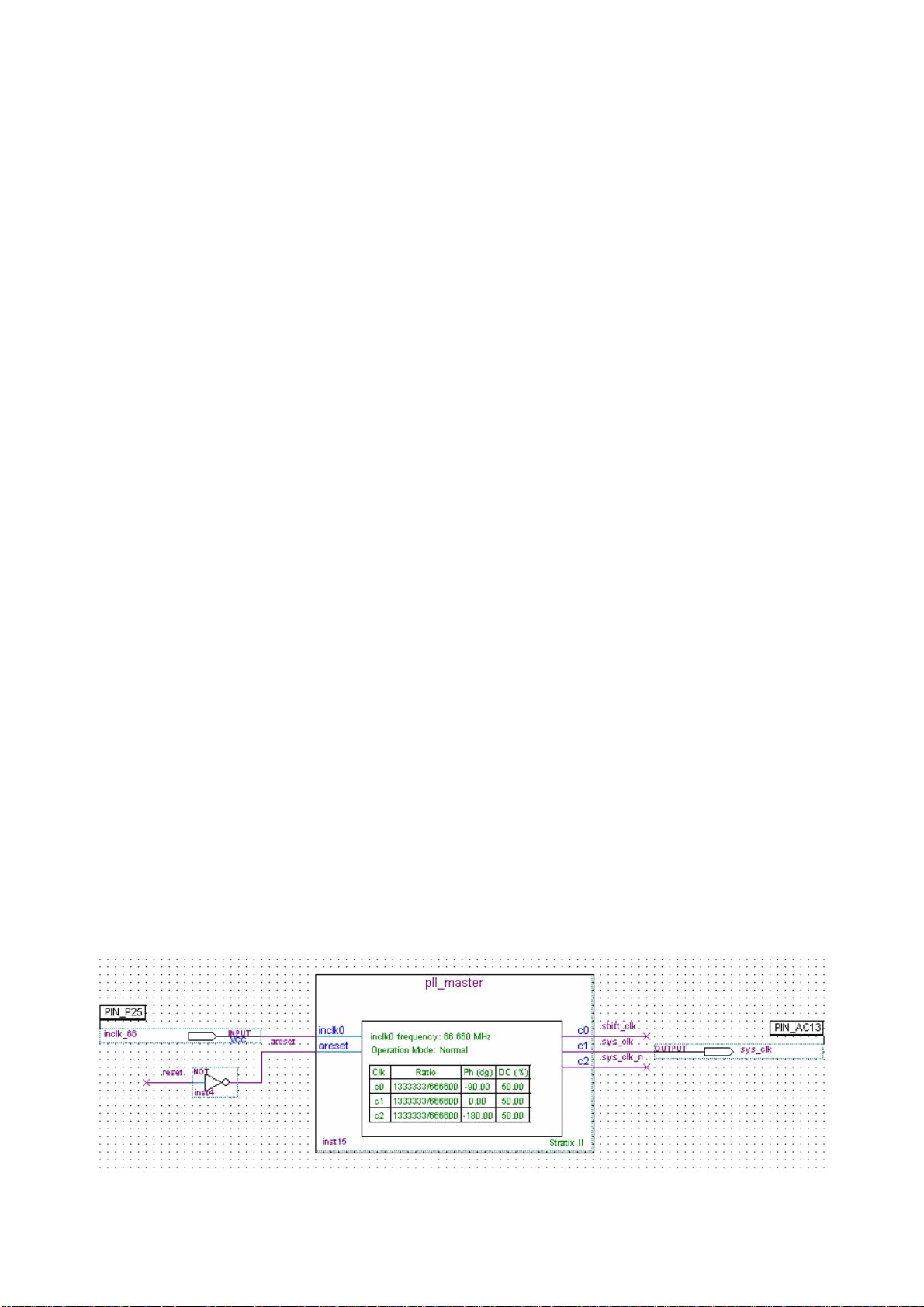

5. QuartusⅡ设计实例

QuartusⅡ是Altera公司(现Intel公司的一部分)的一款FPGA开发工具,支持完整的FPGA设计流程,包括编写代码、编译、仿真、适配和编程下载。

6. ModelSim和Testbench

ModelSim是一款流行的仿真工具,用于验证RTL代码的功能正确性。Testbench是在ModelSim中创建的虚拟环境,模拟真实硬件的输入输出,以测试设计的各个功能。

通过这个入门教程,初学者能够掌握数字电路基础知识,学会使用FPGA开发工具,并掌握基本的FPGA设计方法,为进一步深入学习和实践打下坚实基础。同时,了解不同的电平标准和时序逻辑的特性对于理解FPGA的工作原理至关重要。

2019-02-20 上传

2019-07-28 上传

2024-06-19 上传

2009-01-13 上传

2009-01-09 上传

点击了解资源详情

2010-07-11 上传

zhencchi

- 粉丝: 0

- 资源: 4

最新资源

- Angular程序高效加载与展示海量Excel数据技巧

- Argos客户端开发流程及Vue配置指南

- 基于源码的PHP Webshell审查工具介绍

- Mina任务部署Rpush教程与实践指南

- 密歇根大学主题新标签页壁纸与多功能扩展

- Golang编程入门:基础代码学习教程

- Aplysia吸引子分析MATLAB代码套件解读

- 程序性竞争问题解决实践指南

- lyra: Rust语言实现的特征提取POC功能

- Chrome扩展:NBA全明星新标签壁纸

- 探索通用Lisp用户空间文件系统clufs_0.7

- dheap: Haxe实现的高效D-ary堆算法

- 利用BladeRF实现简易VNA频率响应分析工具

- 深度解析Amazon SQS在C#中的应用实践

- 正义联盟计划管理系统:udemy-heroes-demo-09

- JavaScript语法jsonpointer替代实现介绍