PCIe PCB设计要点与高速信号分析

版权申诉

107 浏览量

更新于2024-09-06

收藏 970KB PDF 举报

"PCB设计---PCIE设计总结.pdf"

在PCB设计中,PCI Express (PCIE) 是一种高速接口标准,广泛应用于服务器和主板上。本设计总结主要聚焦于PCIE的封装形式、速率以及PCB布局和布线的关键要点。

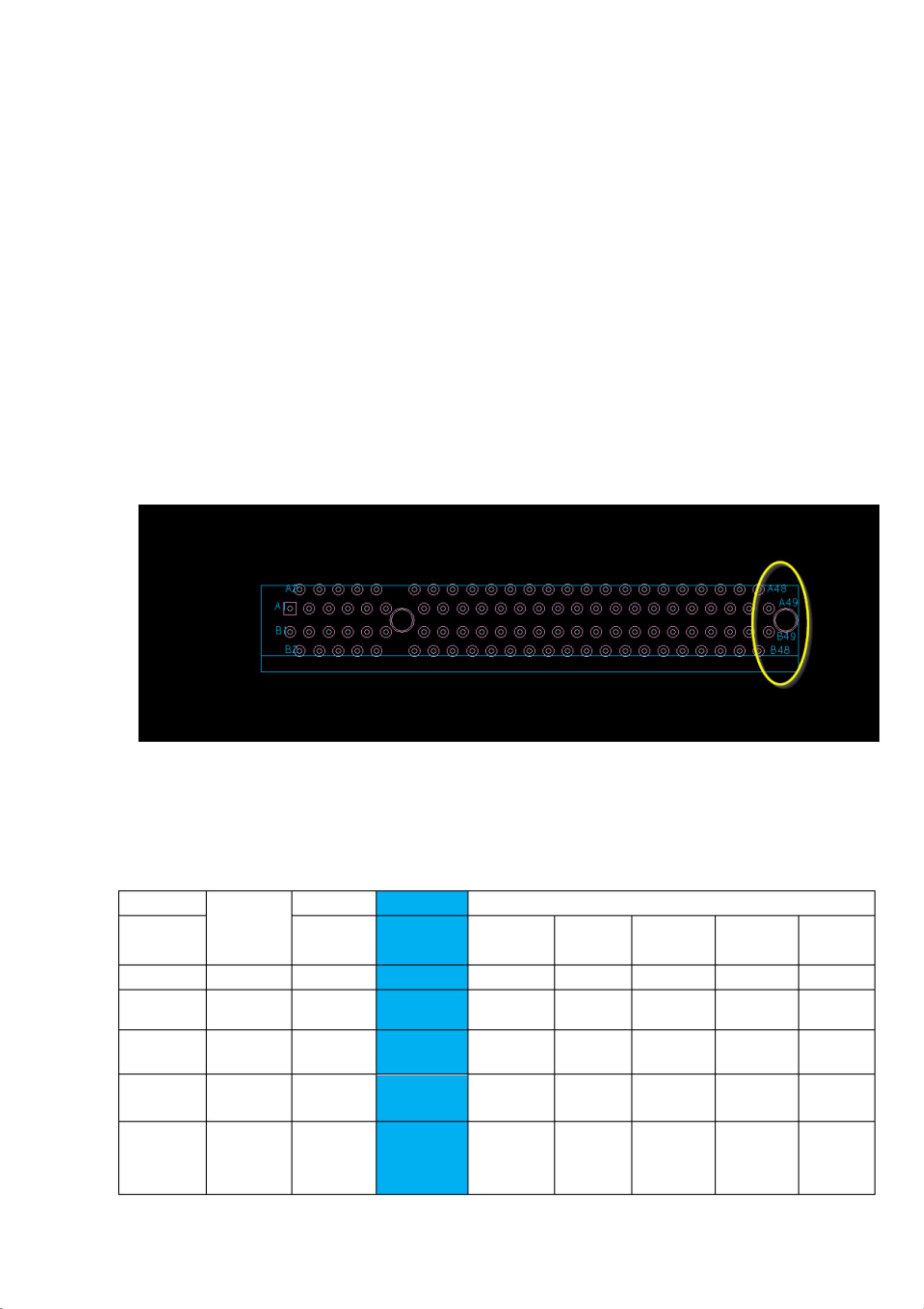

封装方面,PCIE接口有多种规格,包括X1、X4、X8和X16,这些数字代表了lane的数量,每条lane由一对发送和接收的差分信号组成。例如,X1接口包含1条lane,而X16接口则有16条lane。不同封装的管脚数量不同,如X8连接器有49个管脚,其中A32和B32分别代表发送和接收的lane。通过识别管脚号,我们可以确定接口类型。

PCIE的速率随着版本的提升而增加,从最初的PCIE 1.0到最新的PCIE 5.0。每个版本都采用8b/10b或128b/130b编码方式,以提高数据传输的效率和可靠性。例如,PCIE 3.0的单lane传输速率为8.0 GT/s,对应的数据传输速率为7.88 GB/s。PCIE 5.0的单lane速率翻倍至16.0 GT/s,可达到31.5 GB/s的数据传输速度。

在设计PCIE的PCB时,信号完整性和电磁兼容性(SI和EMC)是关键考虑因素。以下是一些布局和布线的建议:

1. 布局:

- AC电容应尽可能靠近接口放置,以减少信号失真。

- 避免Stub,Stub是直角折线或过长的非连续走线,会引入信号反射。如果PCIE接口在TOP层,AC电容应放在BOTTOM层,以消除Stub。

- 底层组件焊盘到接口焊盘的间距至少保持3mm,以适应波峰焊工艺。

2. 布线:

- 阻抗控制是确保信号质量的重要环节,通常选择85Ω或100Ω的阻抗值。

- PCIE走线应尽量在同一层面,避免垂直层间跳线,以减少信号衰减和干扰。

- Stub应尽可能短,因为它们会导致信号反射,影响信号质量。

- 保持适当的线宽和线间距,以满足阻抗匹配和减少串扰。

- 注意信号线的层叠规划,通常将电源和地线安排在信号线两侧,形成良好的屏蔽效果。

在实际设计中,还需要考虑其他因素,如热管理、PCB材料选择、返工友好性等。设计师需要结合仿真工具和实测数据,不断优化设计,以确保PCIE接口在高速运行时的稳定性和可靠性。

2021-11-11 上传

2021-08-17 上传

2020-07-14 上传

2021-07-25 上传

2021-04-26 上传

2019-09-05 上传

2021-01-24 上传

2021-08-11 上传

maodi_lzc

- 粉丝: 1

- 资源: 3万+

最新资源

- 高清艺术文字图标资源,PNG和ICO格式免费下载

- mui框架HTML5应用界面组件使用示例教程

- Vue.js开发利器:chrome-vue-devtools插件解析

- 掌握ElectronBrowserJS:打造跨平台电子应用

- 前端导师教程:构建与部署社交证明页面

- Java多线程与线程安全在断点续传中的实现

- 免Root一键卸载安卓预装应用教程

- 易语言实现高级表格滚动条完美控制技巧

- 超声波测距尺的源码实现

- 数据可视化与交互:构建易用的数据界面

- 实现Discourse外聘回复自动标记的简易插件

- 链表的头插法与尾插法实现及长度计算

- Playwright与Typescript及Mocha集成:自动化UI测试实践指南

- 128x128像素线性工具图标下载集合

- 易语言安装包程序增强版:智能导入与重复库过滤

- 利用AJAX与Spotify API在Google地图中探索世界音乐排行榜