0.6μm工艺下脑电信号专用ASIC设计:高性能与集成优势

需积分: 5 165 浏览量

更新于2024-08-08

收藏 803KB PDF 举报

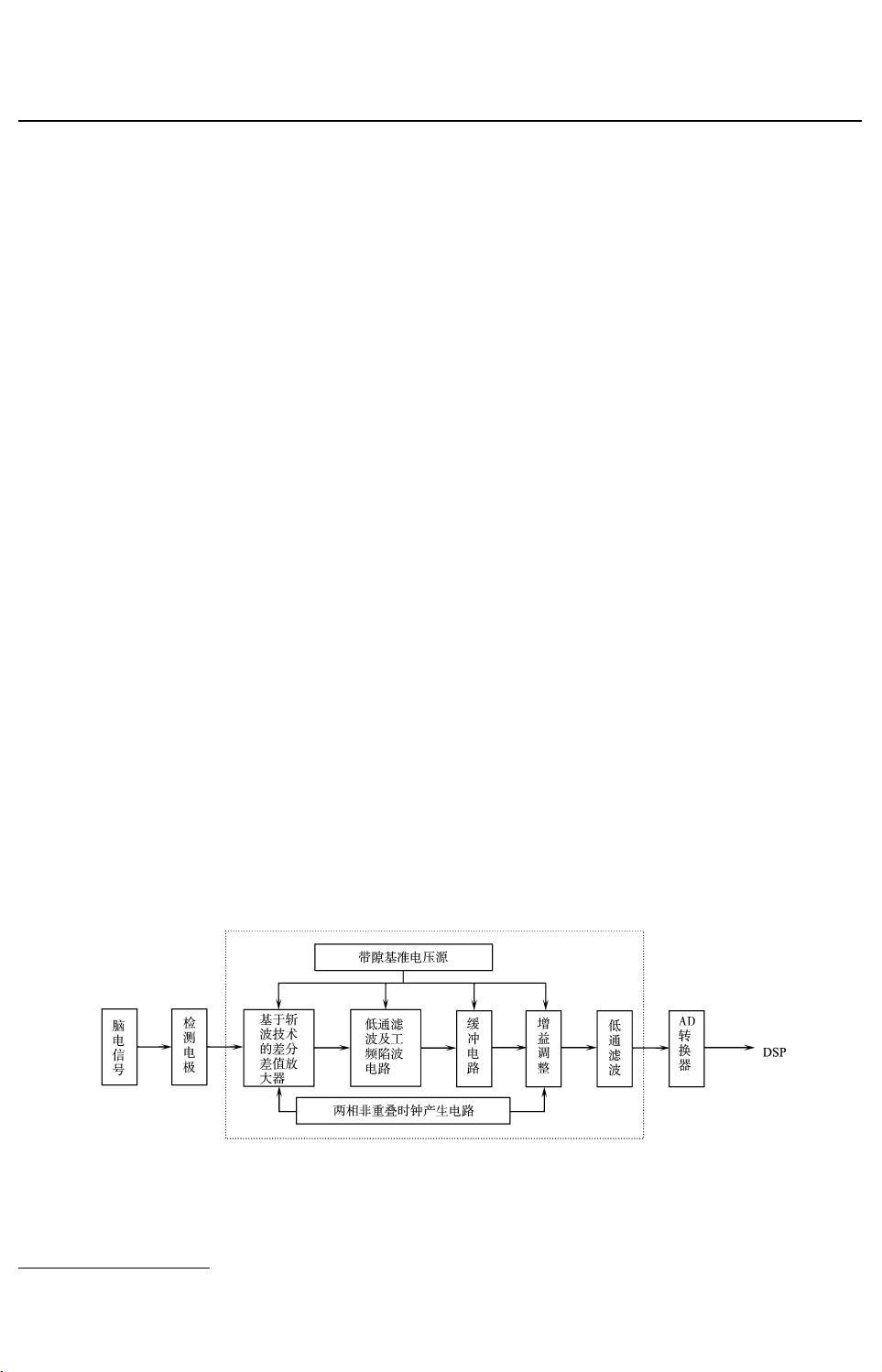

本文主要探讨了"脑电信号检测专用集成电路的设计",采用的是CMOS双层多晶、双层金属以及N阱0.6μm互补金属氧化物半导体工艺。这种ASIC(Application-Specific Integrated Circuit,专用集成电路)系统的核心组成部分包括基于斩波技术的差分差值放大器,用于提高信号处理的精度;跨导运算放大器(OTA)-C低通滤波电路,能够有效去除高频噪声,保留脑电信号的低频成分;增益调整电路,使得系统能够适应不同强度的信号输入;两相非重叠时钟产生电路,确保数据采样和处理的同步;以及带隙电压基准电路,提供稳定的参考电压,确保信号处理的准确性。

在设计上,作者关注到了脑电信号的特性,其信号微弱且易受干扰,通常在5~100μV的范围内,频率范围在0.5~40Hz。因此,电路设计的关键在于如何在有限的芯片空间内实现高信噪比和良好的共模抑制比。通过仿真验证,当输入信号处于-0.862~0.902V范围内,输入和输出呈现良好的线性关系,共模抑制比高达114dB,达到了设计目标,证明了该电路的有效性和可靠性。

文章指出,随着脑机接口技术在军事和医疗等领域的广泛应用,集成化和小型化的脑电信号处理系统变得尤为重要。通过将脑电信号检测电路集成到单个芯片上,可以显著降低能耗,减少设备体积,并简化用户操作。这与SoC(System On a Chip,片上系统)的设计理念相符,即在单一芯片上集成所有必要的功能。

最后,文章详细介绍了系统的架构,特别是模拟信号处理模块的设计,包括带隙基准电路、差分差值放大器、低通滤波器和缓冲电路的集成,以及整个流程从模拟信号到数字信号的转换过程,旨在构建一个高效、紧凑的脑电信号检测平台。

本文的核心知识点集中在脑电信号检测专用集成电路的设计原理、关键技术选择、系统架构以及实际性能评估,展示了在高性能、低功耗芯片上实现脑电信号精确采集和处理的可能性。

2009-09-27 上传

2011-03-04 上传

2020-10-21 上传

2020-08-29 上传

2021-05-18 上传

2021-04-24 上传

2020-10-22 上传

2011-03-04 上传

2021-09-30 上传

weixin_38646634

- 粉丝: 4

- 资源: 910

最新资源

- Angular实现MarcHayek简历展示应用教程

- Crossbow Spot最新更新 - 获取Chrome扩展新闻

- 量子管道网络优化与Python实现

- Debian系统中APT缓存维护工具的使用方法与实践

- Python模块AccessControl的Windows64位安装文件介绍

- 掌握最新*** Fisher资讯,使用Google Chrome扩展

- Ember应用程序开发流程与环境配置指南

- EZPCOpenSDK_v5.1.2_build***版本更新详情

- Postcode-Finder:利用JavaScript和Google Geocode API实现

- AWS商业交易监控器:航线行为分析与营销策略制定

- AccessControl-4.0b6压缩包详细使用教程

- Python编程实践与技巧汇总

- 使用Sikuli和Python打造颜色求解器项目

- .Net基础视频教程:掌握GDI绘图技术

- 深入理解数据结构与JavaScript实践项目

- 双子座在线裁判系统:提高编程竞赛效率