"该资源是2004年12月8日清华大学微电子研究所周润德教授关于《数字大规模集成电路》课程的第8章(2)时序电路的课件,主要讲解了时序电路中的Register和Latch的时序参数、延迟关系以及建立时间(setup time)的概念和重要性。"

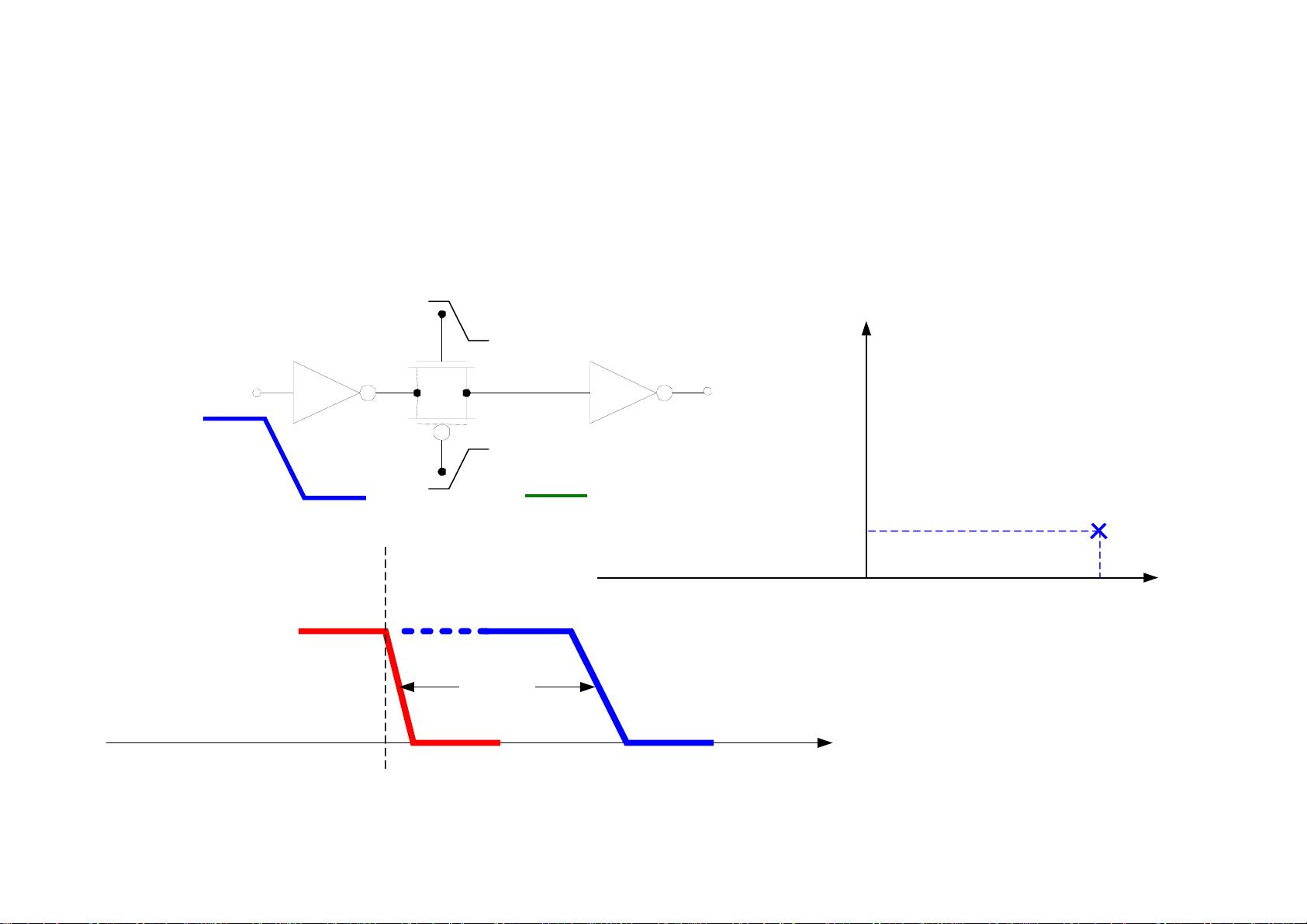

在时序电路设计中,Register和Latch是两种基本的存储单元,它们在数字系统中用于暂存数据。课件中提到了几个关键的时序参数:

1. **tc-q**: 这是数据从输入(D)到输出(Q)的延迟时间,即从时钟边沿触发到数据稳定出现在输出端的时间。

2. **thold**: 时钟到达阈值时间,指时钟信号必须在达到一定阈值之后,Register或Latch才能正确响应。这个时间对确保数据稳定至关重要。

3. **tsu**: 建立时间(setup time),是指数据必须在时钟边沿到来前的一个固定时间内稳定在输入端,以确保在时钟翻转后输出能正确反映出输入值。

4. **td-q**: 对于Latch,这是数据变化到输出变化的时间,不同于Register的tc-q。

5. **PWm**: 对Latch的脉冲宽度要求,确保时钟脉冲宽度足够长,使得Latch能正确捕获数据。

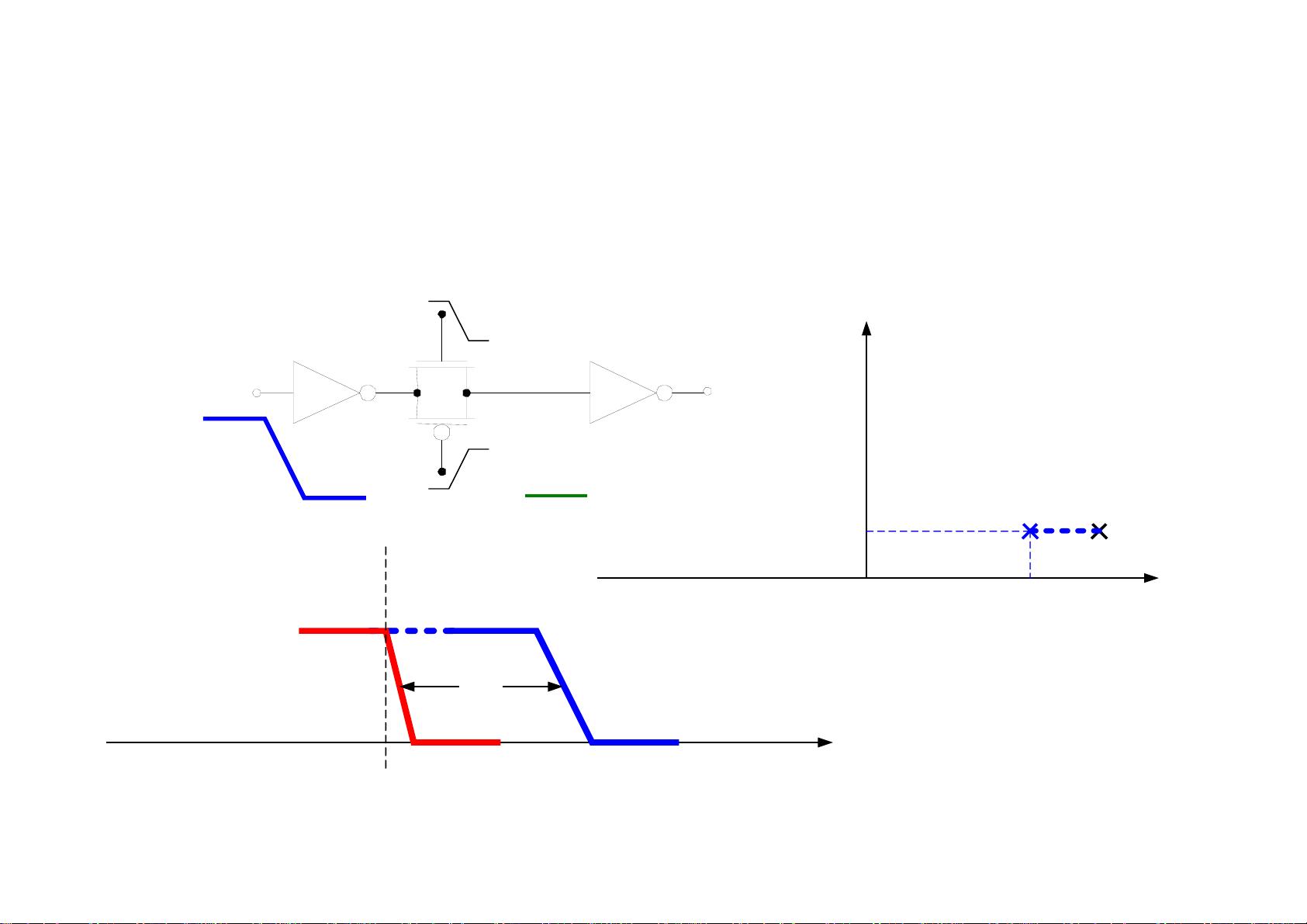

课件还讨论了Latch和Register的Latency(tDQ)与Data-to-Clock时间的关系,以及如何在正电平灵敏的Latch和Register中理解这些关系。在不同的tDC(Data to Clock)时间条件下,tDQ(Data to Clock Delay)的值会有所不同,这对理解和优化电路性能至关重要。

此外,对于建立时间的精确考虑,课件展示了tD2C和tC2Q之间的关系,tD2C表示数据到时钟的时间,tC2Q是时钟到输出的时间。为了确保正确工作,setup time (tSu) 必须小于tC2Q,并且有一个1.05倍的tC2Q作为安全余量,以应对工艺、电压和温度变化的影响。

最后,课件通过示例解释了在时钟到达前,数据必须稳定在输入端的重要性,以满足TSetup-1条件,确保在时钟边沿触发时,数据已经正确地在Register或Latch中被采样。

本课件深入浅出地探讨了时序电路中关键的时序参数和概念,这对于理解和设计高速数字系统中的时序逻辑具有重要意义。