VERILOG教程:基本运算逻辑和Verilog HDL模型

需积分: 0 127 浏览量

更新于2024-01-01

收藏 273KB DOC 举报

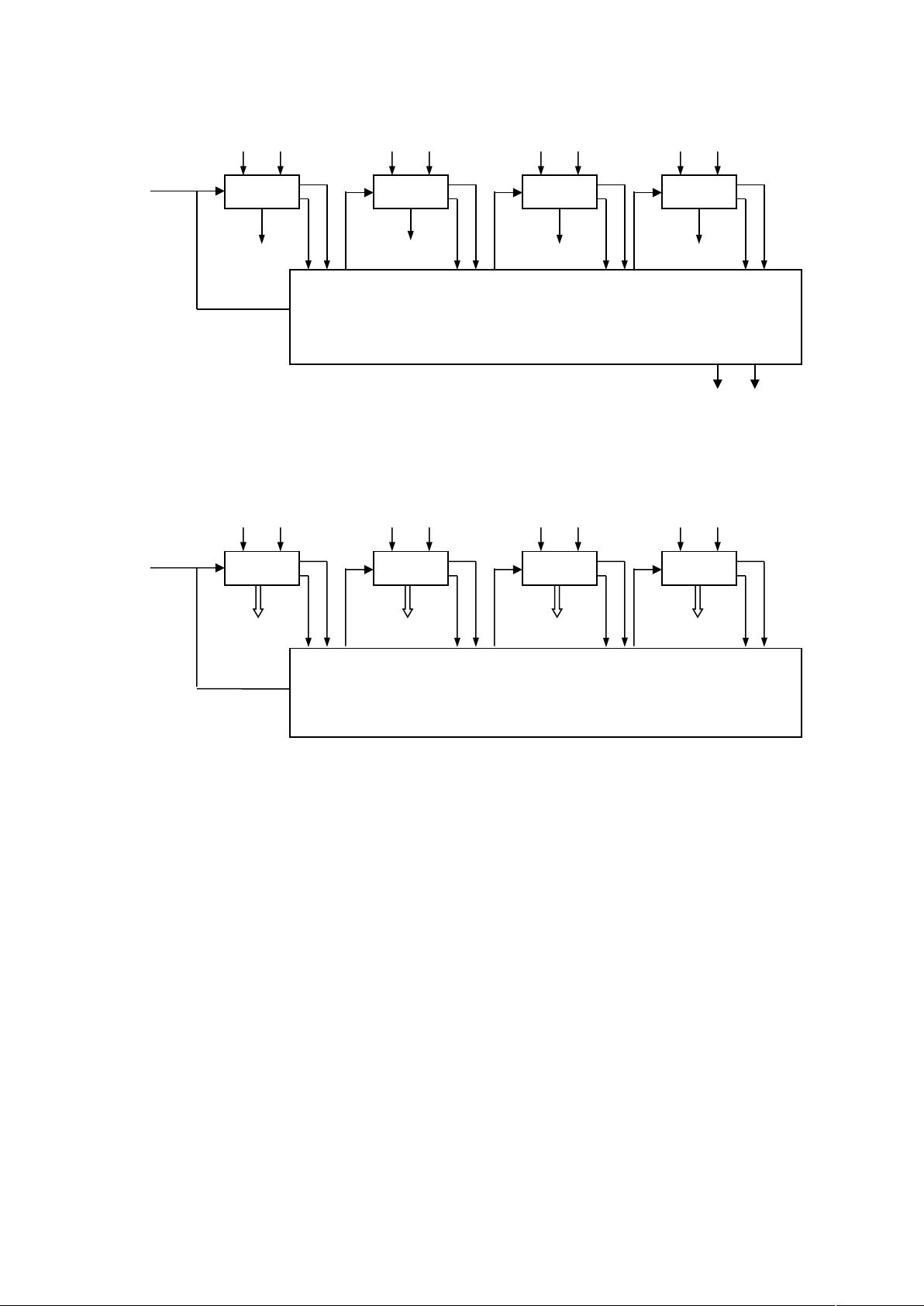

本课件是一个VERILOG教程,主要讲述的是VERILOG的语法知识和具体规范,涵盖了很基础、很基本的内容。其中的第五章则着重介绍了基本运算逻辑及其在Verilog HDL中的模型表达。在前言中,课件指出了复杂的算法数字逻辑电路是由基本运算逻辑、数据流动控制逻辑和接口逻辑电路构成的,而对基本运算逻辑的深入了解则是设计复杂算法逻辑系统电路结构的基本功。尽管Verilog硬件描述语言可以帮助自动综合出复杂的组合和时序电路,对设计的电路进行全面细致的验证,但对于速度要求很高的特殊数字信号处理电路来说,其结构仍然由设计者来定夺。因此,为了提高算法的运算速度,除了提高制造工艺技术外,逻辑结构设计就成为了最重要的环节。而设计出结构合理的基本运算组合电路则是算法逻辑结构设计的基础。只有深入理解复杂组合电路的许多基本特点,才有可能通过电路结构的改进来提高算法逻辑系统的基本时钟速度,为结构合理的高速复杂算法的数字逻辑系统的构成打下坚实的基础。这部分知识应该是数字系统和计算机结构课程的重要内容,通过本课件,希望同学们能熟练地把学过的基础知识运用到实际的Verilog HDL建模中。 Overall, this courseware provides a comprehensive overview of VERILOG, with a particular focus on the syntax and specific specifications. The fifth chapter delves into the basic operation logic and its expression in Verilog HDL models. The courseware emphasizes the importance of understanding the fundamental operation logic in designing complex algorithmic logic systems. It highlights the role of logic structure design in improving algorithmic operation speed and laying a solid foundation for high-speed complex algorithmic digital logic systems. Additionally, the courseware aims to equip students with the ability to apply their foundational knowledge to practical Verilog HDL modeling. With a thorough understanding of the basic principles and hands-on practice, students will be able to utilize Verilog HDL effectively.

2021-10-07 上传

2010-01-26 上传

2011-02-08 上传

2021-10-01 上传

2012-05-29 上传

a254591139

- 粉丝: 0

- 资源: 12

最新资源

- C语言数组操作:高度检查器编程实践

- 基于Swift开发的嘉定单车LBS iOS应用项目解析

- 钗头凤声乐表演的二度创作分析报告

- 分布式数据库特训营全套教程资料

- JavaScript开发者Robert Bindar的博客平台

- MATLAB投影寻踪代码教程及文件解压缩指南

- HTML5拖放实现的RPSLS游戏教程

- HT://Dig引擎接口,Ampoliros开源模块应用

- 全面探测服务器性能与PHP环境的iprober PHP探针v0.024

- 新版提醒应用v2:基于MongoDB的数据存储

- 《我的世界》东方大陆1.12.2材质包深度体验

- Hypercore Promisifier: JavaScript中的回调转换为Promise包装器

- 探索开源项目Artifice:Slyme脚本与技巧游戏

- Matlab机器人学习代码解析与笔记分享

- 查尔默斯大学计算物理作业HP2解析

- GitHub问题管理新工具:GIRA-crx插件介绍