使用TimeQuest Timing Analyzer进行FPGA时序分析教程

需积分: 15 136 浏览量

更新于2024-07-16

1

收藏 704KB DOCX 举报

"基于FPGA的静态时序分析文档主要介绍了如何使用TimeQuestTimingAnalyzer这一强大的时序分析工具,适用于FPGA设计的初学者。文档通过一个DAC7512控制器的Verilog设计实例,详细阐述了TimeQuest进行时序设计和分析的方法。文档内容涵盖了时序分析的基本概念和TimeQuest的操作流程。"

在FPGA设计中,时序分析至关重要,因为它确保设计能够满足速度性能要求,避免因信号延迟导致的错误。TimeQuestTimingAnalyzer是一款由Altera(现Intel FPGA)提供的工具,它采用了工业标准SDC(SynopsysDesignConstraints)进行设计约束、分析和报告,帮助设计师验证设计是否满足时序要求。

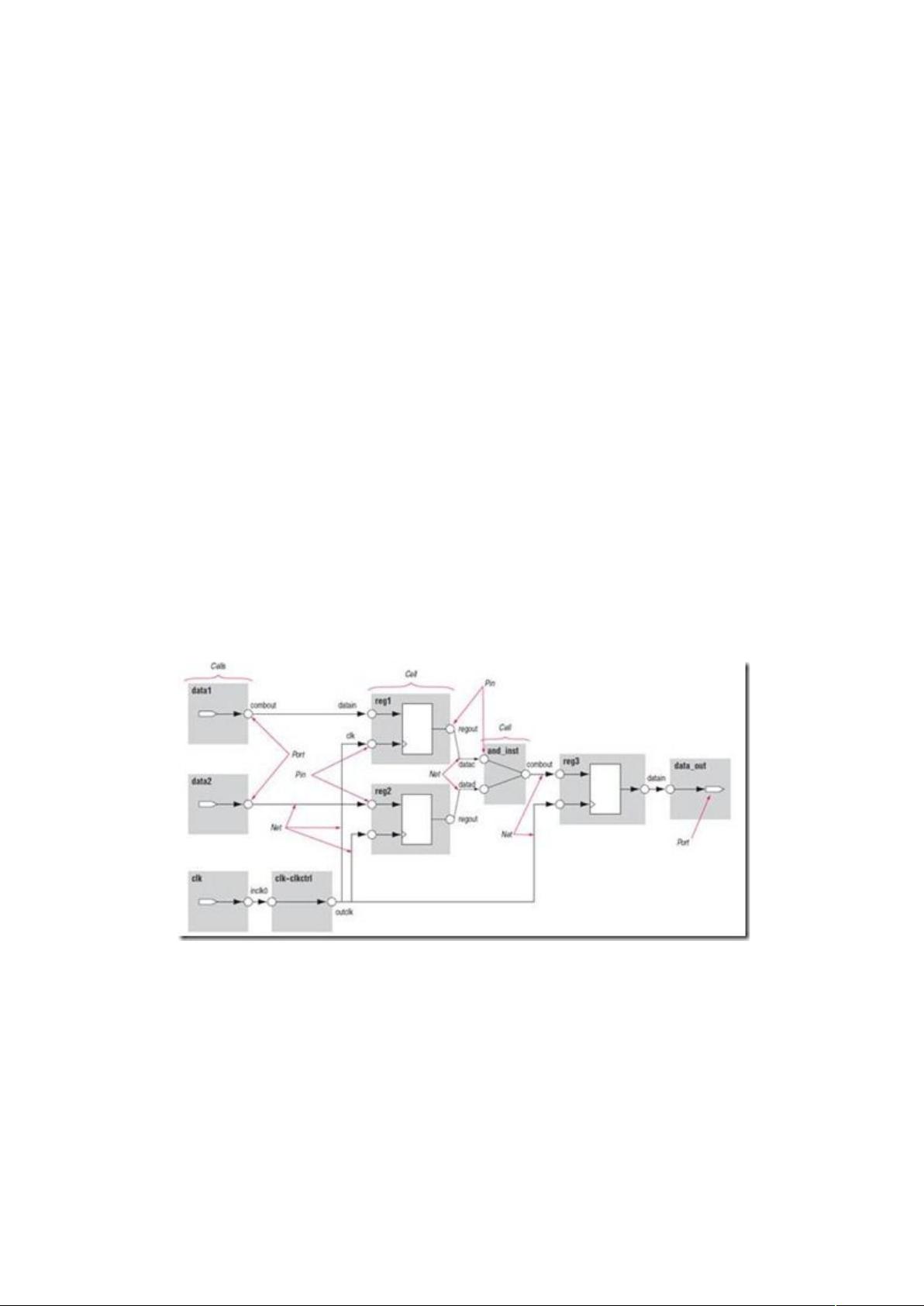

TimeQuest时序分析的基础是布局布线后的网表,该网表由几个关键元素组成:

1) Cells:这些是Altera器件中的基本构建块,例如逻辑元素(LEs)。

2) Pins:表示细胞的输入/输出接口,对应LE的输入/输出。

3) Nets:表示细胞内部或细胞之间的逻辑路径,包括IC-Inter-Cell延迟。

4) Ports:顶层逻辑的输入/输出端口,与实际器件引脚相对应。

5) Clocks:时钟约束指定的时钟信号,不仅限于时钟输入。

6) Keepers:指的是端口和寄存器类型的细胞。

7) Nodes:一个更广泛的概念,可以是上述元素的组合或其他未列出的元素。

TimeQuest的操作流程通常遵循Altera推荐的步骤:

1) 创建项目并导入设计文件:在QuartusII环境中建立项目,并添加所有必要的设计源代码,如Verilog或VHDL文件。

2) 设定时序约束:使用SDC文件定义时钟关系、路径约束等,确保设计满足速度要求。

3) 逻辑综合:将高级语言描述转化为门级网表。

4) 布局布线:根据设计需求对逻辑进行物理布局和互连布线。

5) 时序分析:TimeQuest读取布局布线后的网表,分析路径延迟,检查是否满足时序约束。

6) 报告和优化:如果时序未满足,TimeQuest将生成报告,指导设计者进行优化。

通过这个过程,设计者可以逐步确保FPGA设计的时序正确性,同时利用TimeQuest提供的各种工具进行性能调优,以达到最佳的系统运行速度。对于初学者而言,理解这些概念和流程是掌握FPGA设计的关键。

592 浏览量

729 浏览量

625 浏览量

578 浏览量

531 浏览量

712 浏览量

Arist9612

- 粉丝: 3876

- 资源: 20