异步DSP核心:性能与低功耗的新突破

33 浏览量

更新于2024-09-01

收藏 174KB PDF 举报

本文主要探讨了在现代集成电路设计领域中,一种新兴技术——异步DSP核心设计的重要性及其与传统同步设计的差异。尽管同步设计普遍依赖于全球一致的时钟频率,作为衡量处理器性能的关键指标,但随着半导体技术向更小规模发展,降低功耗的需求日益迫切。异步设计因其功耗低、电路可靠性高的特性,被认为是一种潜在的解决方案。

异步设计的核心挑战在于缺乏标准化工具流程,过去由于技术限制和复杂性,它并未得到广泛应用。然而,随着EDA工具的进步,尤其是支持异步逻辑的高级编程语言和事件驱动架构的发展,异步设计的可行性逐渐增强。商业市场上,特别是在嵌入式感应器等对低功耗和电流稳定性有极高要求的特定市场,已经开始看到基于异步设计的产品。

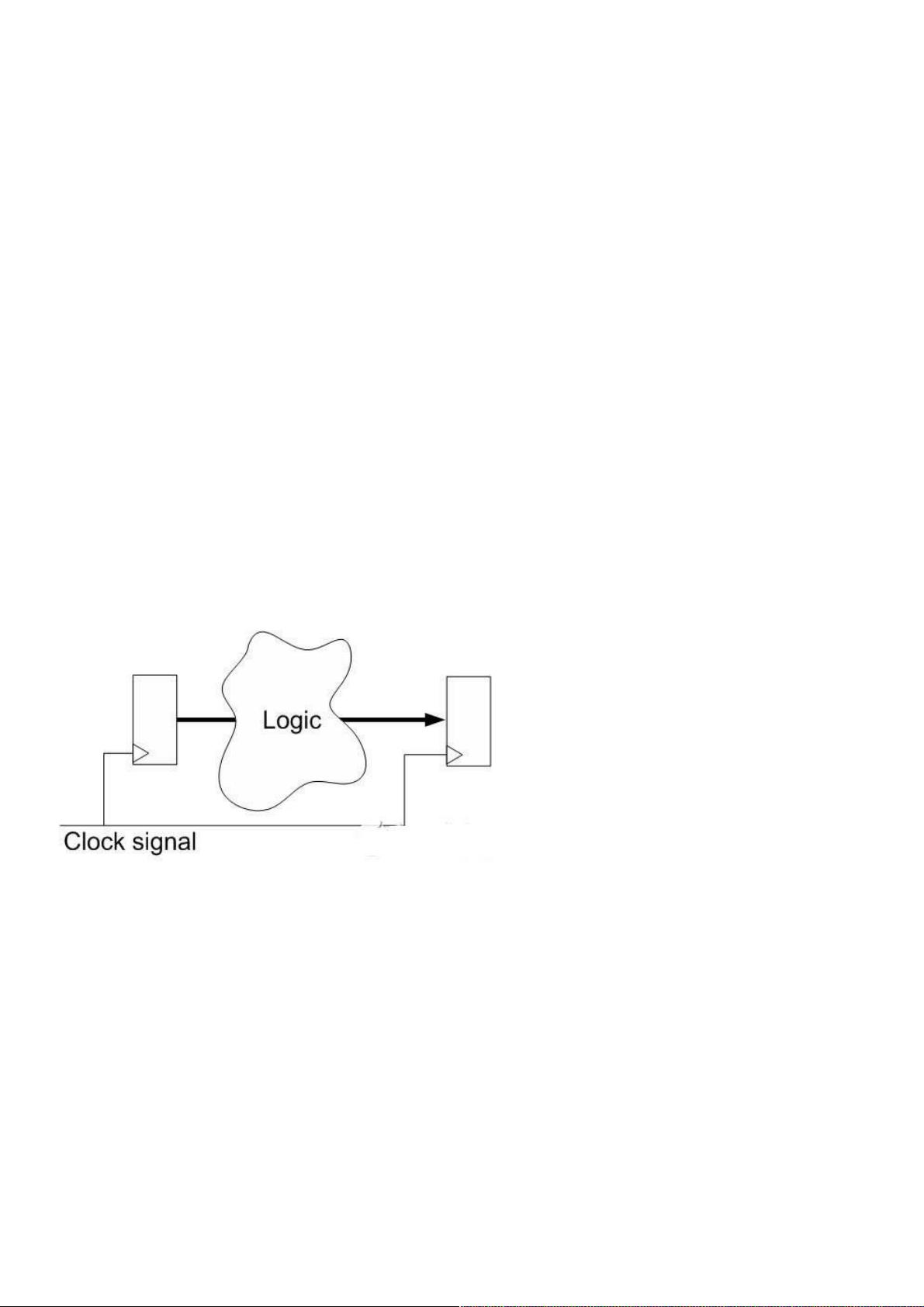

本文特别提到,异步技术已经突破了小众应用的界限,一款全新的通用异步数字信号处理器核心正崭露头角。与传统的同步设计相比,这种核心摒弃了时钟控制的有限状态机和触发器,转而通过逻辑云来计算电路状态,无需外部时钟信号驱动。这种设计允许更为灵活且能效更高的运算,对于IC设计人员来说,提供了更多的设计可能性和性能提升空间。

总结来说,这篇文章深入剖析了异步DSP核心设计如何在高性能和低功耗之间找到平衡,并强调了其在应对现代集成电路设计挑战中的重要角色。随着技术进步,异步设计有望成为未来处理器设计的一个关键趋势,尤其是在对功耗敏感的领域,如物联网设备和电池供电系统。

2020-10-16 上传

2020-10-19 上传

2020-11-02 上传

2023-11-10 上传

2023-06-23 上传

2024-10-26 上传

2023-06-12 上传

2024-10-27 上传

2023-05-12 上传

weixin_38610277

- 粉丝: 8

- 资源: 906

最新资源

- SSM动力电池数据管理系统源码及数据库详解

- R语言桑基图绘制与SCI图输入文件代码分析

- Linux下Sakagari Hurricane翻译工作:cpktools的使用教程

- prettybench: 让 Go 基准测试结果更易读

- Python官方文档查询库,提升开发效率与时间节约

- 基于Django的Python就业系统毕设源码

- 高并发下的SpringBoot与Nginx+Redis会话共享解决方案

- 构建问答游戏:Node.js与Express.js实战教程

- MATLAB在旅行商问题中的应用与优化方法研究

- OMAPL138 DSP平台UPP接口编程实践

- 杰克逊维尔非营利地基工程的VMS项目介绍

- 宠物猫企业网站模板PHP源码下载

- 52简易计算器源码解析与下载指南

- 探索Node.js v6.2.1 - 事件驱动的高性能Web服务器环境

- 找回WinSCP密码的神器:winscppasswd工具介绍

- xctools:解析Xcode命令行工具输出的Ruby库