RTL8181

CONFIDENTIAL v1.0

10

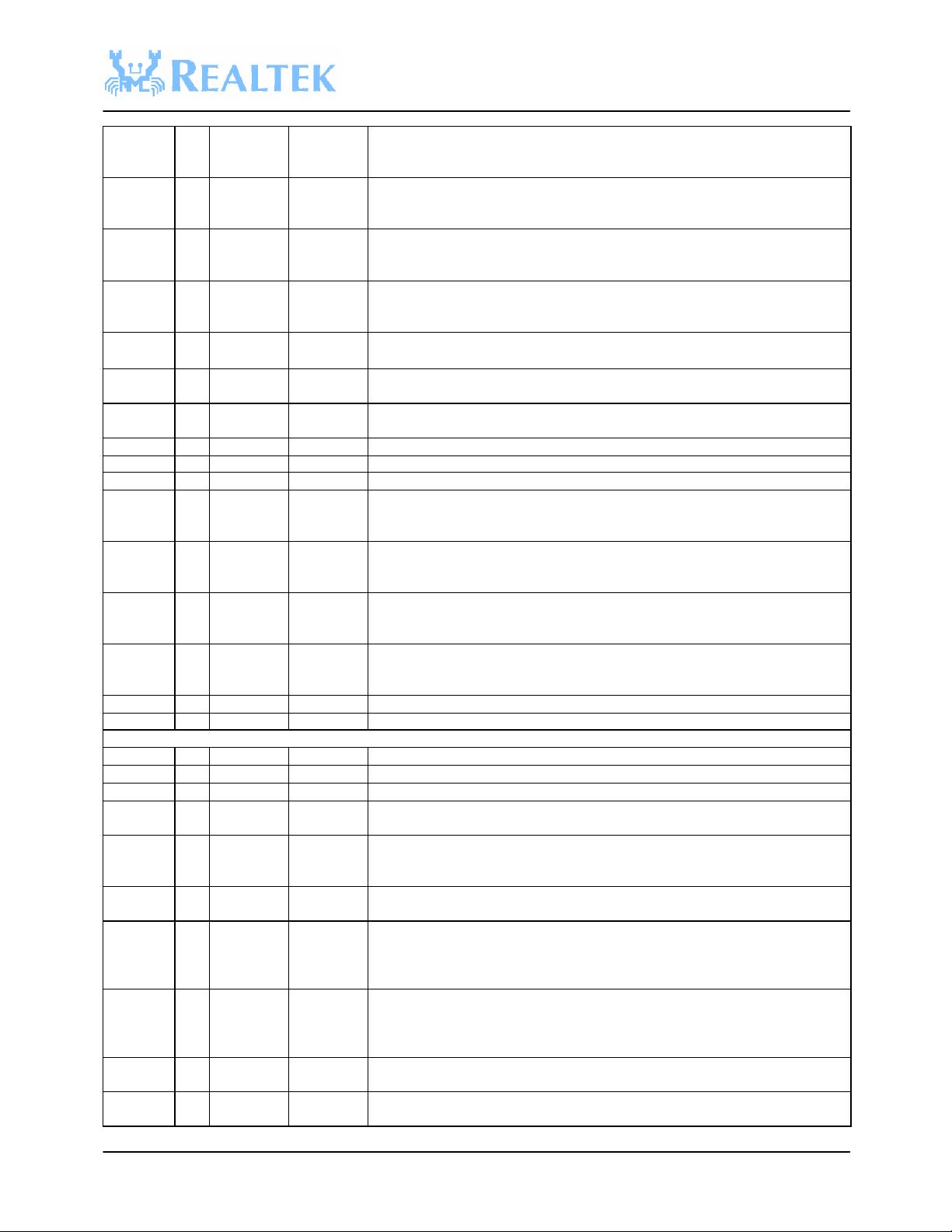

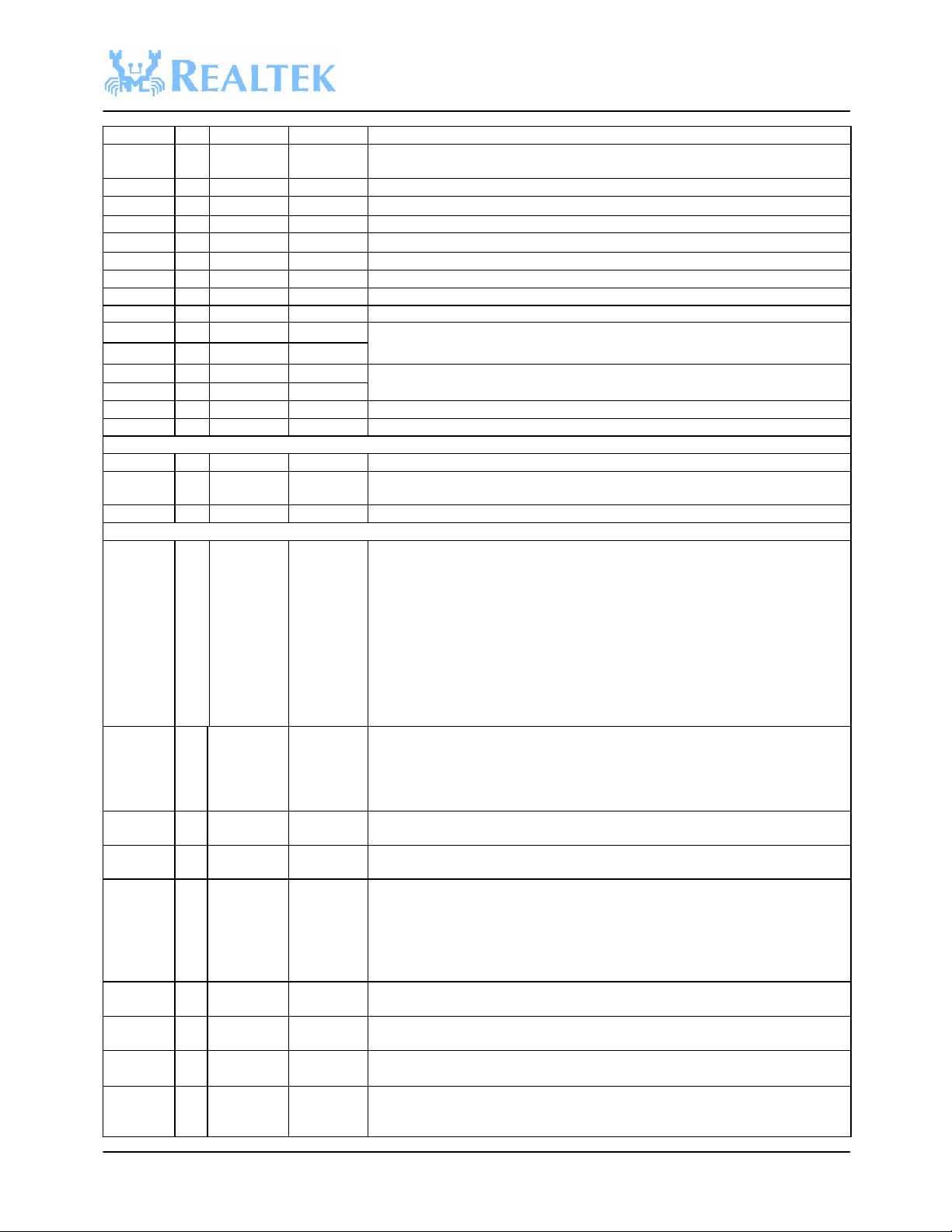

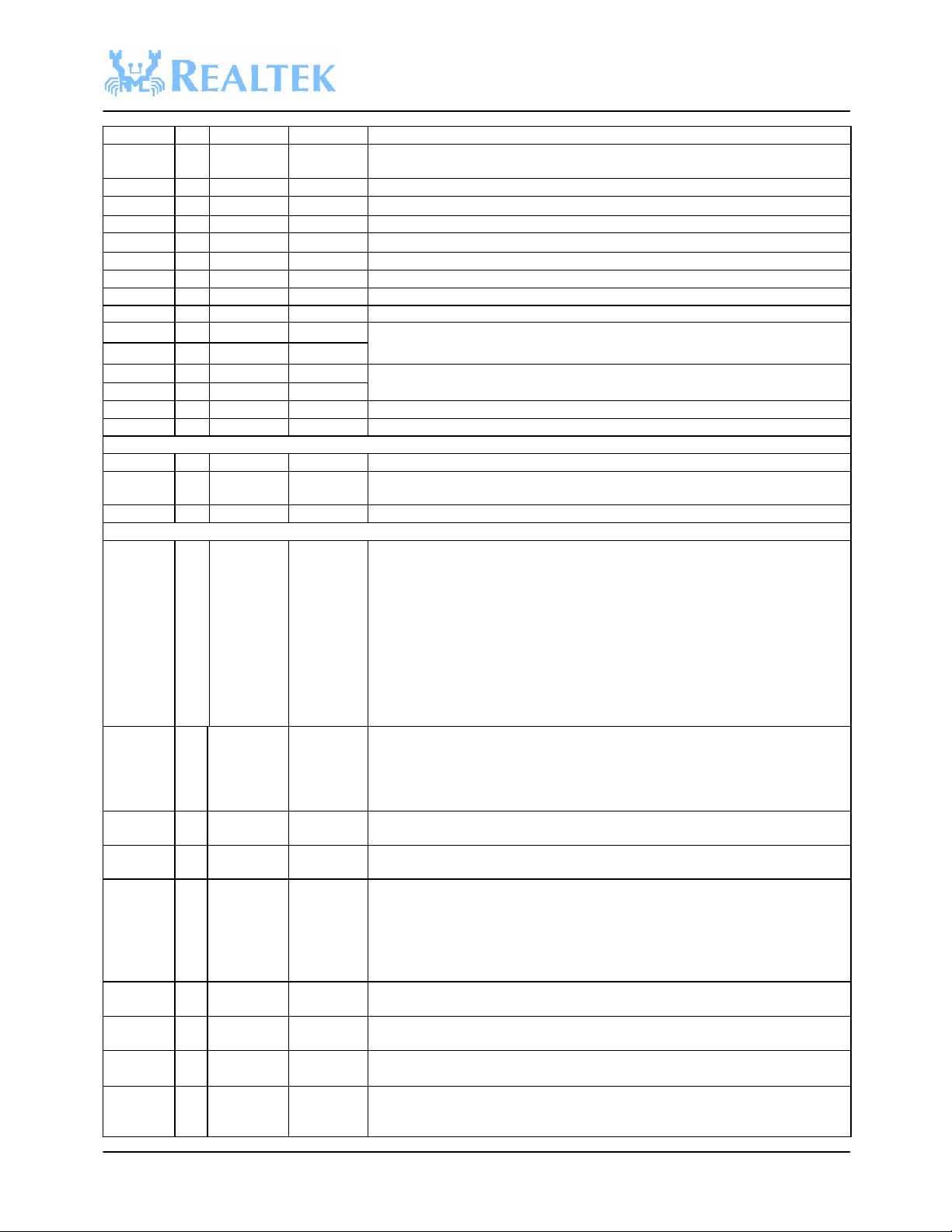

PAPE O 82 K19 Transmit PA Power Enable: Assert high when starting transmission.

PE1/PHIT

XQ

O 84 K18 Not used in the Maxim RF chipset.

PE2 O 85 J20 Not used in the Maxim RF chipset now.

RXIP AI* 110 B19 Receive (Rx) In-phase Analog Data: Positive path of differential pair.

RXIN X 109 B20 Receive (Rx) In-phase Analog Data: Negative path of differential pair.

RXQP AI 106 C18 Receive (Rx) Quadrature-phase Analog Data: Positive path of differential pair.

RXQN X 105 C19 Receive (Rx) Quadrature-phase Analog Data: negative path of differential pair.

RSSI X 103 D17 Not used in Maxim RF chipset.

TXDET AI 102 D18 To internal ADC which detects transmit power.

VREFI AI 101 C20 Not used in Maxim RF chipset.

TXIP AO 97 E19

TXIN AO 96 F18

Transmit (TX) In-phase Digital Data: Combining before connecting to TX_I of

RF2948B.

TXQP AO 94 E20

TXQN AO 93 F20

Transmit (TX) Quadrature Digital Data: Combining before connecting to TX_Q

of RF2948B.

TXAGC AO 91 F19 Transmit gain control output to RF2948.

RXAGC AO 90 G18 Analog Drive to the Receiver AGC Control.

Miscellaneous

R10K I/O 99 E18 This pin must be pulled low by a 10K O resistor.

XO O 87 H18 Crystal Feedback Output: This output is reserved for crystal connection. It should

be left open when XI is driven with an external 44 MHz oscillator.

XI I 88 H19 44 MHz OSC Input

PCI Interface

AD31-0 T/S *X A13,B12,A8

,C8,B8,C4,

B3,A3,C2,D

3,C1,G1,H3,

J3,V2,V1,V

3,W2,V4,w

3,Y3,W6,Y

6,V7,Y14,

W14,Y15,Y

19,U16,R18

,T20,R19

PCI address and data multiplexed pins. The address phase is the first clock cycle in

which FRAMEB is asserted. During the address phase, AD31-0 contains a physical

address (32 bits). For I/O, this is a byte address, and for configuration and memory, it

is a double-word address. Write data is stable and valid when IRDYB is asserted. R

data is stable and valid when TRDYB is asserted. Data I is transferred during those

clocks where both IRDYB and TRDYB are asserted.

C/BE3-0 T/S *X W20,V19,U

17,V20

PCI bus command and byte enables multiplexed pins. During the address phase

of a transaction, C/BE3-0 define the bus command. During the data phase,

C/BE3-0 are used as Byte Enables. The Byte Enables are valid for the entire data

phase and determine which byte lanes carry meaningful data. C/BE0 applies to

byte 0, and C/BE3 applies to byte 3.

CLK O *X N19 PCI clock: This clock input provides timing for all PCI transactions and is input

to the PCI device.

DEVSELB

S/T/

S

*X P3 Device Select: As a bus master, the RTL8181 samples this signal to insure that a

PCI target recognizes the destination address for the data transfer.

FRAMEB S/T/

S

*X N20 Cycle Frame: As a bus master, this pin indicates the beginning and duration of an

access. FRAMEB is asserted low to indicate the start of a bus transaction. While

FRAMEB is asserted, data transfer continues. When FRAMEB is deasserted, the

transaction is in the final data phase.

As a target, the device monitors this signal before decoding the address to check

if the current transaction is addressed to it.

GNTB T/S *X H20 Grant:Grant indicate to the agent that access to the bus has been granted.

REQB T/S *X J18 Request: Request indicates to the arbiter that this agent desires use of the bus.

IDSEL O *X A16 Initialization Device Select: This pin is used as a chip select during configuration

read and write transactions..

INTAB O/D

*X A17 Interrupt A: Used to request an interrupt. It is asserted low when an interrupt

condition occurs, as defined by the Interrupt Status, Interrupt Mask.

IRDYB S/T/

S

*X M18 Initiator Ready: This indicates the initiating agent’s ability to complete the

current data phase of the transaction.

As a bus master, this signal will be asserted low when the RTL8181 is ready to