使用VHDL设计FPGA/CPLD中的专用同步通信芯片

PDF格式 | 304KB |

更新于2024-08-30

| 144 浏览量 | 举报

"EDA/PLD中的用VHDL设计专用串行通信芯片"

在现代通信系统中,通信芯片扮演着至关重要的角色,它们是构建硬件平台的基础,负责处理OSI模型物理层的数据发送和接收任务。这些芯片还能适应不同的传输方式和协议,包括数据校验和组帧,以确保信息的准确无误。常见的串行通信芯片通常分为同步和异步两类。异步芯片,如INTEL的8250,广泛应用于各种系统,而同步通信芯片则需要支持特定的协议,例如BSC(平衡系统控制器)、HDLC(高级数据链路控制)和SDLC(同步数据链路控制)等。

过去,设计专用的同步收发器(SRT)通常依赖于传统的逻辑元件,这种方法可能导致设计周期长、调试困难以及系统稳定性的不足。然而,随着可编程ASIC技术的进步,尤其是现场可编程门阵列(FPGA)和复杂可编程逻辑器件(CPLD)的发展,现在设计者可以利用电子设计自动化(EDA)工具,使用硬件描述语言(如VHDL)来定制符合特定需求的通信芯片。

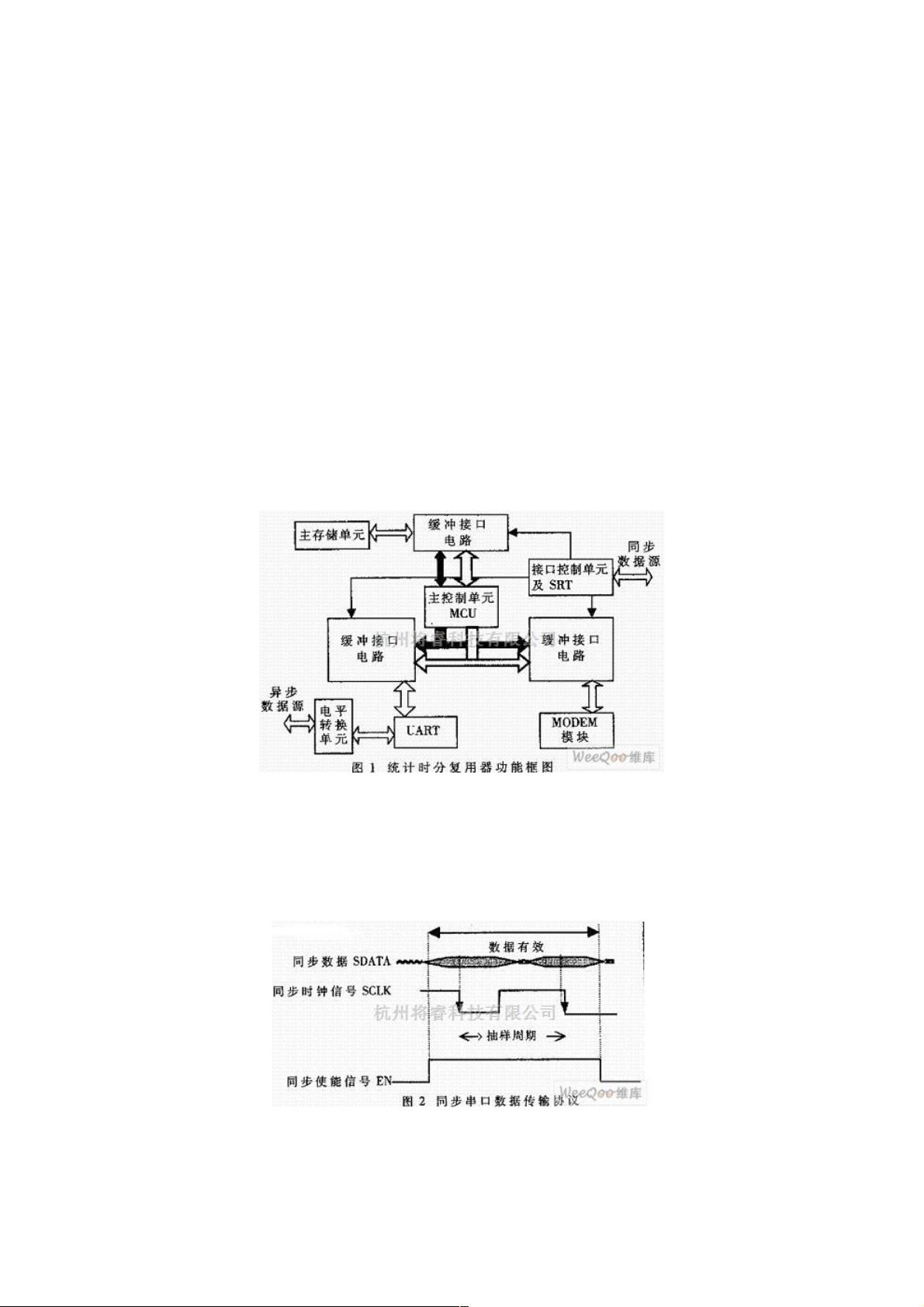

本文以开发统计时分复用器中的专用同步收发芯片为例,阐述了使用EDA技术和VHDL设计的流程。统计时分复用器能够将7路异步数据和1路同步数据进行复接,系统功能简洁且适用于近距离通信。为了节省成本和降低功耗,整个接口控制单元与SRT被集成在一个CPLD(XC95144)中。

在CPLD内部,设计包括接口控制单元和SRT两个主要部分。SRT的架构尤为关键,它可能包含多个功能模块,如波特率发生器、接收器、发送器、数据缓冲区以及错误检测模块。波特率发生器用于生成与通信速率匹配的时钟信号,接收器和发送器分别处理输入和输出数据流,数据缓冲区用于临时存储数据,而错误检测模块则确保数据传输的完整性,可能包含奇偶校验、CRC校验等功能。

由于采用了与INTEL 8250兼容的UART,主控单元的程序编写可以简化,因为操作流程得到了统一。这样,通过VHDL设计的SRT不仅可以满足特定的同步传输协议,还能够与现有系统无缝对接,提高了系统的灵活性和可靠性。

利用EDA/PLD技术,特别是VHDL,设计者可以快速地创建和优化针对特定应用的串行通信芯片,这极大地缩短了产品开发周期,提高了设计质量,并且降低了维护和升级的成本。这种趋势在现代通信领域中越来越普遍,因为它允许设计者根据实际需求定制高度专业化和高效能的通信解决方案。

相关推荐

weixin_38531788

- 粉丝: 4

最新资源

- 计算机组成原理期末试题及答案(2011参考)

- 均值漂移算法深入解析及实践应用

- 掌握npm与yarn在React和pg库中的使用

- C++开发学生信息管理系统实现多功能查询

- 深入解析SIMATIC NET OPC服务器与PLC的S7连接技术

- 离心式水泵原理与Matlab仿真教程

- 实现JS星级评论打分与滑动提示效果

- VB.NET图书馆管理系统源码及程序发布

- C#实现程序A监控与自动启动机制

- 构建简易Android拨号功能的应用开发教程

- HTML技术在在线杂志中的应用

- 网页开发中的实用树形菜单插件应用

- 高压水清洗技术在储罐维修中的关键应用

- 流量计校正方法及操作指南

- WinCE系统下SD卡磁盘性能测试工具及代码解析

- ASP.NET学生管理系统的源码与数据库教程