Xilinx原语详解与应用

需积分: 13 97 浏览量

更新于2024-07-19

收藏 545KB PDF 举报

"Xilinx原语是FPGA设计中不可或缺的一部分,它们是Xilinx公司为用户提供的基础硬件逻辑单元,类似于库函数或者C++中的关键字。原语包括了LUT(查找表)、D触发器、RAM等基本元件,代表了FPGA内部的实际硬件。在设计流程中,所有设计单元最终都需要转化为目标器件上的原语才能被实现。原语的使用与HDL(硬件描述语言)的关系类似于汇编与C语言,提供了最直接的代码输入方式。

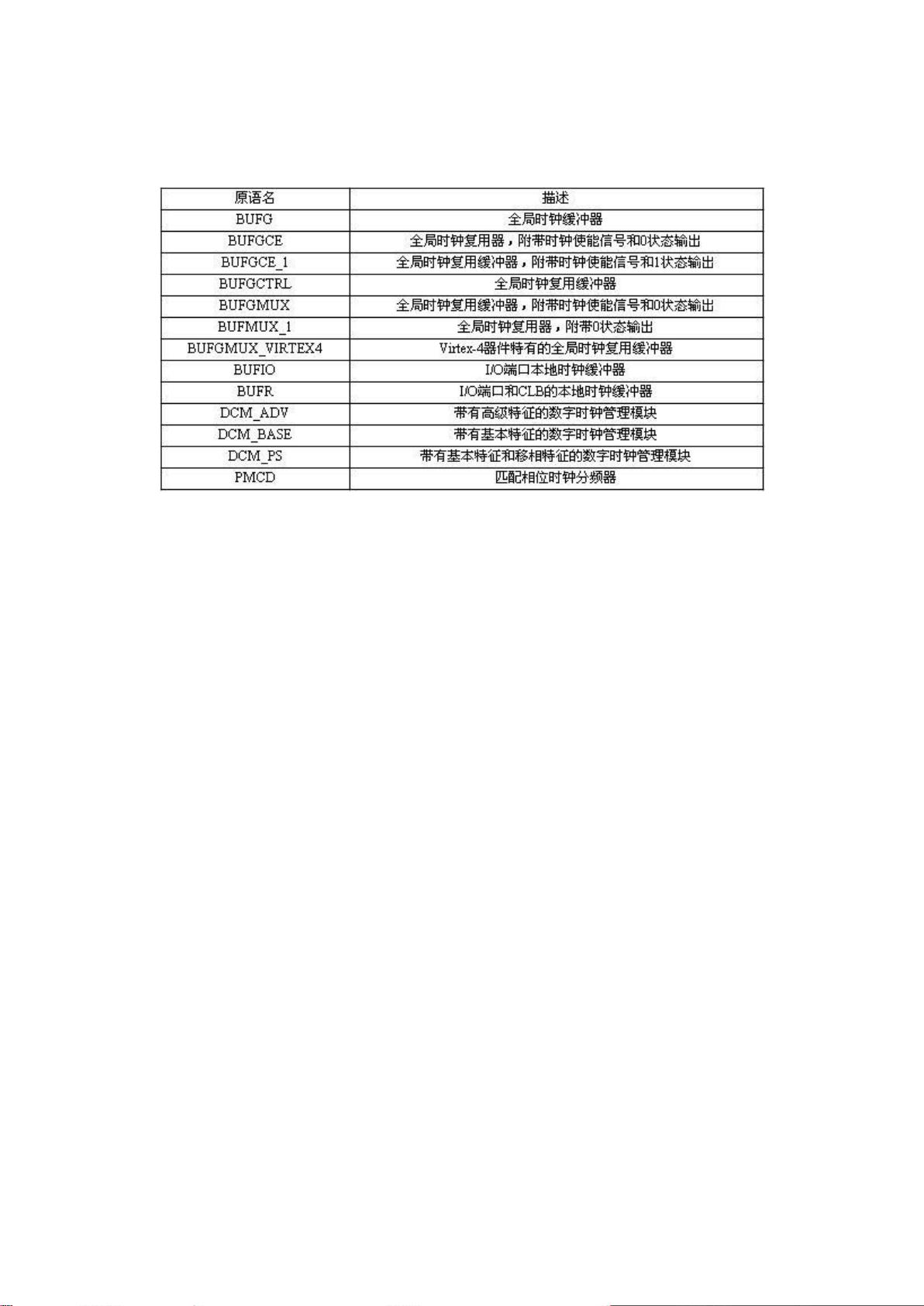

Xilinx的原语按照功能分为多个类别,包括计算组件、I/O端口组件、寄存器和锁存器、时钟组件、处理器组件、移位寄存器、配置和检测组件、RAM/ROM组件、Slice/CLB组件以及G比特收发器组件。这些组件覆盖了FPGA开发的各个方面,但需要注意的是,并非所有原语都能在任何型号的芯片上通用。

3.4.1 计算组件

计算组件主要是指DSP48核,这是一个18*18比特的有符号乘法器,后面连接了一个可配置流水线的3输入加法器。DSP48核的灵活性很高,乘法器和加法器的位宽可在18到48比特之间调整,广泛应用于需要乘法和加法操作的场合,如滤波器系统,可以提升系统性能,节省逻辑资源,并能支持高速运行。在Verilog中,可以通过以下模板实例化一个DSP48核:

```verilog

module fpga_v4_dsp48(

BCOUT, P, PCOUT, A, B, BCIN, C, CARRYIN, CARRYINSEL,

CE_A, CE_B, CE_C, CECARRYIN, CECINSUB, CECTRL, CEM, CEP, CLK,

OPMODE, PCIN, RSTA, RSTB, RSTC, RSTCARRYIN, RSTM, RSTP, SUBTRACT);

```

每个引脚都有特定的功能,例如`A`, `B`是乘法器输入,`CEA`, `CEB`是使能信号,`CLK`是时钟输入,`OPMODE`用于设置操作模式等。

使用原语时,设计师需要对目标芯片的特性有深入理解,确保所使用的原语与选定的FPGA型号兼容。对于不同系列的Xilinx芯片,虽然原语的基本概念相同,但具体实现和可用性可能有所差异。例如,Virtex-4系列提供了丰富的原语类型,而其他系列如Spartan或Artix可能会有不同的原语集。

Xilinx原语是FPGA设计的基础构建块,通过灵活组合和配置这些原语,设计师能够实现复杂的数字系统。理解和熟练掌握原语的使用,对于优化设计性能、节省资源和提高设计效率至关重要。

114 浏览量

2022-09-07 上传

126 浏览量

2018-01-24 上传

2016-07-31 上传

2020-12-03 上传

zhangtaibin209

- 粉丝: 1

- 资源: 9

最新资源

- Grace Gmail Plugin for Chrome-crx插件

- 在您的本机应用程序中设置应用程序图标-Swift开发

- FittingSurvivalModelss.zip_matlab例程_matlab_

- qqbot:QQBot:基于腾讯的SmartQQ的对话机器人

- exportDoc:使用Itext API解决使用Java创建Word文档的问题

- nodebootstrap-clustering:NodeBootstrap的群集组件

- heroku_template

- lab-06-后端

- 前端+php+Apache压缩文件

- 具有PKCE的轻量级OAuth 2.0客户端-Swift开发

- javascript

- vcDigitalImageProcess.zip_图形图像处理_Visual_C++_

- Arkiver Web Collector-crx插件

- App-TimeTracker:从命令行进行分布式时间跟踪

- ActiveUsers Block for Moodle-开源

- PyPI 官网下载 | sklearn2pmml-0.73.3.tar.gz