VHDL 实现:计数器设计与复位电路

需积分: 13 21 浏览量

更新于2024-09-12

收藏 87KB PDF 举报

"该资源主要介绍了使用VHDL进行计数器设计的一些基本规则和方法,包括带符号位加法运算、8X8位乘法电路设计、异步复位电路设计以及同步复位电路设计。通过这些基本的数字逻辑操作,可以构建不同类型的计数器。"

在VHDL中设计计数器,通常会涉及到数字逻辑的基本运算,如加法和乘法,以及复位信号的处理。以下是各部分的具体知识:

1. 带符号位加法运算:

这段代码展示了如何在VHDL中进行带符号位的加法操作。`std_logic_signed`库被用来处理带符号的二进制数。`adder4s2is`实体定义了两个4位输入a和b,以及相应的输出s和sbin。在行为架构中,首先将输入扩展一位(添加符号位),然后执行加法操作。这种运算在设计计数器时可能用于计算递增或递减的数值。

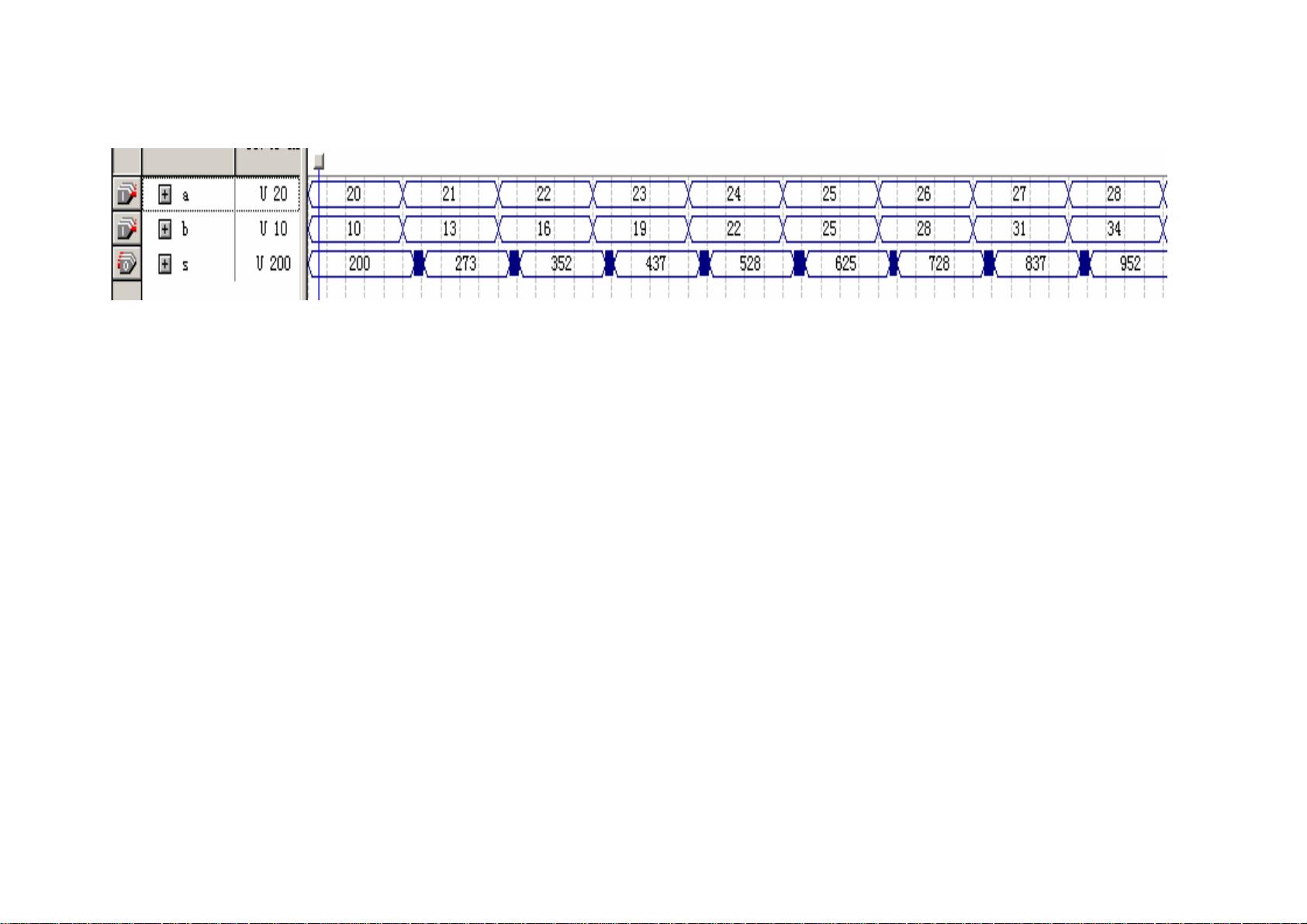

2. 8X8位乘法电路设计:

这段代码展示了8X8位乘法器的实现,使用了`std_logic_unsigned`库来处理无符号的二进制数。`multiply_8_1`实体接受两个8位输入a和b,输出一个16位的结果s。在行为架构中,简单的乘法操作是通过`a*b`完成的。这在设计计数器时可能会用于累加或累乘。

3. 异步复位电路设计:

异步复位电路在计数器设计中非常关键,因为它能确保在系统启动或复位信号激活时,计数器能够回到预设的初始状态。在这个例子中,`CP4_ASY_RST`实体有一个非同步的低电平有效复位信号`RST_N`,一个时钟信号`CLK`,一个数据输入`D`,和一个输出`Q`。当复位信号`RST_N`为0时,计数器的当前状态被清零;否则,在时钟上升沿,`Q`的值更新为`D`。

4. 同步复位电路设计:

同步复位电路与异步复位电路类似,但复位信号是在时钟边沿触发的。在给定的代码片段中,描述了一个同步复位电路的结构,但具体内容不完整。通常,同步复位会在时钟的上升沿或下降沿发生,确保系统在稳定的时钟周期内进行复位,避免了竞争冒险现象。

通过这些基础元素,可以构建各种类型的计数器,如模N计数器、二进制计数器、灰码计数器、同步计数器和异步计数器等。例如,可以利用加法器实现模N计数器,每次时钟脉冲到来时,计数器的值增加1,当达到N时复位回零。而复位电路则确保了计数器在特定条件下能正确重置。

在实际应用中,VHDL计数器设计还会考虑其他因素,如计数方向控制、计数速度优化、功耗管理、错误检测和校正等。设计者需要根据具体需求选择适当的计数器结构,并结合复位、加载和使能信号来实现复杂的计数功能。

1588 浏览量

点击了解资源详情

140 浏览量

151 浏览量

2024-11-08 上传

105 浏览量

463 浏览量

erjan619

- 粉丝: 0

- 资源: 2