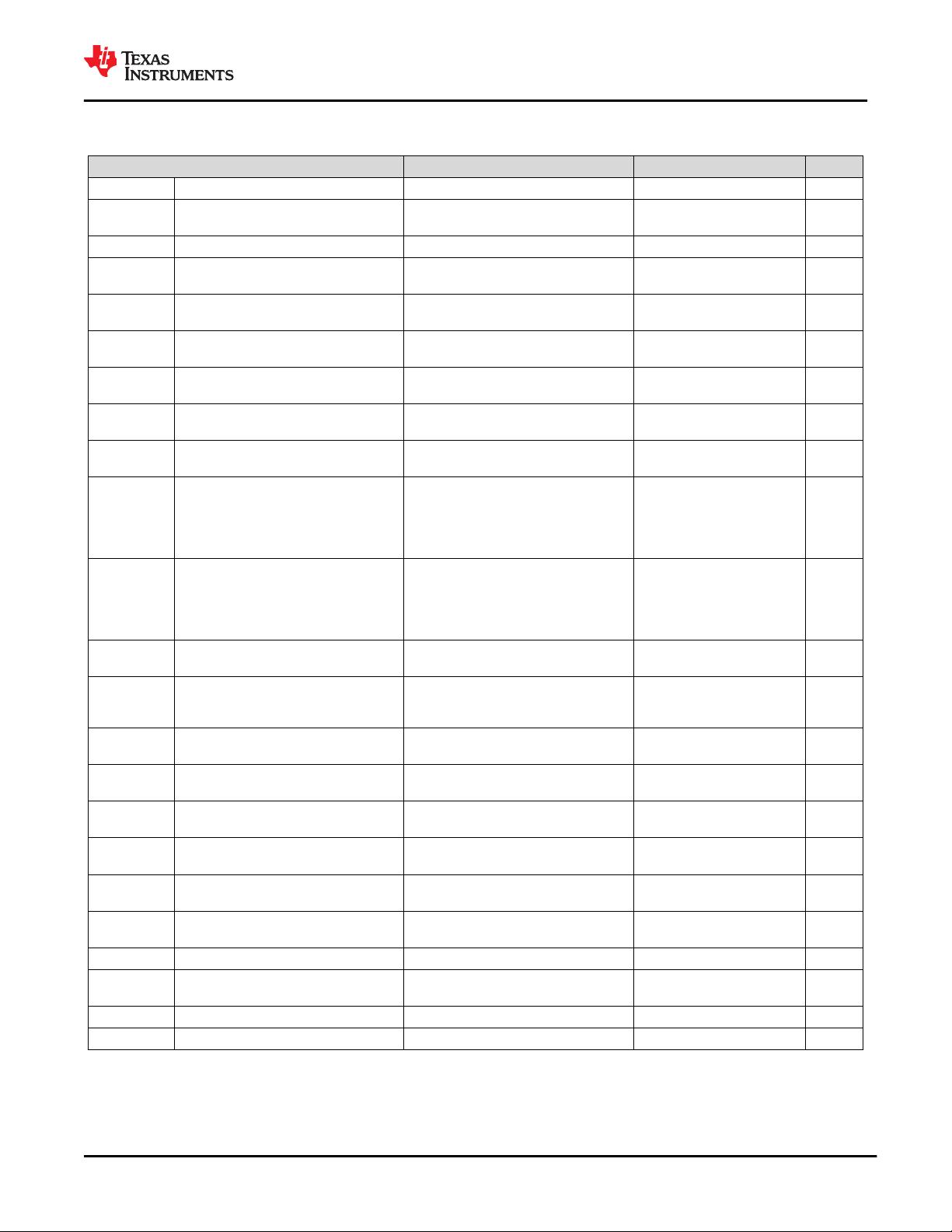

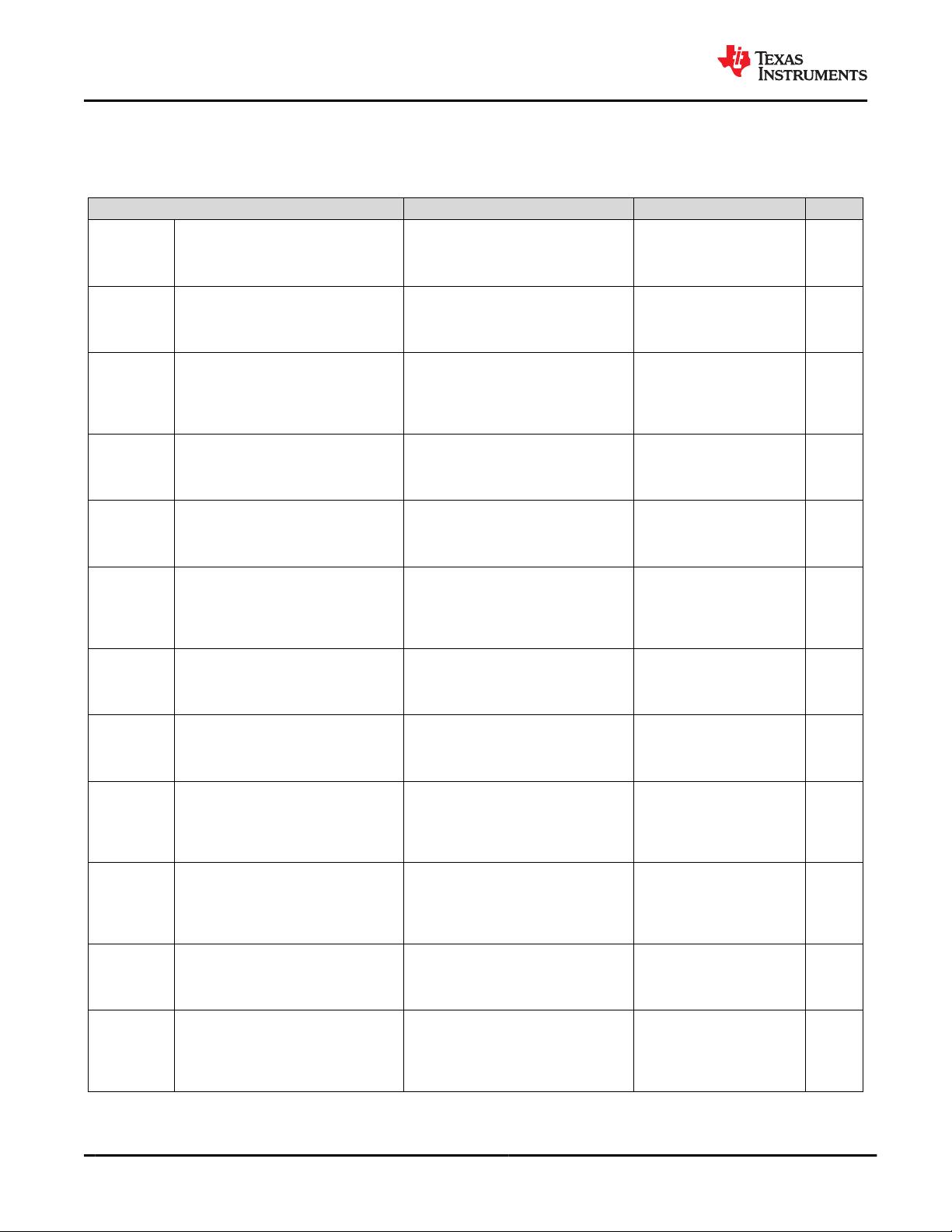

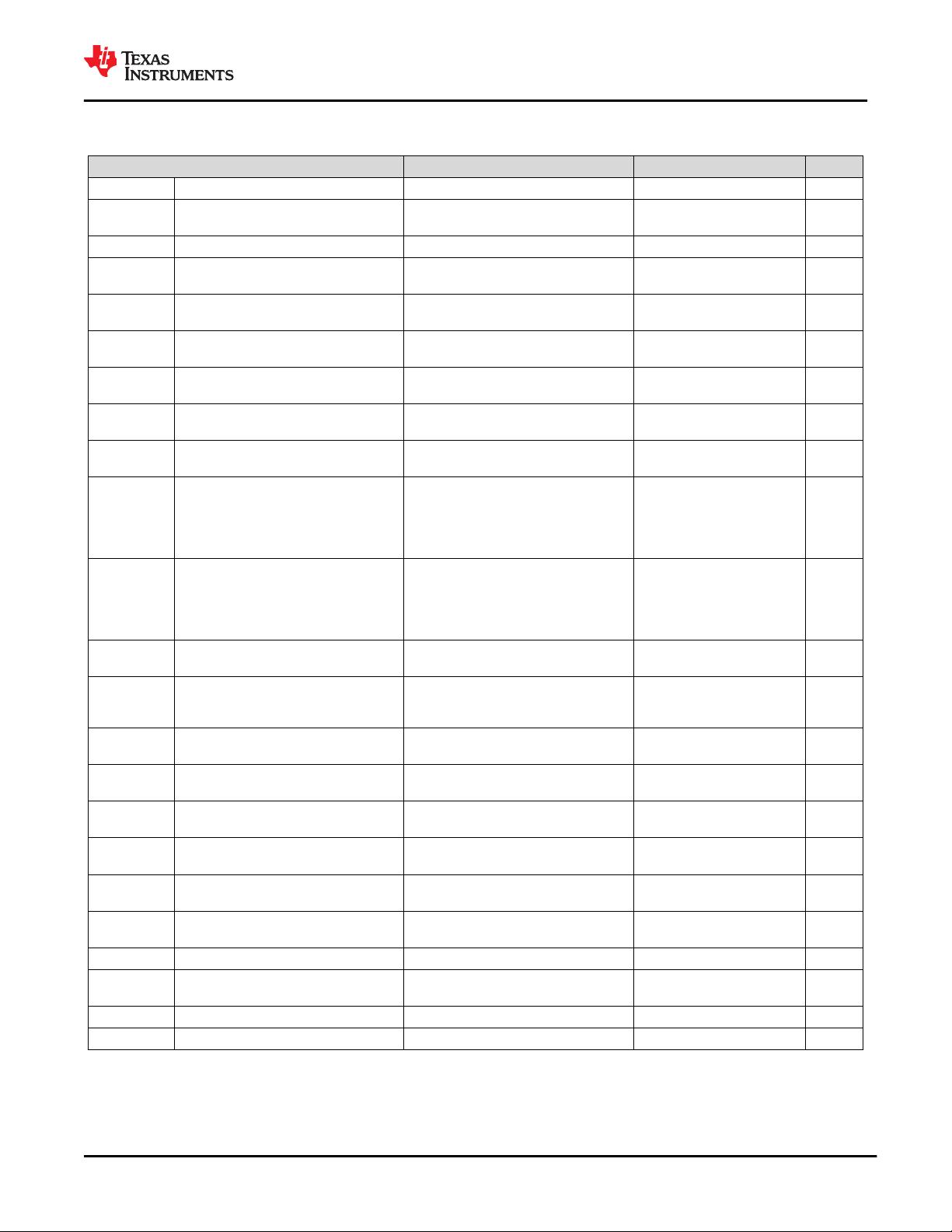

7.6 Electrical Characteristics (continued)

parameters valid across -40℃ ≤ T

A

≤ 125℃ (unless otherwise noted)

PARAMETER TEST CONDITIONS MIN TYP MAX UNIT

V

OL

LIN dominant low-level output voltage

(3)

TXD = low, 7 V ≤ V

SUP

≤ 48 V 0.2 V

SUP

V

OL

LIN dominant low-level output voltage

(1)

(2)

TXD = low, 7 V ≤ V

SUP

≤ 18 V 0.2 V

SUP

V

OL

LIN dominant low-level output voltage

(3)

TXD = low, 4 V ≤ V

SUP

< 7 V 1.2 V

V

SUP_NON_OP

V

SUP

where impact of recessive LIN bus

< 5% (ISO/DIS 17987 Param 11)

TXD & RXD open, LIN = 4 V to 58 V –0.3 58 V

I

BUS_LIM

Limiting current (ISO/DIS 17987 Param

57)

TXD = 0 V, V

LIN

= 48 V, R

MEAS

= 440 Ω,

V

SUP

= 48 V, V

BUSdom

< 4.518 V

75 120 300 mA

I

BUS_PAS_dom

Receiver leakage current, dominant

(ISO/DIS 17987 Param 13)

LIN = 0 V, V

SUP

= 24 V Driver off/

recessive; See Figure 8-6

–2 mA

I

BUS_PAS_rec1

Receiver leakage current, recessive

(ISO/DIS 17987 Param 14)

LIN > V

SUP

, 8 V ≤ V

SUP

≤ 48 V, Driver

off; See Figure 8-7

20 µA

I

BUS_PAS_rec2

Receiver leakage current, recessive

(ISO/DIS 17987 Param 14)

LIN = V

SUP

, Driver off; See Figure 8-7 –5 5 µA

I

BUS_NO_GND

Leakage current, loss of ground

(ISO/DIS 17987 Param 60)

GND = V

SUP

, 0 V ≤ V

LIN

< 36 V, V

SUP

=

24 V; Figure 8-8

–2 2 mA

I

leak gnd(dom)

Leakage current, loss of ground

(5)

V

SUP

= 8 V, GND = open, V

SUP

= 18 V,

GND = open

R

Commander

= 1 kΩ, C

L

= 1 nF

R

Responder

= 20 kΩ, C

L

= 1 nF

LIN = dominant

–1 1 mA

I

leak gnd(rec)

Leakage current, loss of ground

(5)

V

SUP

= 8 V, GND = open, V

SUP

= 18 V,

GND = open

R

Commander

= 1 kΩ, C

L

= 1 nF

R

Responder

= 20 kΩ, C

L

= 1 nF

LIN = recessive

-100 100 µA

I

BUS_NO_BAT

Leakage current, loss of supply

(ISO/DIS 17987 Param 61)

0 V ≤ V

LIN

≤ 48 V, V

SUP

= GND;

See; Figure 8-9

5 µA

V

BUSdom

Low level input voltage (ISO/DIS 17987

Param 62)

(3)

LIN dominant (including LIN dominant

for wake-up); See Figure 8-4 and Figure

8-3

0.4 V

SUP

V

BUSrec

High level input voltage (ISO/DIS 17987

Param 63)

(3)

LIN recessive; See Figure 8-4 and

Figure 8-3

0.6 V

SUP

V

IH

LIN recessive high-level input voltage

(1)

(2)

7 V ≤ V

SUP

≤ 18 V 0.47 0.6 V

SUP

V

IL

LIN dominant low-level input voltage

(1)

(2)

7 V ≤ V

SUP

≤ 18 V 0.4 0.53 V

SUP

V

BUS_CNT

Receiver center threshold (ISO/DIS

17987 Param 64)

V

BUS_CNT

= (V

BUSdom

+ V

BUSrec

)/2 See

Figure 8-4 and Figure 8-3

0.475 0.5 0.525 V

SUP

V

HYS

Hysteresis voltage (ISO/DIS 17987

Param 65)

V

HYS

= (V

BUSrec

- V

BUSdom

) See Figure

8-4 and Figure 8-3

0.175 V

SUP

V

HYS

Hysteresis voltage (SAE J2602)

V

HYS

= V

IH

- V

IL

See Figure 8-4 and

Figure 8-3

0.07 0.175 V

SUP

V

SERIAL_DIODE

Serial diode LIN termination pullup path I

SERIAL_DIODE

= 10 μA 0.4 0.7 1 V

R

PU

Pullup resistor to V

SUP

(ISO/DIS 17987

Param 26)

Normal and Standby modes 20 45 60 kΩ

I

RSLEEP

Pullup current source to V

SUP

Sleep mode, V

SUP

= 27 V, LIN = GND –20 –2 µA

C

LINPIN

Capacitance of the LIN pin V

SUP

= 14 V 25 pF

(1) SAE 2602 commander node load conditions: 5.5 nF/4 kΩ and 899 pF/20 kΩ

(2) SAE 2602 responder node load conditions: 5.5 nF/875 Ω and 899 pF/900 Ω

(3) ISO 17987 bus load conditions (C

LINBUS

, R

LINBUS

) include 1 nF/1 kΩ; 6.8 nF/660 Ω; 10 nF/500 Ω.

(4) RXD uses open drain output structure therefore V

OL

level is based upon microcontroller supply voltage V

CC

.

(5) I

leak gnd

= (V

BAT

- V

LIN

)/R

Load

www.ti.com

TLIN2024A-Q1

SLLSFM7 – JUNE 2022

Copyright © 2022 Texas Instruments Incorporated

Submit Document Feedback

7

Product Folder Links: TLIN2024A-Q1