CUDA架构:GPU并行计算的新纪元

需积分: 50 67 浏览量

更新于2024-09-13

收藏 1.09MB PDF 举报

“CUDA架构.pdf”是一篇详细介绍NVIDIA CUDA架构的文章,内容涵盖了GPU在并行计算中的应用,以及CUDA如何解决GPU编程难题,包括GPU的困境、芯片结构和多处理器组织。

文章首先介绍了GPU在2007年前面临的困境。传统上,GPU主要用于图形渲染,依赖图形API编程,这限制了其在其他计算任务上的应用。编程难度大,非图形应用处理API时有额外开销,DRAM内存带宽瓶颈,以及无法在DRAM上进行通用写操作,都是当时GPU计算的障碍。NVIDIA的Tesla架构和CUDA的引入,旨在打破这些限制,使GPU成为通用并行计算平台。

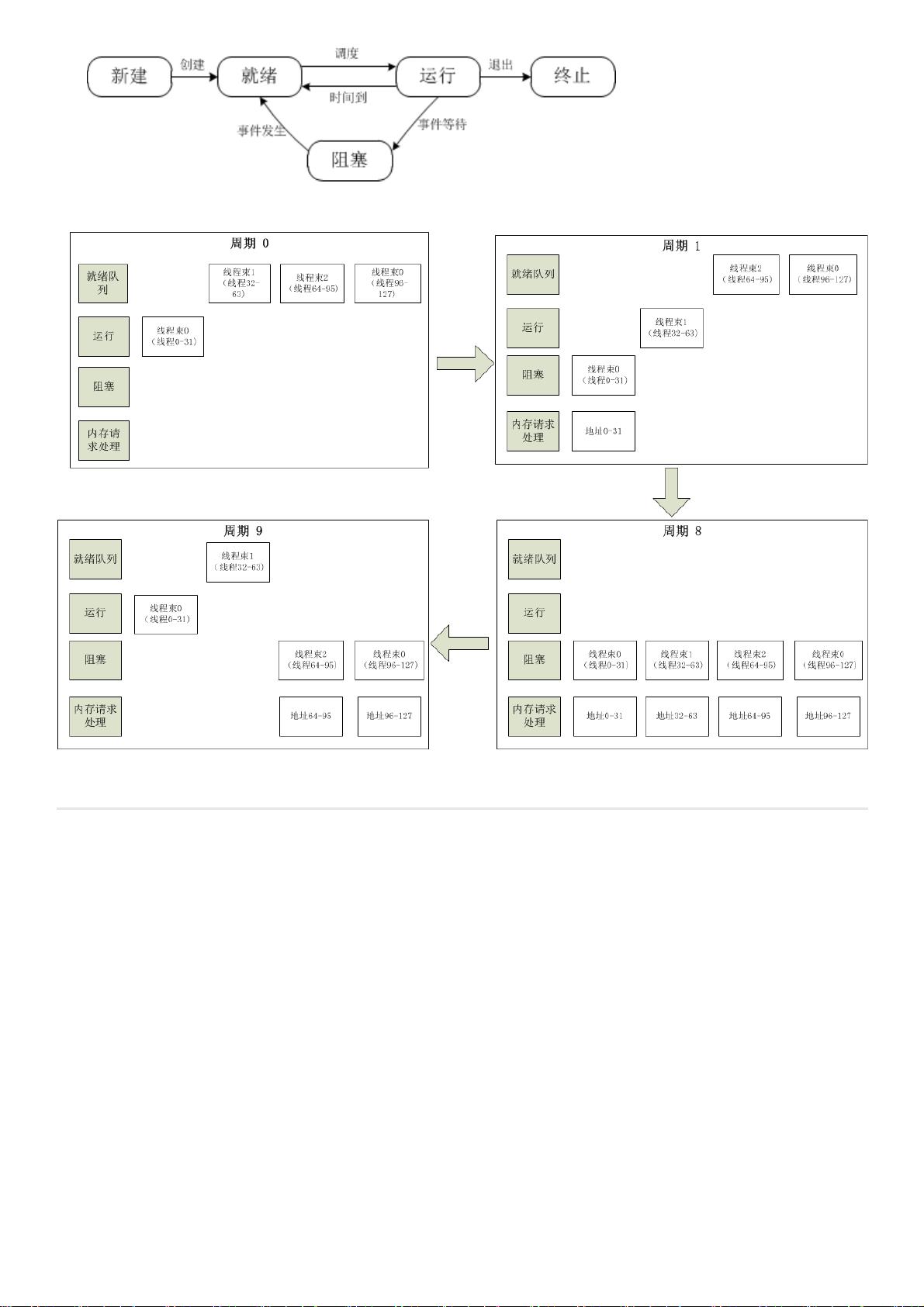

CUDA架构的核心是SIMT(单指令多线程)多处理器设计。GPU芯片由一组SIMT多处理器组成,每个多处理器内部包含多个标量处理器,用于执行不同的线程。这种架构实现了MIMD(多指令多数据)的异步并行机制,允许每个线程独立执行指令并维护自己的状态。

在硬件层面,每个多处理器配备有不同类型的芯片存储器:

1. 本地寄存器(Registers):每个处理器有一组32位寄存器,用于存储中间计算结果。

2. 共享存储器(Shared Memory):所有标量处理器共享,提供并行数据交换的能力。

3. 只读固定缓存(Constant Cache):加速从固定存储器的只读区域读取操作。

4. 只读纹理缓存(Texture Cache):优化从纹理存储器空间的读取,常用于图形处理。

通过这样的架构,CUDA使得开发者可以直接利用GPU的强大并行计算能力,执行非图形计算任务,比如科学计算、机器学习和大数据分析等。CUDA编程模型使得程序员可以利用C/C++等高级语言直接编程,降低了GPU编程的复杂度,极大地拓展了GPU的应用范围。

总结来说,CUDA架构是NVIDIA为了解决GPU在通用计算中的限制而设计的一种并行计算框架。它通过SIMT多处理器和丰富的芯片存储器资源,提供了高效的数据并行处理能力,使得GPU能够胜任更为复杂的计算任务,而不仅仅局限于图形渲染。

2023-06-21 上传

2023-06-25 上传

2024-01-02 上传

2023-07-29 上传

2023-06-27 上传

2023-08-01 上传

old8xp

- 粉丝: 0

- 资源: 4

最新资源

- MATLAB实现小波阈值去噪:Visushrink硬软算法对比

- 易语言实现画板图像缩放功能教程

- 大模型推荐系统: 优化算法与模型压缩技术

- Stancy: 静态文件驱动的简单RESTful API与前端框架集成

- 掌握Java全文搜索:深入Apache Lucene开源系统

- 19计应19田超的Python7-1试题整理

- 易语言实现多线程网络时间同步源码解析

- 人工智能大模型学习与实践指南

- 掌握Markdown:从基础到高级技巧解析

- JS-PizzaStore: JS应用程序模拟披萨递送服务

- CAMV开源XML编辑器:编辑、验证、设计及架构工具集

- 医学免疫学情景化自动生成考题系统

- 易语言实现多语言界面编程教程

- MATLAB实现16种回归算法在数据挖掘中的应用

- ***内容构建指南:深入HTML与LaTeX

- Python实现维基百科“历史上的今天”数据抓取教程