双处理器嵌入式容错实时系统设计与软件容错关键

98 浏览量

更新于2024-08-31

收藏 237KB PDF 举报

"嵌入式系统/ARM技术中的嵌入式双机容错实时系统的设计"

本文探讨了嵌入式系统特别是基于ARM技术的实时容错系统设计,着重于提高系统的可靠性和鲁棒性。在容错实时系统的研究中,有两个核心要点:一是优化实时调度算法,以确保在正常或异常情况下,实时任务都能在预定时间内得到正确处理;二是将传统的冗余容错策略应用到实时系统中,以应对硬件和软件故障。

在当前的嵌入式系统中,软件故障导致的失效比例高达65%,远超硬件故障的8%,因此软件容错能力成为了决定系统可靠性的重要因素。为了解决这一问题,文中提出了一个基于双处理器的实时嵌入式容错系统架构。这个架构利用多处理器系统,实现了处理器间的通信,并且在硬件、操作系统和应用软件层面进行了无缝集成的软件容错设计,旨在整体上提升系统可靠性。

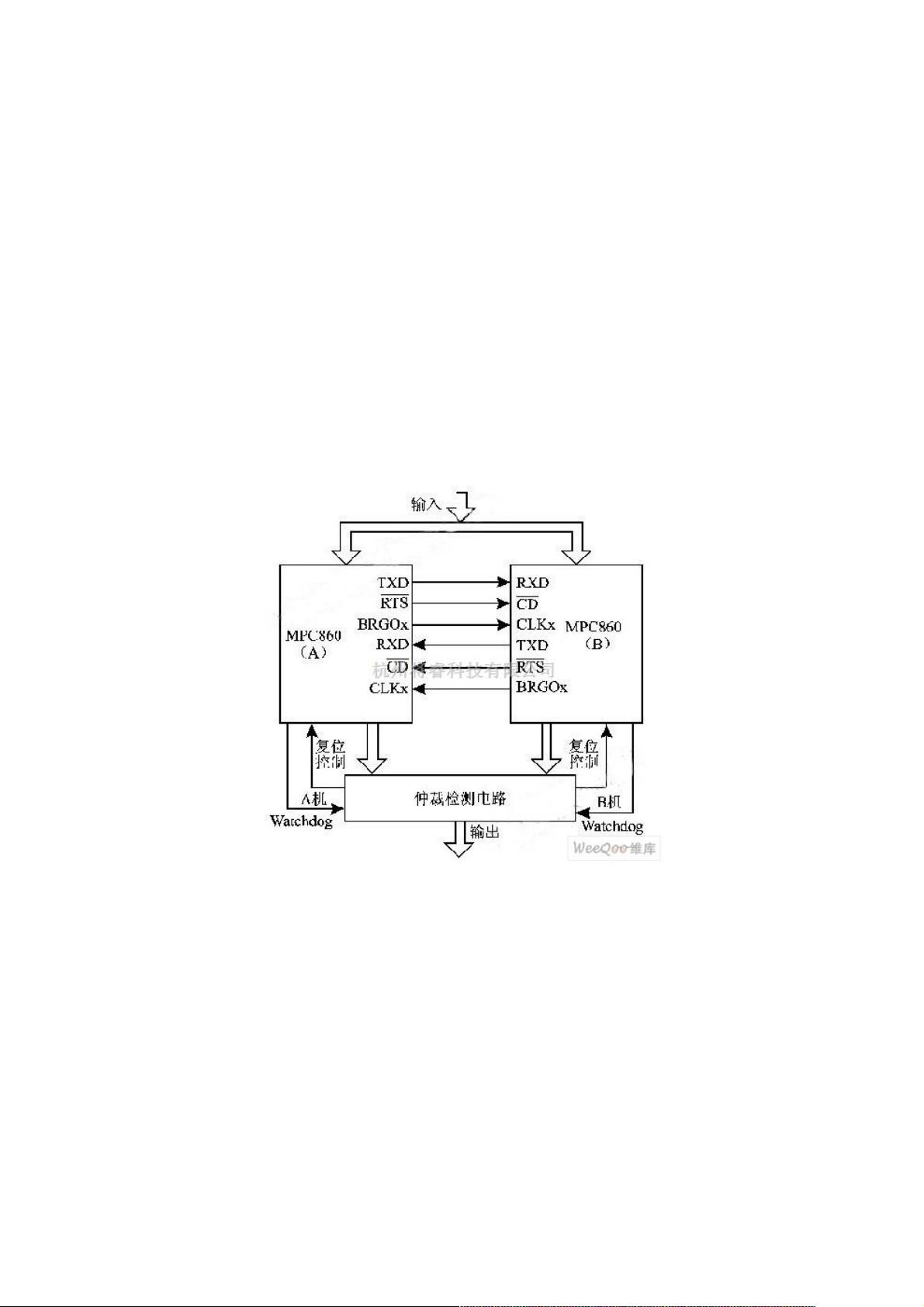

该双机容错实时系统的体系结构如图1所示,包括两台独立的处理机A和B,每台都有自己的外围控制逻辑和外设,避免了资源竞争,增强了系统稳定性。两台机器通过特定的仲裁检测电路进行比较和故障检测。系统运行状态分为两种:正常状态下,A机为主系统,B机为备用,A机的输出作为系统结果,运行到指定点会将日志发送给B机进行同步;当A机发生故障时,B机可以接管并继续运行,保证关键任务的连续执行。

此外,实时调度算法的改进是关键,它需要保证在任何情况下都能有效分配系统资源,优先处理高优先级任务,同时考虑到错误情况下的任务重调度。这种双机系统通过冗余设计,使得即使在单个处理器故障时,系统仍能继续运行,降低了因故障导致的服务中断风险。

在软件容错设计方面,通常包括错误检测、故障隔离、恢复机制和状态备份等策略。例如,使用冗余代码进行错误检测,通过心跳信号监测系统组件的状态,以及设计故障切换逻辑,确保在检测到故障时能够快速无损地切换到备用系统。

在硬件层面,采用冗余设计,如冗余电源、冗余存储和冗余网络接口等,以提高硬件的可用性。同时,通过硬件级别的故障预测和预防措施,可以进一步增强系统的稳定性。

嵌入式系统/ARM技术中的嵌入式双机容错实时系统设计是一种有效的解决方案,它结合了硬件冗余和软件容错,以确保在各种异常情况下,关键任务的执行质量和实时性不受影响,从而提高整个系统的可靠性和安全性。这对于那些对系统稳定性要求极高的应用场景,如航空航天、医疗设备、交通控制系统等,具有极大的价值。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2020-12-10 上传

2020-12-07 上传

2020-12-13 上传

2020-11-07 上传

2020-11-07 上传

2020-11-11 上传

weixin_38603936

- 粉丝: 6

- 资源: 904

最新资源

- capistrano-memcached:Capistrano 任务用于自动和合理的内存缓存配置

- lab33-CAP-APWM,c#医院缴费系统源码,c#

- HBD-Chrome-Extension-crx插件

- IO_2020_2021_QuadclubApp:罗兹大学软件工程课程中实施的项目

- qr-code-generator-chrome-extension:Chrome扩展程序-一键QR代码生成器

- 美味

- StudentManagementSystem

- 龙卷风图:这会根据指定的灵敏度值创建龙卷风图。-matlab开发

- abc,c#bs框架源码,c#

- jerseywildfly:Projeto utilizando实现工具Eclipse Jersey https:eclipse-ee4j.github.io

- Create-Your-Own-Image-Classifier-Project-Submission:创建自己的图像分类器项目提交

- AzureDevOps

- distractor_neurons

- poject1:项目描述

- GCMT:Gentoo集群管理工具-开源

- stm32motor,c#开启动画源码,c#