Lattice ECP3 FPGA内存使用指南详解

需积分: 10 126 浏览量

更新于2024-07-17

收藏 4.62MB PDF 举报

本指南是针对Lattice ECP3系列FPGA器件的内存使用情况而编写的,旨在帮助设计工程师在iCE40 LEVER®平台上有效集成基于EBR(Embedded Block RAM)和PFU(Processing Function Unit)的内存。Lattice ECP3架构以其丰富的内存资源而闻名,特别适合对内存密集型应用。

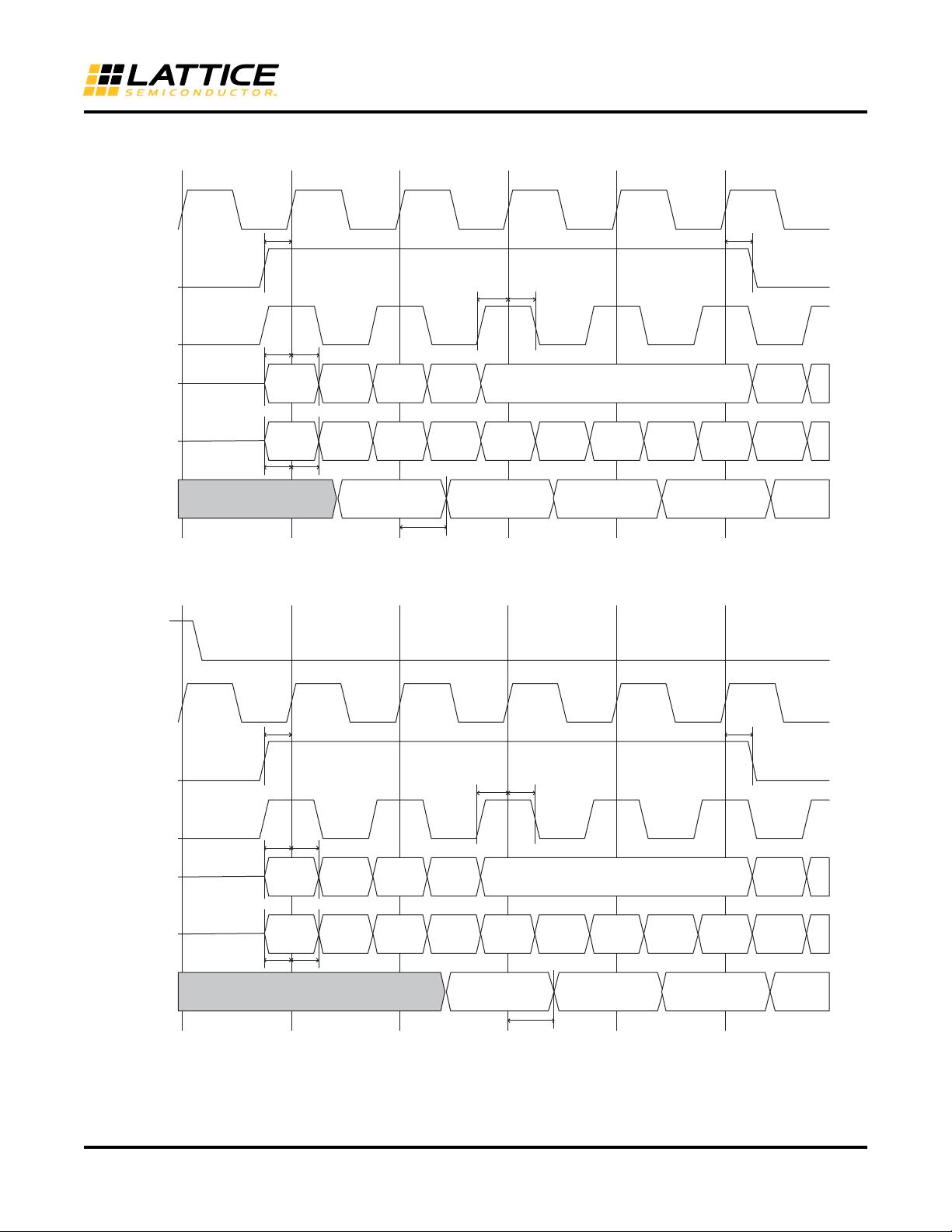

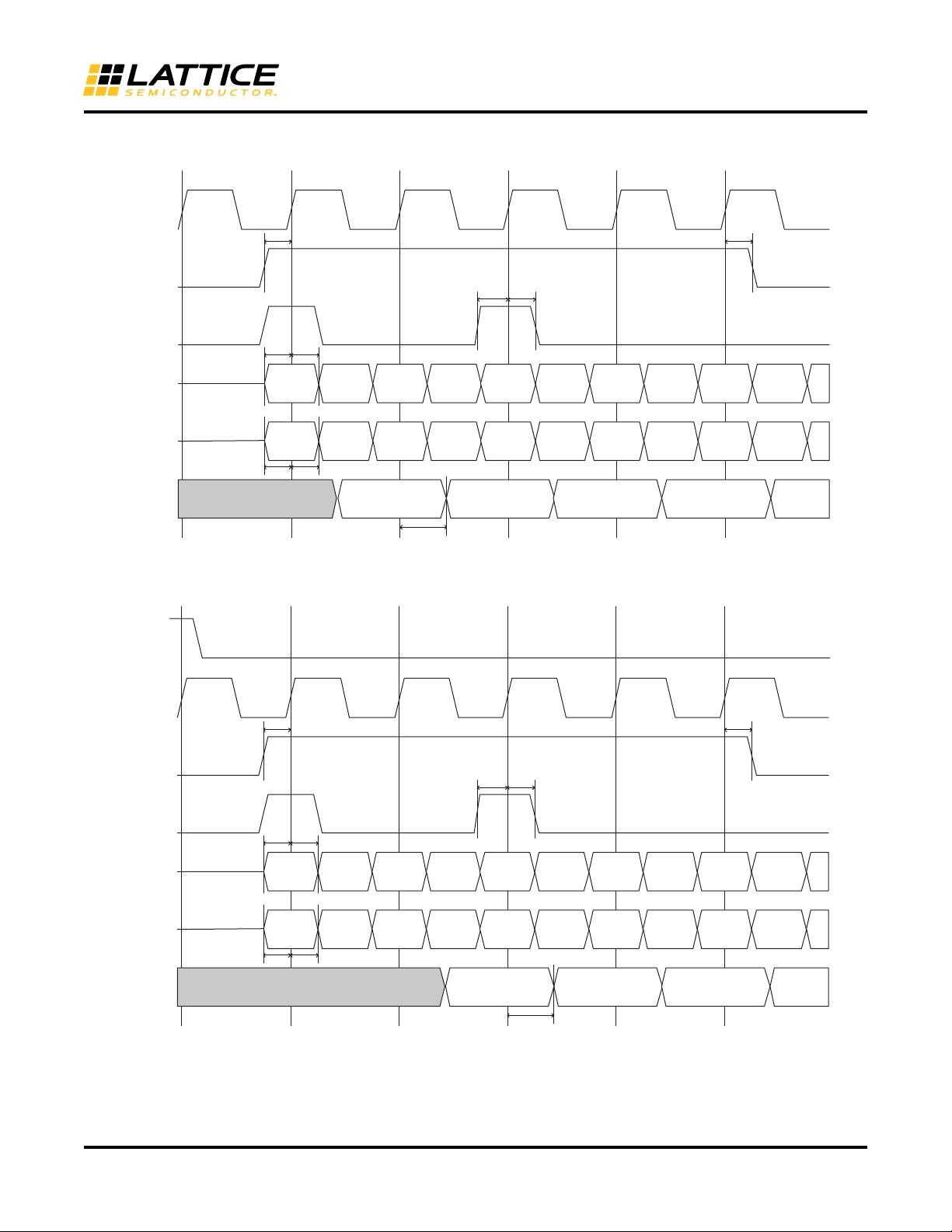

EBR作为核心组成部分,提供了SysMEM™嵌入式块RAM,可以单独使用,也可与分布式PFU内存相结合。单端口RAM、双端口RAM、伪双端口RAM以及只读存储器(ROM)等不同类型的内存可以通过EBR构建。LUTs(Look-Up Tables)和PFUs能够实现分布式单端口RAM、双端口RAM和ROM的功能。此外,设备内部逻辑可以灵活配置这些内存单元,使其具备FIFO(First-In-First-Out)和其他存储类型的能力。

该技术笔记详细介绍了如何优化EBR的配置,包括但不限于内存容量规划、数据传输速度控制、地址映射策略以及潜在的功耗优化。它还会涵盖内存错误校验、一致性管理以及与其他片上功能(如定时器、计数器)的协同工作。此外,为了充分利用Lattice ECP3的性能潜力,设计师需要熟悉其内存带宽限制、时序参数和接口规范。

请注意,所有的规格和信息都可能随着技术和市场需求的变化而更新,因此在设计过程中,务必参考最新的技术文档,如Lattice Semiconductor Corp. 的官方技术通知TN1179,日期为2014年4月,网址为www.latticesemi.com/tn1179_01.8。同时,确保遵循所有商标、专利和免责声明,这些信息可在Lattice半导体公司的官方网站的法律页面上找到。

本指南不仅涵盖了内存设计的最佳实践,还提供了关于如何在Lattice ECP3 FPGA中实现高效内存布局和管理的关键技术细节,对于从事此类设计的工程师来说,是不可或缺的参考资料。

2018-09-13 上传

190 浏览量

151 浏览量

116 浏览量

2022-06-15 上传

105 浏览量

xl@666

- 粉丝: 400

最新资源

- JAD工具:Java反编译神器的实用教程

- Delphi多线程控件BmdThread_1.9的安装与测试指南

- Flash猜拳游戏源码分享 - 剪刀石头布

- Java编程课程中辐射监测任务1解析

- 深入探究ASP.NET同学录系统设计与实践

- Windows Server 2003双机热备技术实施教程

- 掌握kindeditor使用技巧,实例操作解析

- mimos:打造hapi生态系统的Mime数据库界面

- JqGrid在VS2010和MVC下的应用示例

- C#实现USB HID设备通信的方法及实例

- YangDiDi-bilibili.github.io网站CSS技术解析

- Eclipse贪吃蛇游戏插件简易安装指南

- MATLAB实现:非线性方程组的无导数解算器开发

- 揭秘:超级玛丽游戏源码的神秘面纱

- Scribd文档去划线解决方案及开发指南

- 单片机红外线控制数码管显示与蜂鸣器