FPGA设计优化:乒乓操作、串并转换与流水线策略

需积分: 10 40 浏览量

更新于2024-09-12

收藏 111KB PDF 举报

“FPGA设计的四种常用思想与技巧,包括乒乓操作、串并转换、流水线操作和数据接口同步化,旨在提升FPGA/CPLD设计效率。”

在FPGA(现场可编程门阵列)和CPLD(复杂可编程逻辑器件)的设计中,运用特定的思想和技巧可以显著提高设计效率和性能。以下是对这四种常用设计方法的详细解释:

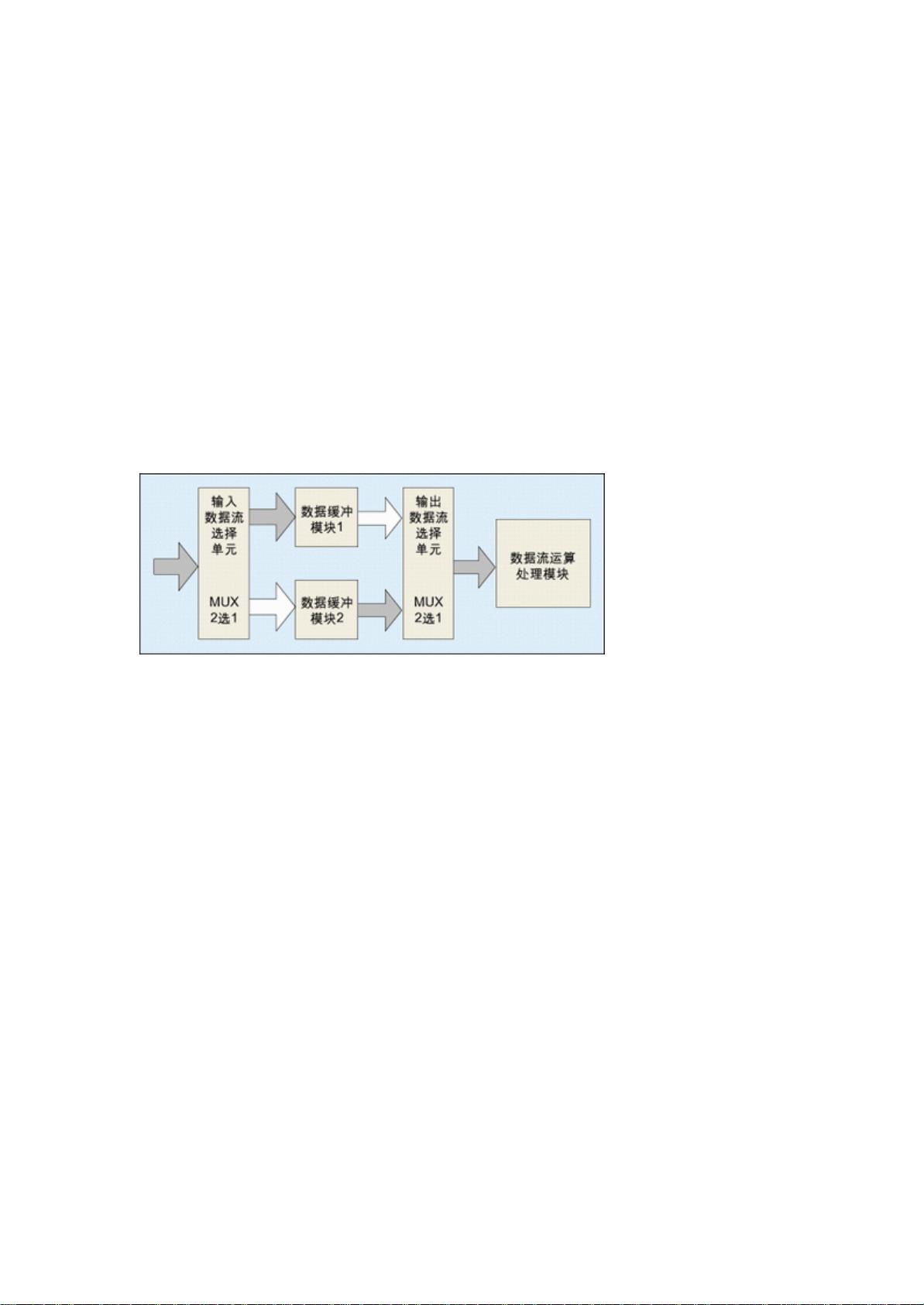

1. **乒乓操作**:

乒乓操作是一种巧妙的数据流控制技术,常用于需要连续处理数据的场景。它利用两个或多个数据缓冲区交替存储和处理数据,使得数据处理不间断,如同乒乓球在两个拍子之间连续弹跳。例如,数据首先被存储在缓冲区1,然后在下一个时钟周期转移到缓冲区2,同时缓冲区1中的数据被处理。这样,数据处理与新的数据接收可以同时进行,提高了系统的吞吐量。在需要延迟处理或者流水线计算的应用中,乒乓操作尤为有效。

2. **串并转换**:

串并转换是另一种关键的设计技巧,主要用于解决速度和带宽问题。在串行数据传输中,数据一位接一位地传输,而并行数据则是多位同时传输。在FPGA设计中,将串行数据转换为并行数据可以显著提升数据处理速度。例如,在高速通信接口中,串行到并行转换器( Serializer/Deserializer,SerDes)经常被用来增加数据传输速率。反之,当系统需要并行数据转换为串行以适应低速接口时,也会使用并行到串行转换。

3. **流水线操作**:

流水线操作是基于时间分片的思想,将复杂的处理任务分解为多个阶段,每个阶段在一个独立的硬件单元中并行执行。这种方式使得在每个时钟周期内可以处理更多的数据,从而提高系统性能。乒乓操作就是流水线设计的一个实例,它通过连续的数据流动实现数据处理的流水线化。

4. **数据接口同步化**:

在多模块系统中,数据接口同步化至关重要,因为不同模块可能运行在不同的时钟域,导致数据同步问题。同步化设计确保了数据在不同模块间准确无误地传输,避免时钟偏移引起的错误。通常使用同步器(如D-flip-flops)或锁存器来实现跨时钟域的数据传递,以确保数据在正确的时间点被采样。

理解和熟练运用这些设计思想与技巧,对于FPGA/CPLD设计师来说至关重要。它们可以帮助优化系统资源,提高处理速度,减少设计的复杂性和错误,从而在项目开发中取得更好的成果。在实际工作中,根据具体的应用需求灵活组合和运用这些方法,可以设计出更加高效、可靠的FPGA/CPLD解决方案。

378 浏览量

2010-05-26 上传

114 浏览量

2021-09-18 上传

2023-02-27 上传

2023-02-26 上传

2023-02-26 上传

2012-10-20 上传

鬼谷清泉

- 粉丝: 5

最新资源

- 深入探究JavaScript中的多边形布尔运算技术

- 最新版本挖掘鸡4.02:强大压缩工具介绍

- 基于8255/8253/8259芯片的微机原理抢答器设计报告

- C#中文件和文件夹操作详解及常用类

- Xamarin Android 富交互NavigationTabBar组件指南

- Keil MDK进阶技巧与实战解析

- 清风123域名出售管理系统:全技术栈源代码

- 悠索科技绩效考核评估系统:自定义功能与数据管理

- XJYChart:iOS图表框架的强大特性与动画支持

- Java通讯录管理系统:课程设计完整文档

- Kokpit:通过Android控制ARDrone 2.0四旋翼无人机

- Simple-Http-Listener-PCL 6.0:Xamarin表单的新一代跨平台Http Server

- 安卓古筝App体验:动听旋律与传统艺术的完美结合

- Android中assets下9patch图编译方法详解

- TEC2000仿真软件:微体系结构模拟与教学应用

- 策略模式C++实现与VC2005编译测试