Verilog入门:模块与基本结构

需积分: 41 7 浏览量

更新于2024-09-08

2

收藏 298KB PDF 举报

Verilog入门教程深入讲解了HDL(Hardware Description Language)语言的基础知识,特别是针对模块(module)的介绍。模块是Verilog设计的核心概念,它是功能或结构的描述单元,通过外部端口(port list)与其他模块交互。模块由以下几个关键部分组成:

1. **模块定义**:使用`module`关键字声明模块名称,如`module HalfAdder(A,B,Sum,Carry);`,其中端口列表包含输入(input)、输出(output)和可能的混合类型(inout)。

2. **信号声明**:包括寄存器(reg)、线网(wire)、参数(parameter)等,它们定义了模块内部的变量和数据类型。例如,`reg Sum; wire Carry;` 表示Sum是寄存器,Carry是线网。

3. **声明与语句**:Verilog使用`declaration statements`来说明设计的逻辑结构,如`assign`语句用于描述数据流行为,`always`或`initial`语句用于时间敏感和初始化行为。在本例中,`assign Sum = A^B;` 和 `assign Carry = A & B;` 分别定义了半加器的逻辑。

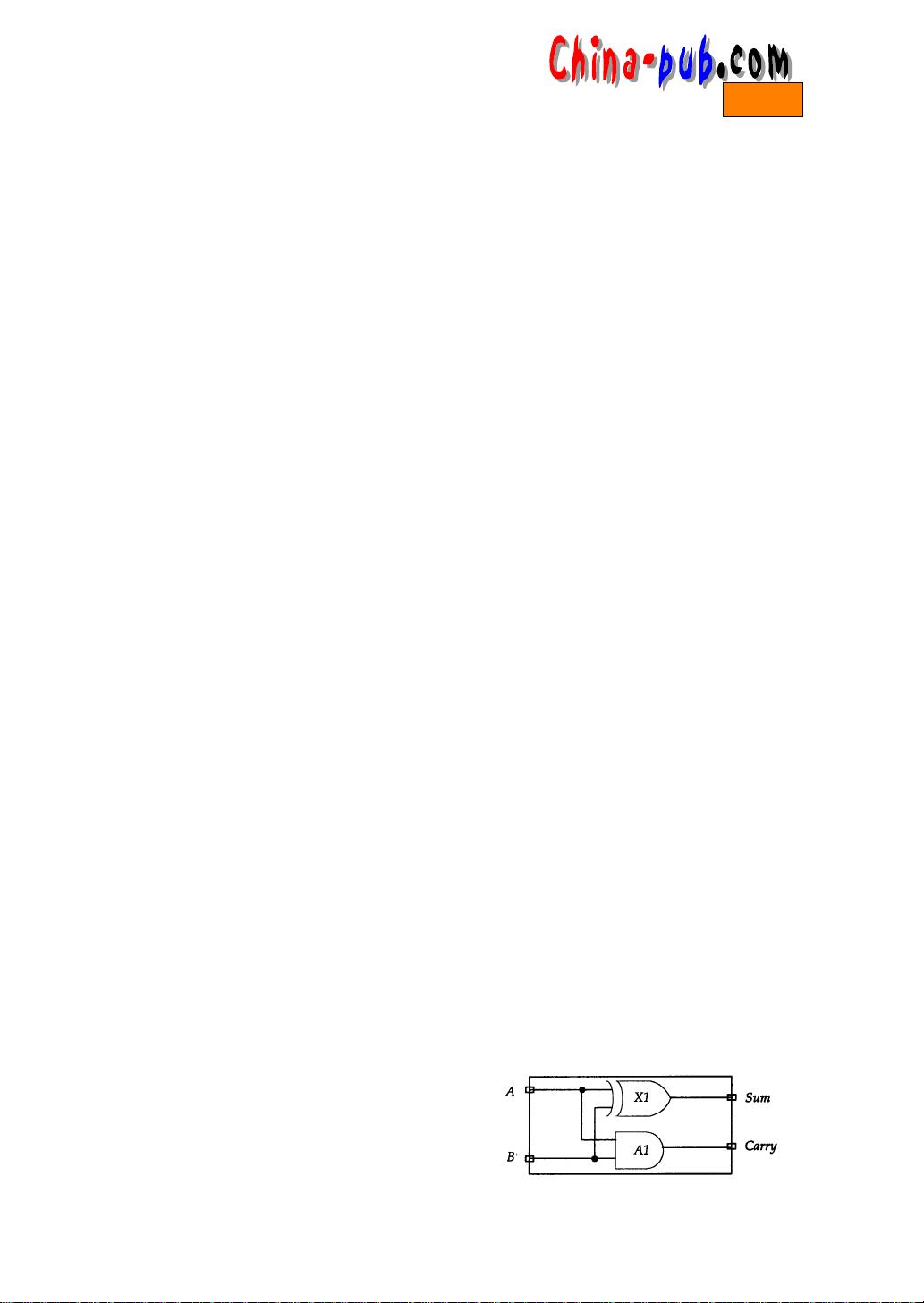

4. **并发与顺序**:模块内的连续赋值语句是并发的,即它们可以并行执行,但实际执行顺序取决于其他条件,比如硬件实现的时序。图2-1展示了如何使用`assign`语句来模型化半加器的逻辑。

5. **模块实例化**:模块可以被其他模块调用,提供复用性和模块化的设计。模块实例化通常出现在其他模块的`always`或`initial`语句中,如`half_adder U1(A,B,Sum,Carry);`。

6. **代码组织**:为了保持代码清晰和可读性,建议将声明部分放在语句之前,并遵循一定的命名规则和模块结构,如将所有的`initial`和`always`块集中在一起。

通过学习这些基础概念,初学者可以逐步掌握Verilog语言,进行简单的电路设计和模块化编程。随着对模块、数据流和时序控制的理解加深,将能够构建更复杂的系统。后续章节可能会进一步探讨高级语法、仿真、验证和综合等内容,帮助读者提升Verilog设计能力。

126 浏览量

338 浏览量

264 浏览量

269 浏览量

600 浏览量

点击了解资源详情

shang0209

- 粉丝: 1

最新资源

- Sencha Architect:HTML5快速开发神器

- 深入探索编译原理中的语法树实现方法

- 深入理解ACE框架与设计模式的应用

- 掌握Jupyter Notebook核心技巧

- Loxdown: TypeScript实现的Lox静态类型变体

- C语言实现3DES加密算法教程

- Android仪表盘效果的实现方法及代码解析

- HDD Recovery Pro4.1:全面硬盘数据恢复解决方案

- 易语言编程初学者十例源码解析

- 网页制作:精通表单设计与应用

- 掌握Canny边缘检测算法的实践与应用

- 掌握边缘Canny算法实现高效图像边缘提取

- 2Tale Writer's Portal的轻量级Web文字处理器开发

- Tryséuma学校技术课程:全面提升前端与后端技能

- VB开发多功能透明时钟程序及其自定义功能介绍

- 辰华CHI760E电化学工作站软件实用版介绍与安装