LatticeXP FPGA与IP驱动DDR读写控制的嵌入式系统设计验证

194 浏览量

更新于2024-08-30

收藏 260KB PDF 举报

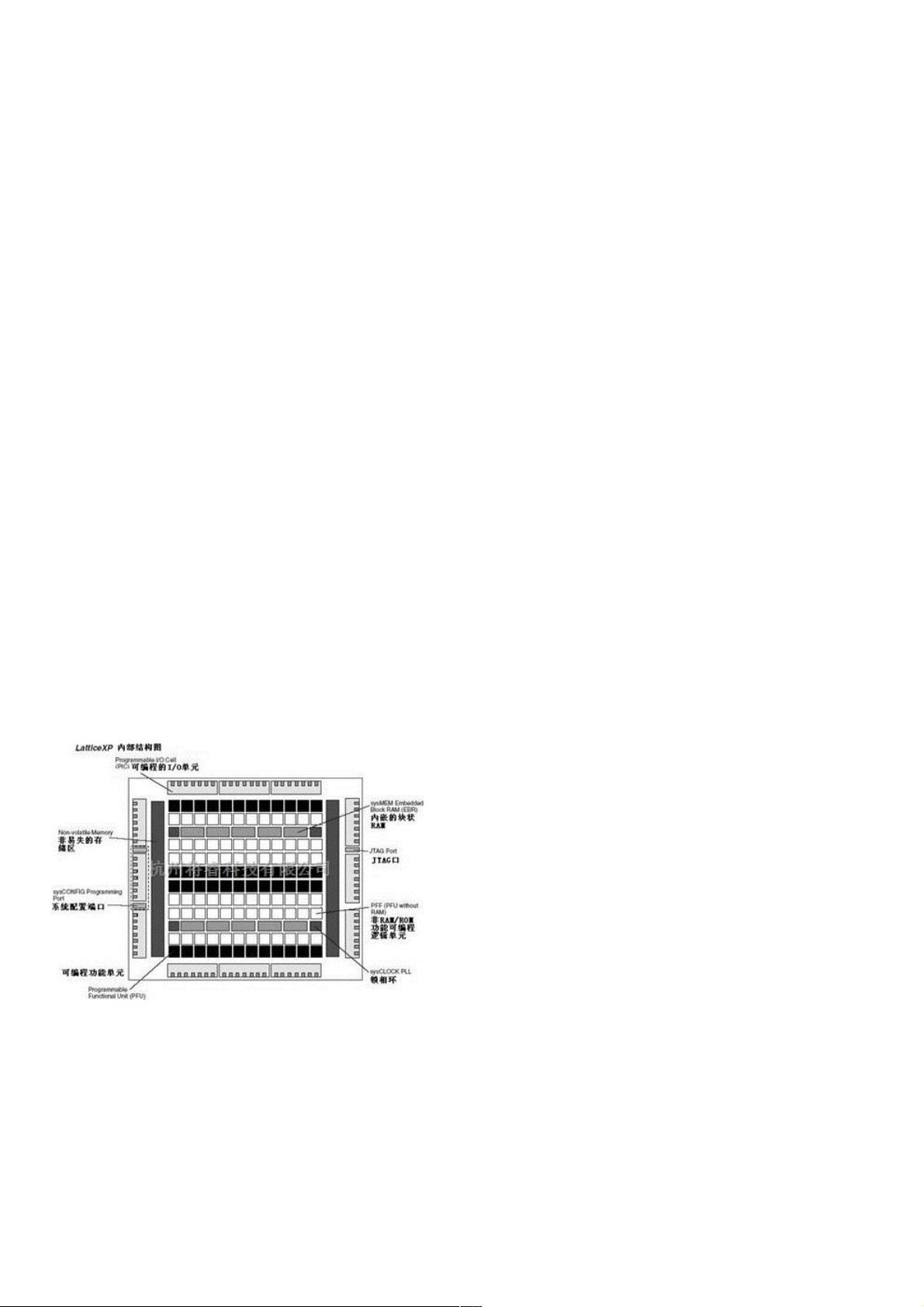

本文主要探讨了在EDA/PLD(电子设计自动化/可编程逻辑器件)技术中,如何利用FPGA(现场可编程门阵列)知识产权(IP)有效地设计和验证DDR SDRAM(双倍速率同步动态随机存取存储器)的读写控制功能。LatticeXP系列FPGA被选为实现这一目标的关键平台,因为它提供了必要的硬件资源和兼容DDR SDRAM标准的接口。

在嵌入式系统的发展中,高速处理器的需求推动了对大容量RAM,特别是DDR SDRAM的依赖。由于DDR SDRAM通过在时钟信号的上升和下降沿进行数据传输,实现了双倍的带宽,这使得它在处理如视频监控和图像数据采集这类实时性强的应用中具有显著优势,传统SDRAM已经无法满足这些应用的带宽需求。

设计过程中,DDR SDRAM的操作速度提升意味着控制时序的要求更为严格。同时,DDR内存的工作电压从SDRAM的3.3V降低到2.5V的SSTL-Ⅱ标准,这对设计者提出了额外的挑战。很多处理器不内置DDR SDRAM控制器,因此设计者通常需要在系统中集成专门的控制器,以便微处理器或数字信号处理器能有效控制内存。

FPGA的优势在于其灵活性和高度定制化能力。许多现代FPGA提供了与DDR SDRAM标准兼容的接口,包括SSTL-Ⅱ电气特性以及内置的DDR触发器和锁相环等硬件资源。这些特性使得设计者能够利用预集成的IP模块简化控制器的设计,并确保其性能和可靠性。

文章详细介绍了设计方法,可能包括选择合适的FPGA芯片、理解并适配DDR SDRAM的规格、设计读写控制逻辑、以及进行实际的硬件测试,以验证设计的有效性和稳定性。这样的设计对于提高嵌入式系统的整体性能和功耗效率至关重要。

本研究旨在通过结合LatticeXP系列FPGA和IP,提供了一种高效且可靠的方法,用于解决在嵌入式系统中使用DDR SDRAM时的读写控制问题,这对于推动技术进步和满足现代应用的带宽需求具有实际意义。

2020-11-07 上传

2020-11-07 上传

2020-10-19 上传

2020-11-21 上传

2020-12-09 上传

2020-12-06 上传

2020-11-05 上传

2020-11-30 上传

点击了解资源详情

weixin_38650508

- 粉丝: 6

- 资源: 938

最新资源

- 构建基于Django和Stripe的SaaS应用教程

- Symfony2框架打造的RESTful问答系统icare-server

- 蓝桥杯Python试题解析与答案题库

- Go语言实现NWA到WAV文件格式转换工具

- 基于Django的医患管理系统应用

- Jenkins工作流插件开发指南:支持Workflow Python模块

- Java红酒网站项目源码解析与系统开源介绍

- Underworld Exporter资产定义文件详解

- Java版Crash Bandicoot资源库:逆向工程与源码分享

- Spring Boot Starter 自动IP计数功能实现指南

- 我的世界牛顿物理学模组深入解析

- STM32单片机工程创建详解与模板应用

- GDG堪萨斯城代码实验室:离子与火力基地示例应用

- Android Capstone项目:实现Potlatch服务器与OAuth2.0认证

- Cbit类:简化计算封装与异步任务处理

- Java8兼容的FullContact API Java客户端库介绍