FPGA编程中的跨时钟域信号同步IP设计与解决方案

需积分: 50 112 浏览量

更新于2024-07-20

2

收藏 1.2MB PDF 举报

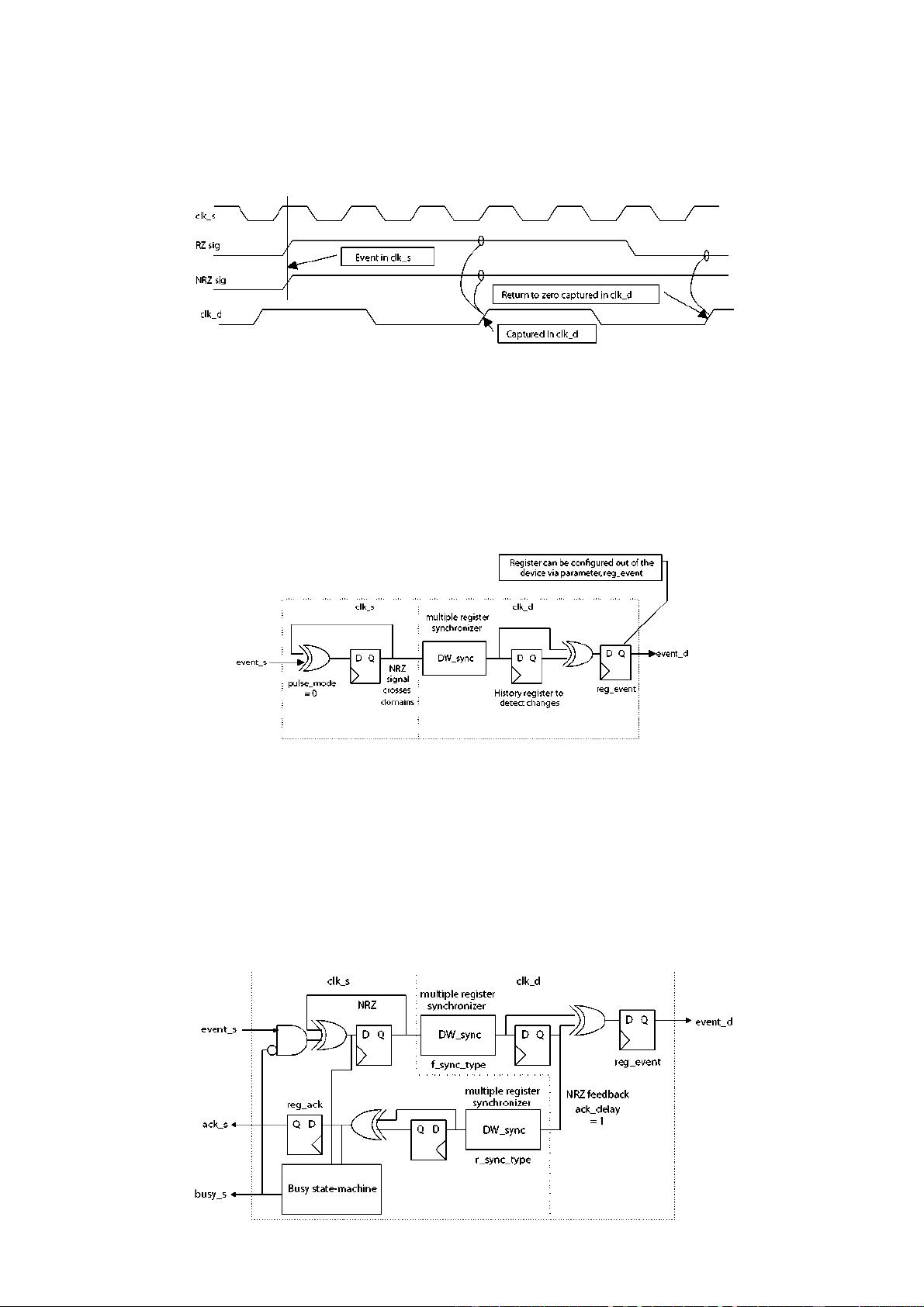

跨时钟域信号同步在FPGA编程实现中是一项关键的技术挑战,本文将深入探讨如何在Synopsys DesignWare IP解决方案中处理这类问题。首先,理解跨时钟域通信是必要的,这通常发生在不同频率或相位的时钟域之间,可能导致数据传输不稳定或错误。FPGA中的时钟同步机制旨在确保各个模块之间的数据流在正确的时间点发生,并保持一致性。

文章中提到的几个主要IP模块包括:

1. VK—DW_sync: 这个模块可能用于实现全局时钟同步,确保所有模块的时钟信号保持在一个共享的参考时钟上,以减少时钟抖动和噪声的影响。

2. #K—DW_pulse_sync, DW_pulseack_sync: 这些模块可能涉及脉冲同步,确保信号的上升沿和下降沿在正确的时钟周期内发生,这对于触发器和数据交换至关重要的信号来说是必不可少的。

3. ³A&ÓK—DW_data_sync: 数据同步IP负责在不同的时钟周期内正确地采样和发送数据,可能是通过锁存、延迟线或者其他数据恢复技术来实现。

4. ¡K—DW_fifo_s2_sf, DW_fifo_2c_df, DW_stream_sync: FIFO(First-In-First-Out)同步接口用于在不同时钟速度的上下文中管理数据流,确保数据在正确的时间被读取和写入。

5. Y*m—DW_reset_sync: 重置同步确保系统在复位期间的同步行为,避免潜在的数据混乱。

6. «5ⶺK—DW_data_qsync_hl, DW_data_qsync_lh: 这些可能是队列同步接口,确保数据在读写操作中的正确顺序和时机。

7. VKãì和u¾: 这些部分可能涉及到时钟控制和管理,例如提供适当的时钟分频或时钟切换功能。

8. ãìu: 可能涉及到高级时钟管理策略,如选择性时钟分配或者时钟树优化。

9. ClocktoQdelay和FFMinimumspecs: 分别是时钟到Q(数据)延迟的测量以及最小特性规格,这些参数对于确定信号传输的最佳时间和性能至关重要。

10. ÉEPfÇ: 这可能是关于设计工具中时钟和数据流分析的功能,帮助工程师识别和解决潜在的时序问题。

跨时钟域信号同步的IP解决方案是FPGA设计中的核心组成部分,它涉及到精确的时钟管理、数据同步、接口设计以及工具支持。理解并有效利用这些IP可以显著提高系统的可靠性和性能。在实际应用中,设计师需要根据具体的设计需求选择合适的同步机制,并进行详细的时序分析和验证。

2019-09-05 上传

2023-07-19 上传

2023-11-04 上传

2023-05-09 上传

2023-10-19 上传

2023-07-18 上传

2023-07-14 上传

qq_26657811

- 粉丝: 1

- 资源: 9

最新资源

- 前端面试必问:真实项目经验大揭秘

- 永磁同步电机二阶自抗扰神经网络控制技术与实践

- 基于HAL库的LoRa通讯与SHT30温湿度测量项目

- avaWeb-mast推荐系统开发实战指南

- 慧鱼SolidWorks零件模型库:设计与创新的强大工具

- MATLAB实现稀疏傅里叶变换(SFFT)代码及测试

- ChatGPT联网模式亮相,体验智能压缩技术.zip

- 掌握进程保护的HOOK API技术

- 基于.Net的日用品网站开发:设计、实现与分析

- MyBatis-Spring 1.3.2版本下载指南

- 开源全能媒体播放器:小戴媒体播放器2 5.1-3

- 华为eNSP参考文档:DHCP与VRP操作指南

- SpringMyBatis实现疫苗接种预约系统

- VHDL实现倒车雷达系统源码免费提供

- 掌握软件测评师考试要点:历年真题解析

- 轻松下载微信视频号内容的新工具介绍