华为静态时序分析教程

需积分: 49 155 浏览量

更新于2024-07-19

1

收藏 957KB PDF 举报

"华为静态时序分析"

静态时序分析(Static Timing Analysis,简称STA)是集成电路设计中的一个重要步骤,主要用于评估数字电路的时序性能。它通过分析电路中信号传播延迟,确定电路是否满足预定的时钟周期要求,即是否满足时序约束。华为作为全球领先的ICT解决方案供应商,在其芯片设计过程中也会广泛应用静态时序分析。

华为时序分析的资料通常会包含以下几个方面:

1. **基本概念**:静态时序分析基于门级或网表级别的电路模型,无需运行实际的电路模拟,就能计算出电路的最坏情况延迟。这种分析方法快速且准确,对于大规模集成电路的设计至关重要。

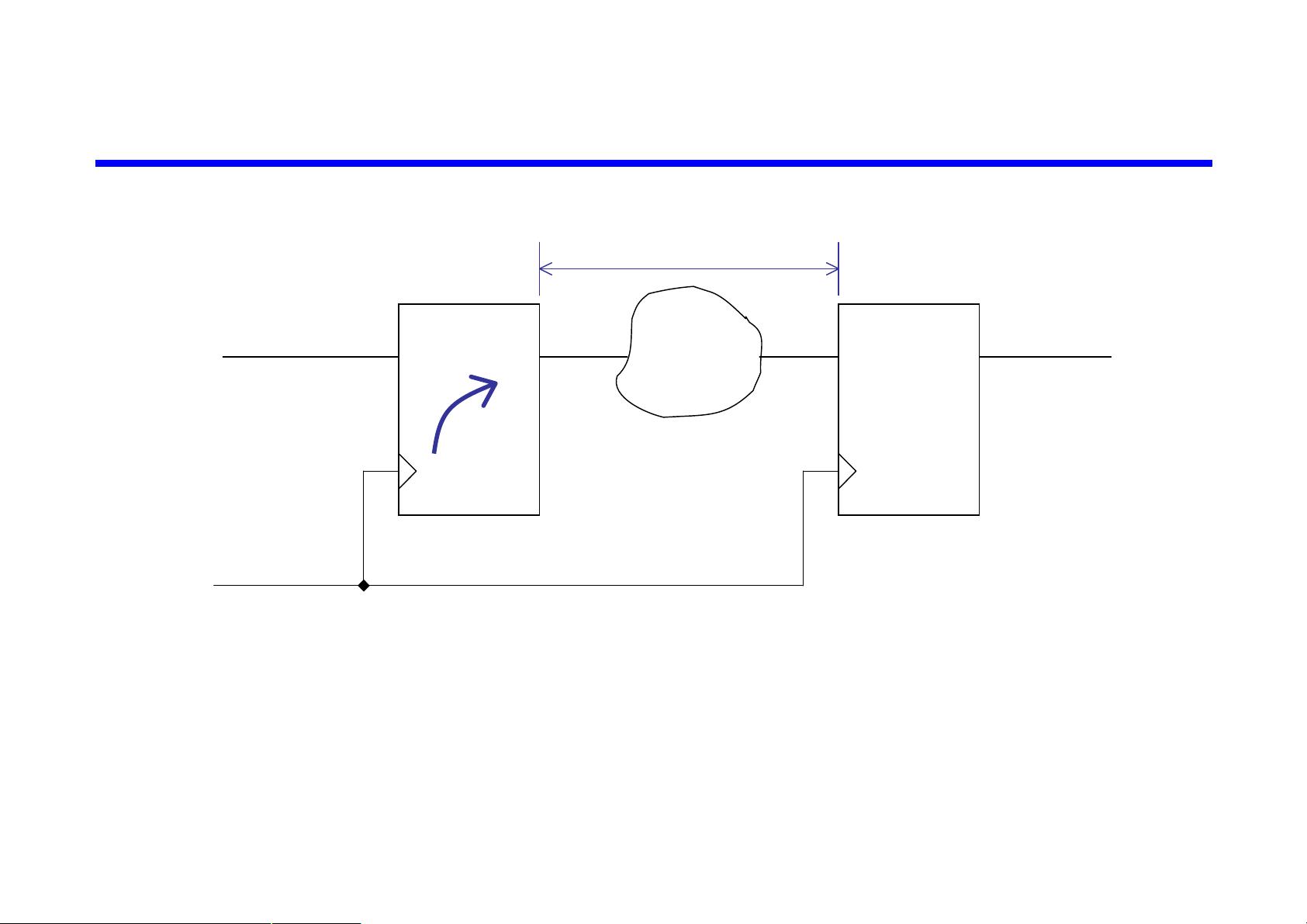

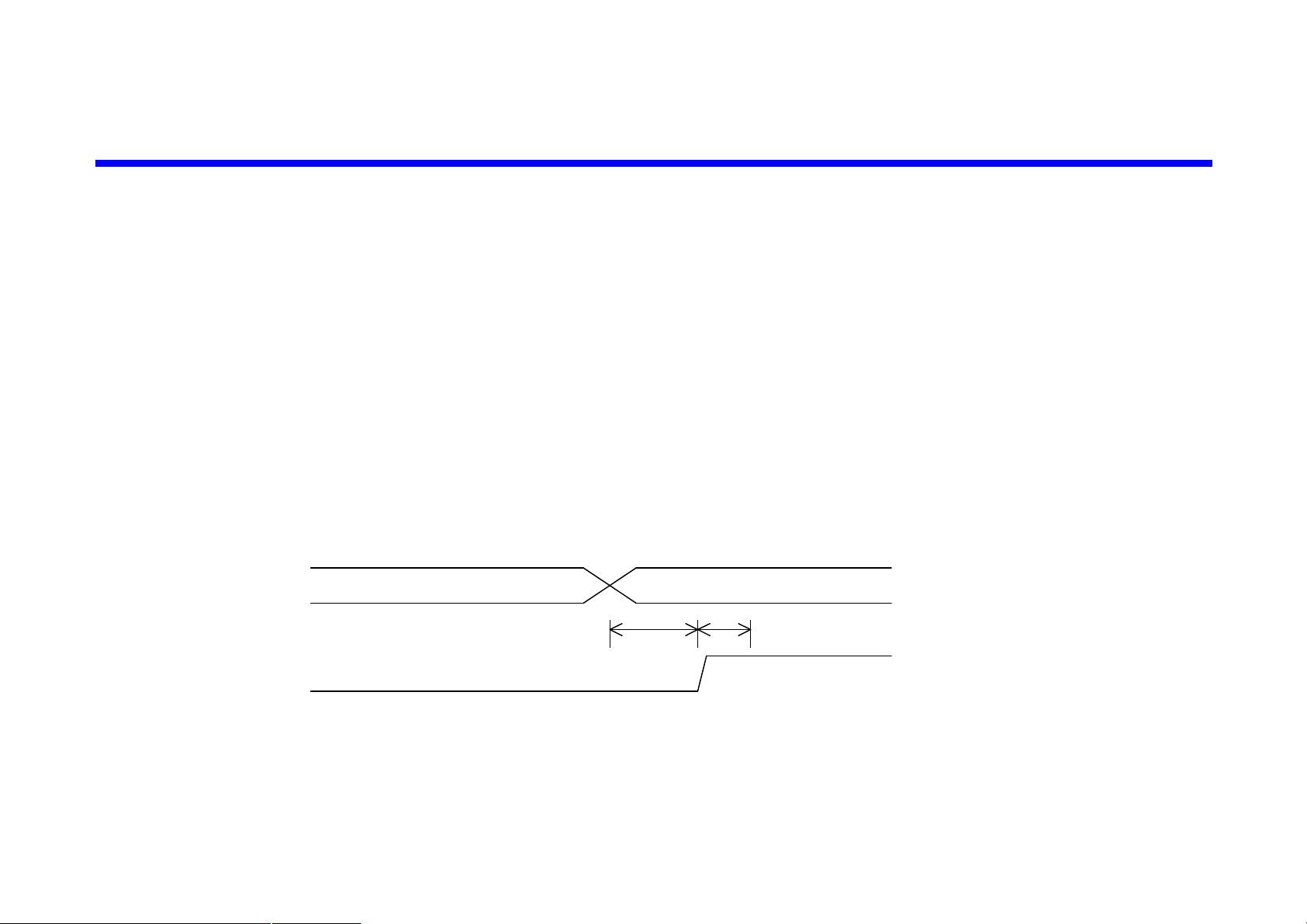

2. **时序路径**:时序路径是从触发器到另一个触发器的信号传输路径,包括组合逻辑和时钟路径。静态时序分析的目标是确定这些路径中最慢的,确保整个系统能够在指定的时钟周期内稳定工作。

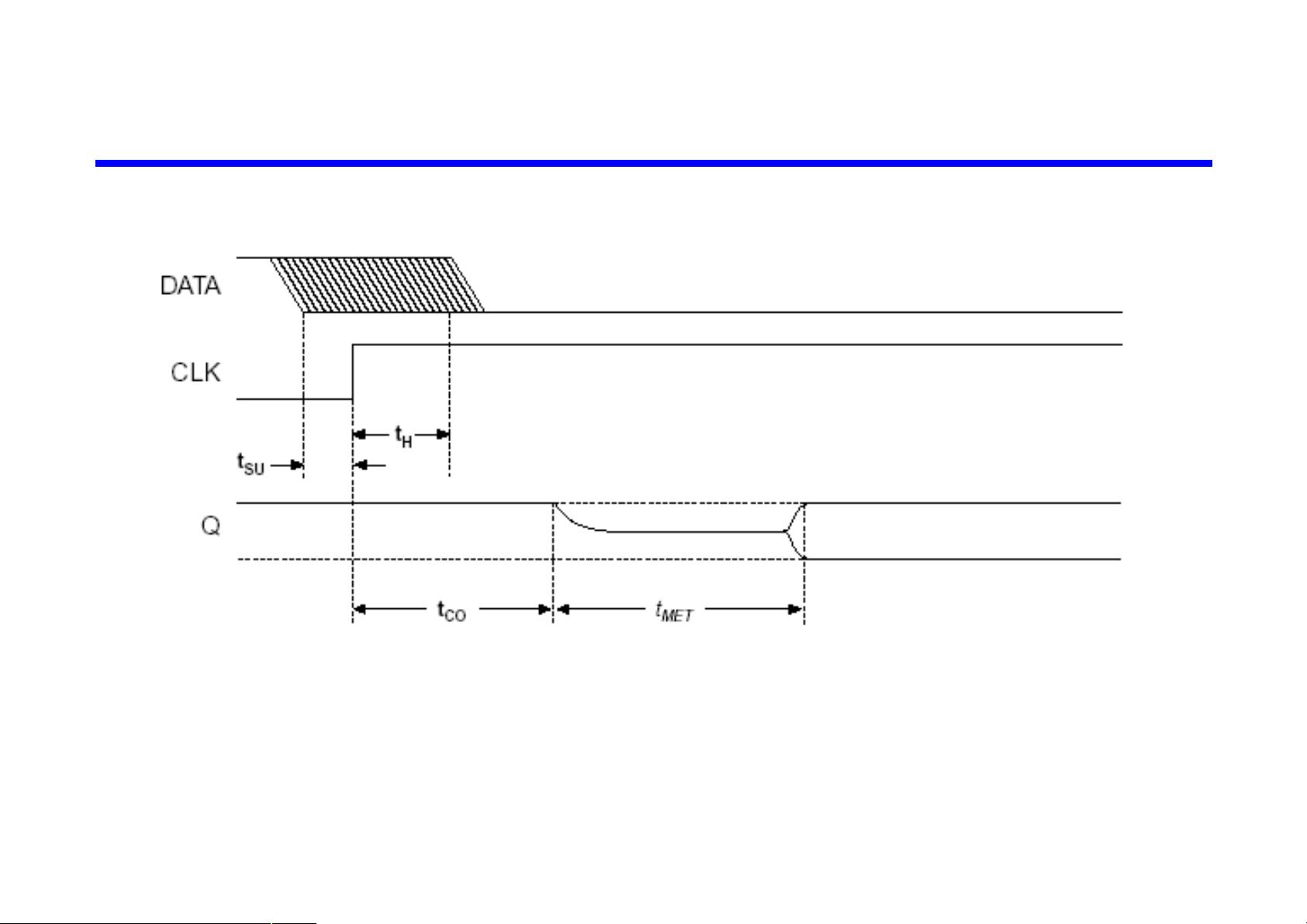

3. **时序模型**:时序分析中涉及到的模型包括最大延迟(Max Delay)和最小延迟(Min Delay),以及路径的建立时间(Setup Time)和保持时间(Hold Time)。理解这些模型对于优化电路性能至关重要。

4. **工具应用**:华为可能使用的工具有Synopsys的PrimeTime、Mentor Graphics的SST Velocity等。这些工具能够自动进行时序分析,提供详细的报告,帮助工程师识别和解决时序问题。

5. **时序约束**:在进行静态时序分析前,需要定义时序约束,如时钟周期、时钟Skew等,这些约束指导着分析过程并决定设计是否满足性能要求。

6. **时序优化**:分析结果可能显示某些路径过慢,这时就需要进行时序优化,可能包括门级优化、布线优化或者改变时钟分配,以缩短关键路径的延迟。

7. **FPGA与ASIC的差异**:在FPGA设计中,由于其可编程性,时序分析和优化有其特殊性。而ASIC设计则更注重前向工程流程,需要在设计早期就进行严格的时序分析,以确保流片成功。

8. **技术细节**:华为的资料可能会涵盖如何设置和使用各种分析选项,如何解读分析报告,以及如何处理时序违规(Timing Violation)等问题。

通过深入理解和掌握这些知识点,无论是初学者还是经验丰富的工程师,都能更好地应对华为静态时序分析的挑战,从而提升芯片设计的效率和质量。

111 浏览量

点击了解资源详情

点击了解资源详情

222 浏览量

153 浏览量

点击了解资源详情