AN143

Rev 0.9 | Page 8/40

1.4.1 Application scene 1: Receive the data at RX

RX FIFO is used more directly. Clear it when you enter RX every time. Enter RX and fill them if the data is

received (Detect the Sync Word successfully). MCU can achieve the following several operations according to

the interrupt. After you have finished, you cannot use it. Send FIFO_CLR_RX to clear before you receive it

next time.

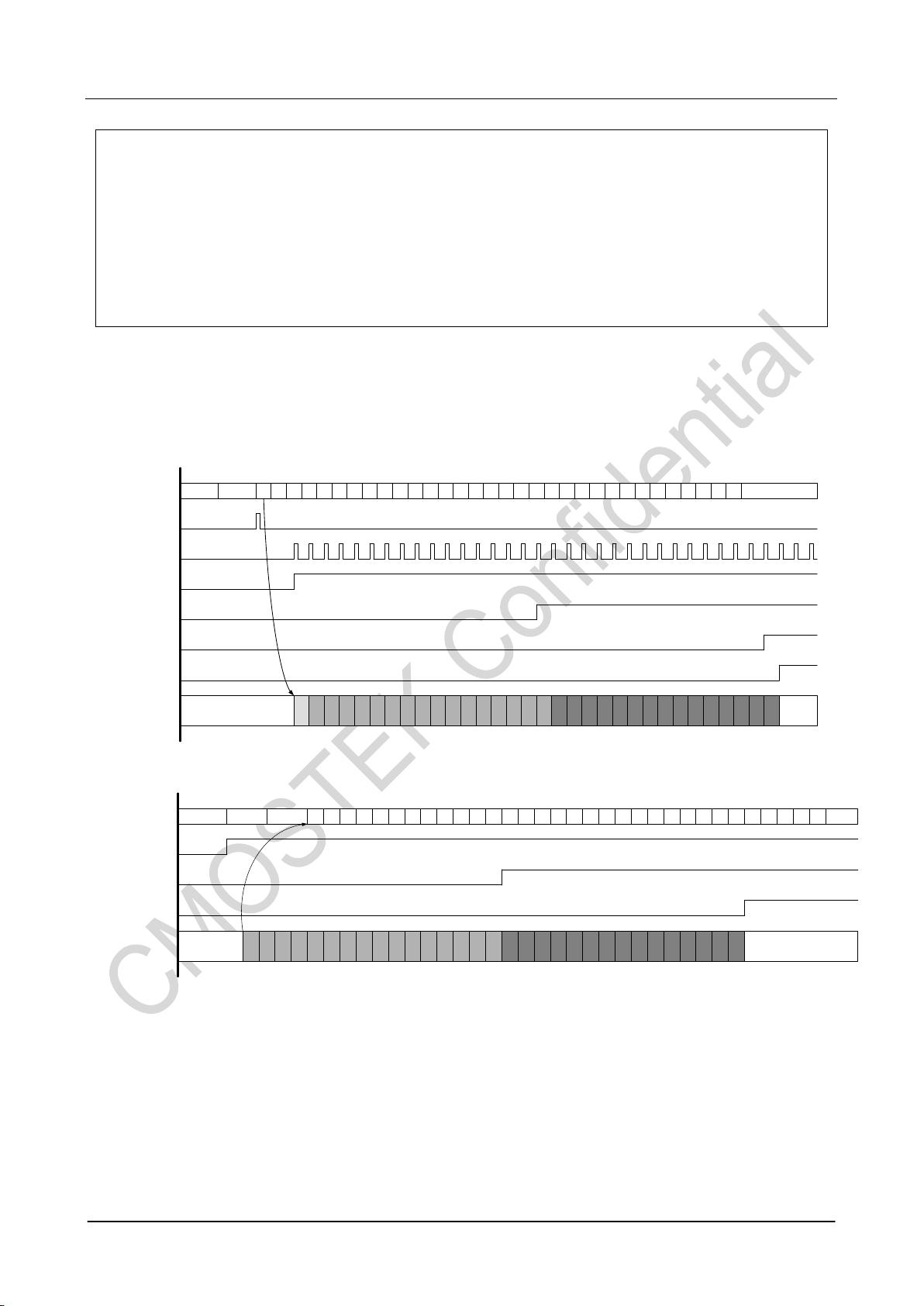

1. Detect the RX_FIFO_FULL interrupt. Once valid indicates that the FIFO has been filled, you can start

reading. The appropriate packet length is just equal to the FIFO depth. Also, the user does not read the

FIFO until the full packet is received.

2. Detect the RX_FIFO_TH interrupt. Once valid indicates that the FIFO has been filled in the preset data

length, you can start reading. The appropriate packet length is not equal to the FIFO depth. Also, the

user does not read the FIFO until the full packet is received.

3. Detect the RX_FIFO_NMTY interrupt. Once valid, read immediately until the interrupt is invalid. Read

again when the interrupt is valid again. This allows you to read them while you receive them. It is suitable

for the case where the packet length is greater than the FIFO depth and is suitable for the case where

the packet length is less than or equal to the FIFO depth.

4. Detect the X_FIFO_WBYTE interrupt. Read immediately once it is valid. This allows you to achieve the

regular operation to write a byte and then read a byte. The premise is that SPI is faster than receiving the

data.

In addition, you can define how many packets are sent per sending by setting the TX_PKT_NUM <7:0>.

If sending the packet is more than one, the FIFO_AUTO_RES_EN is set to 1. That is, the TX FIFO

automatically clears the read pointer and goes back the unread state after each packet is sent. This allows

you to repeatedly send the same packet. You don't need MCU to fill in the data again. The user can set the

TX_PKT_GAP <7:0> to define the time gap between each packet, the unit is the symbol. After entering the

transmitting state, the transmitter sends N packets according to these configurations. After completing, the

transmitter automatically exits the TX and returns to the specified state. The status after exiting can be

configured by TX_EXIT_STATE <1:0>.

If you want to achieve continuous reception, it is recommended to use the above fourth operation. This

needs SPI to read quickly enough. At least it is 1.5 times faster than the rate that FIFO writes a byte. For

example, if the data rate is 10KHz, the time it takes to receive a byte is about 800 us. The rate SPI reads a

byte is 1.5 times faster than the rate FIFO writes a byte. The most time-consuming is 534us. SPI reads a byte

for 8 SCL clock cycles, but with the added time cost before and after, we can count it according to the 10 SCL

clock cycles, then each cycle is 53.4us, converted to SCL clock frequency is about 18.7 kHz. The rate of SCL

is roughly 2 times the rate of data.

1.4.2 Application scene 2: Fill in the data beforehand and enter the TX transmitting

For many applications, pre fill the data packets to be transmitted into TX FIFO, and then enter the TX

transmitting. The behavior of filling data is suggested to be executed in the STBY state. This scene is suitable

for packet length less than or equal to FIFO depth, and the application time does not need to be very compact.

After the user pre configured, he can write the data directly and judge whether the data has been fully written

by detecting the interrupt of TX_FIFO_NMTY, TX_FIFO_TH or TX_FIFO_FULL. During the debugging stage,

after completing the data, the user can read back the filling data according to the following methods, and