硬件工程师笔试全攻略:试题与解析

这篇资源主要涵盖了硬件工程师笔试的相关试题和答案,包括了电子工程的基础知识、逻辑电路设计、可编程逻辑器件、电路设计流程、电子组件理解、数字信号处理以及通信协议等多个方面。以下是对这些知识点的详细解释:

1. 建立时间和保持时间:在数字逻辑中,建立时间是指数据输入到时钟边沿之间必须满足的最小时间间隔,以确保正确捕获数据。保持时间则是指时钟边沿之后数据必须稳定不变的时间长度,以避免错误的翻转。

2. 竞争与冒险现象:在数字电路中,当多个信号同时到达一个节点时,可能导致输出的不稳定,这种现象称为竞争。冒险则是在电路中由于延迟不一致导致的短暂输出错误。

3. D触发器实现2倍分频:D触发器可以用来实现时钟分频,通过反馈其输出到输入端,可以实现频率减半的效果。

4. "线与"逻辑:这是一种利用晶体管的饱和导通状态实现的逻辑操作,要求所有输入都为低电平时输出才为低。要实现"线与",通常需要使用带有开漏输出的门电路,并通过上拉电阻来提供高电平。

5. 同步逻辑与异步逻辑:同步逻辑中,所有元件都按照同一个时钟信号工作;异步逻辑则不受单一时钟控制,信号传递依赖于前级输出的稳定。

6. Latch与Register的区别:Latch是一种瞬时存储器,数据在时钟信号改变时保持;Register则是时钟同步的存储器,数据在时钟边沿被采样。由于Register更易于设计和控制,现在更常被使用。

7. 锁相环(PLL):PLL是一种能够锁定输出频率与输入参考频率之间的相位关系的电路,常用于频率合成和相位同步。

8. 逻辑电平:常见的有TTL和CMOS电平,它们不能直接互连,因为TTL的高电平输出无法驱动CMOS的输入,而CMOS的低电平可能不足以使TTL电路关闭。

9. 可编程逻辑器件:如FPGA、CPLD等,可以通过编程实现用户自定义的逻辑功能。VHDL和VERILOG是两种常用的硬件描述语言,可以用来描述8位D触发器等逻辑。

10. EDA设计流程:从原理图设计、布局布线、仿真验证到PCB制造,每个步骤都需要关注信号完整性和电源完整性,防止电磁干扰等问题。

11. 实现逻辑函数:如用逻辑门和CMOS电路实现AB+CD,或者用MUX和INV实现异或门。

12. 亚稳态解决:亚稳态通常出现在同步电路中,通过增加寄存器级或使用同步复位/预置来避免。

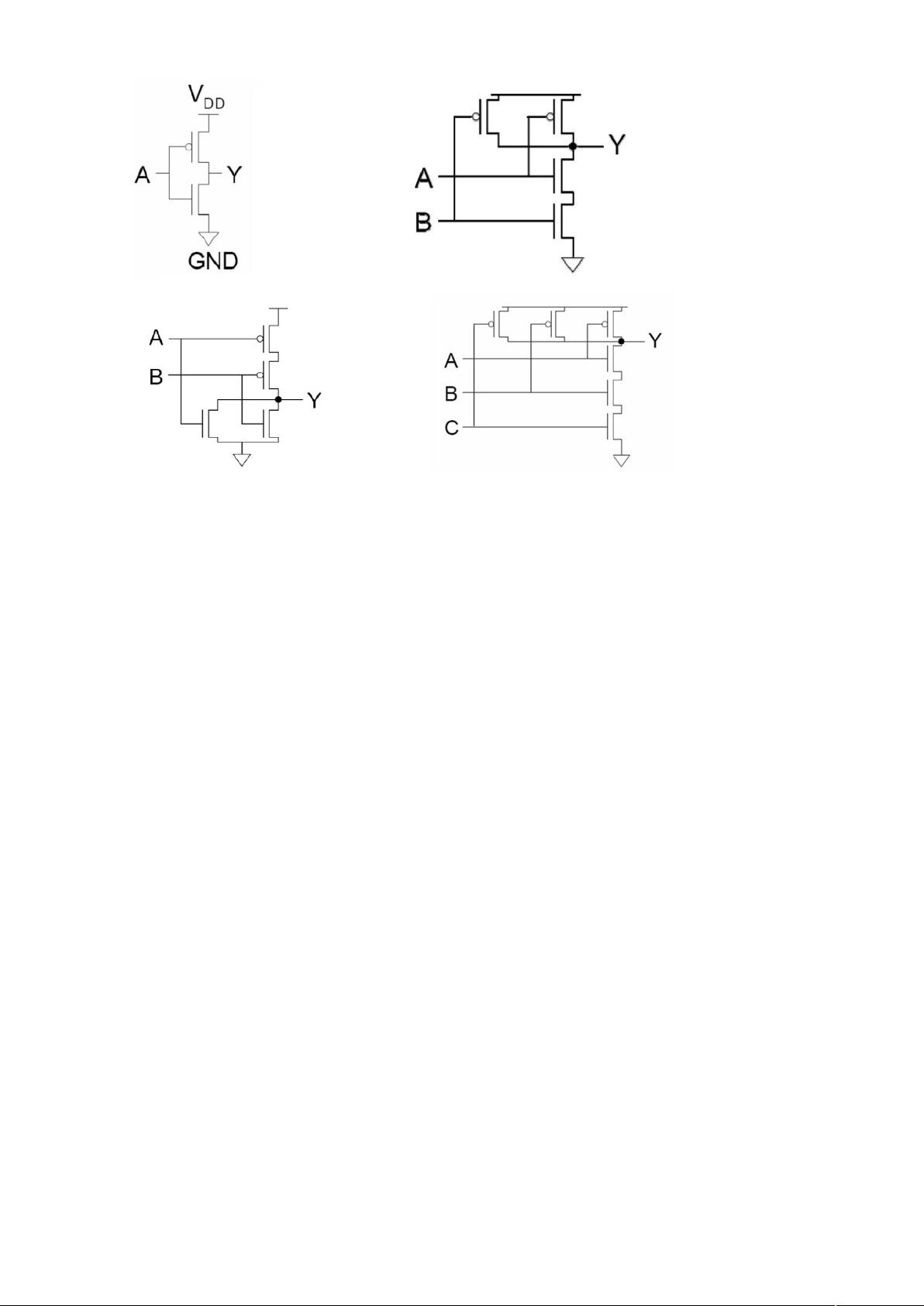

13. MOS管构建与非门:通过两个N沟道MOS管的互补连接,可以构成一个简单的与非门。

14. 集成电路前段设计流程涉及工具:包括逻辑综合、布局布线、版图设计等,常见的工具有Synopsys、Cadence、 Mentor Graphics等。

15. 名词解释:IRQ是中断请求,BIOS是基本输入输出系统,USB是通用串行总线,VHDL是硬件描述语言,SDR是软件定义无线电。

其余知识点包括数字信号处理芯片(DSP)、CPU和MCU的区别,二进制编码,中断处理流程,不同类型的内存(如SRAM、SSRAM、SDRAM),信号与系统的关系,模拟电路的频率补偿,奈奎斯特采样定律,数字电路总结,DMA(直接内存访问)原理和功能,串行与并行通信的比较,RS232C协议,放大电路的频率补偿目的和方法,模拟信号到数字信号的转换,以及数字电子电路的总结。

这个资源为准备硬件工程师笔试提供了全面的复习材料,涵盖了电子工程的关键概念和技术。

270 浏览量

5057 浏览量

170 浏览量

215 浏览量

214 浏览量

222 浏览量

5057 浏览量

6118 浏览量

550 浏览量

kaoyanfor2010

- 粉丝: 0

最新资源

- ASP.NET集成支付宝即时到账支付流程详解

- C++递推法在解决三道经典算法问题中的应用

- Qt_MARCHING_CUBES算法在面绘制中的应用

- 传感器原理与应用课程习题解答指南

- 乐高FLL2017-2018任务挑战解析:饮水思源

- Jquery Ui婚礼祝福特效:经典30款小型设计

- 紧急定位伴侣:蓝光文字的位置追踪功能

- MATLAB神经网络实用案例分析大全

- Masm611: 安全高效的汇编语言调试工具

- 3DCurator:彩色木雕CT数据的3D可视化解决方案

- 聊天留言网站开发项目全套资源下载

- 触摸屏适用的左右循环拖动展示技术

- 新型不连续导电模式V_2控制Buck变换器研究分析

- 用户自定义JavaScript脚本集合分享

- 易语言实现非主流方式获取网关IP源码教程

- 微信跳一跳小程序前端源码解析