大规模逻辑设计:VERILOG编码与常见问题指南

需积分: 32 196 浏览量

更新于2024-07-27

收藏 3.45MB PDF 举报

《大规模逻辑设计指导书》是一份详细的专业文档,针对逻辑设计过程中的关键环节提供深入指导。这份140页的内部使用文档主要分为两大部分:第一篇方法论和第二章VERILOG语言编写规范。它涵盖了从设计前期的命名规则、规范内容,到具体编程技巧如选择有意义的信号和变量名、Verilog和VHDL语言的使用,再到代码模块划分、逻辑结构(如有限状态机、函数、类属和运算符)的实现。

在章节28的“命名规则”部分,强调了信号和变量命名的重要性,应包含其功能、来源以及状态等信息,以便于理解和维护设计。编码风格指南则推荐使用规范化的命名和注释,以提高代码可读性。VERILOG语言编写规范中详细列出了保留字、参数化元件实例、程序包和函数的书写示例,以及VHDL范例,以帮助开发者熟悉这两种硬件描述语言的使用。

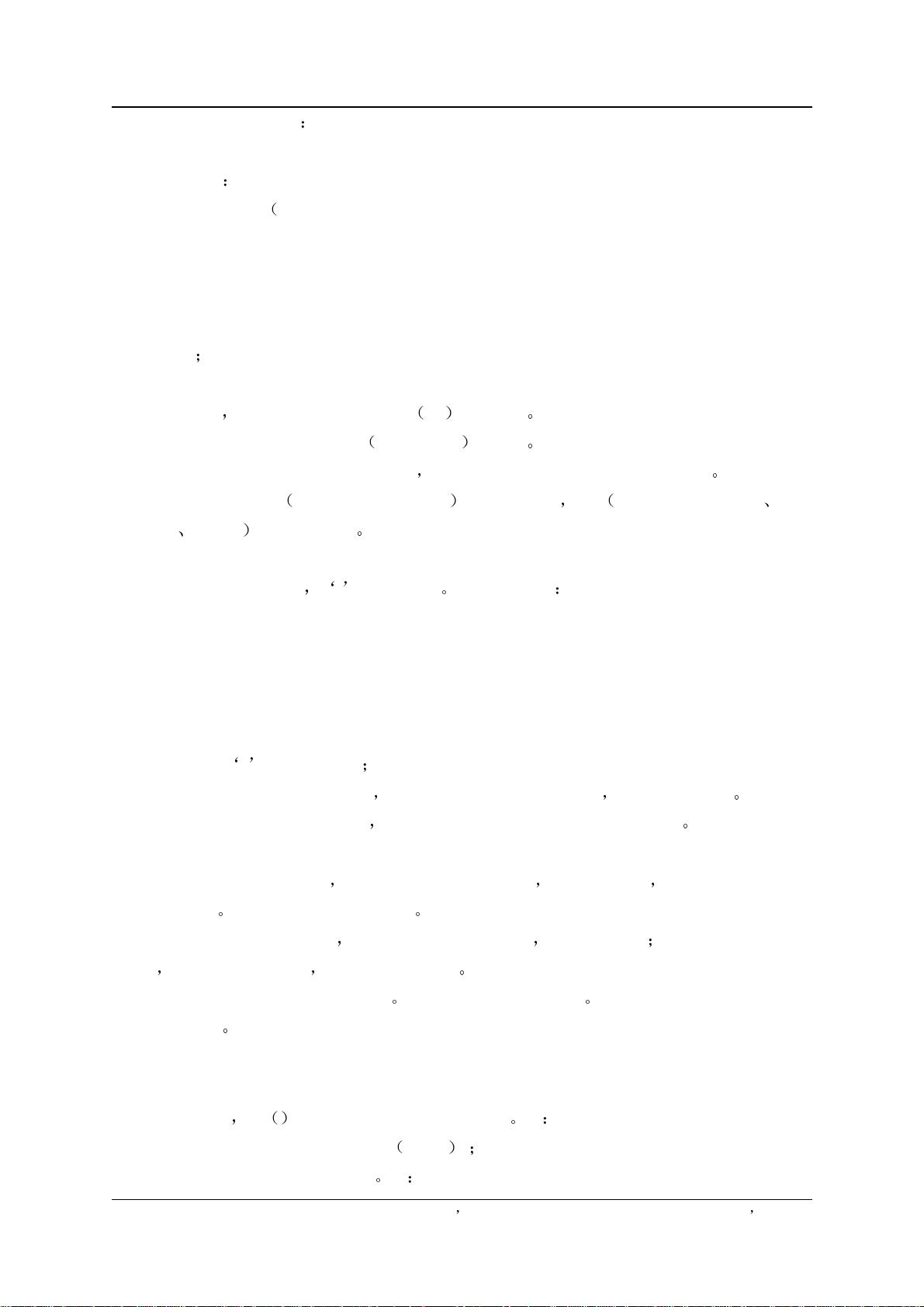

章节5着重讨论了代码编写过程中可能遇到的问题,例如使用有限状态机(FSM)时的注意事项、避免使用过时的latch、处理多赋值语句和三态总线、优化综合执行时间和解决资源共享问题。这些内容旨在帮助设计师避免常见错误,提高设计效率和质量。

此外,文档还涉及了代码模块化的设计原则,如使用TAB键间隔以保持良好的代码格式,以及对函数、procedure、类属(generics)和运算符的正确运用。通过详尽的指导,这份文档旨在为从事大规模逻辑设计的专业人员提供一个全面且实用的参考框架,确保设计过程的系统性和准确性。整个文档由研究管理部文档中心发布,强调版权和保密性,提醒读者未经许可不得复制或侵权。

2010-03-29 上传

2009-10-13 上传

2015-09-10 上传

2023-07-16 上传

2024-10-28 上传

2024-11-02 上传

2024-11-08 上传

2024-10-31 上传

2024-10-28 上传

shuhuan0826

- 粉丝: 0

- 资源: 2

最新资源

- Cucumber-JVM模板项目快速入门教程

- ECharts打造公司组织架构可视化展示

- DC Water Alerts 数据开放平台介绍

- 图形化编程打造智能家居控制系统

- 个人网站构建:使用CSS实现风格化布局

- 使用CANBUS控制LED灯柱颜色的Matlab代码实现

- ACTCMS管理系统安装与更新教程

- 快速查看IP地址及地理位置信息的View My IP插件

- Pandas库助力数据分析与编程效率提升

- Python实现k均值聚类音乐数据可视化分析

- formdotcom打造高效网络表单解决方案

- 仿京东套餐购买列表源码DYCPackage解析

- 开源管理工具orgParty:面向PartySur的多功能应用程序

- Flutter时间跟踪应用Time_tracker入门教程

- AngularJS实现自定义滑动项目及动作指南

- 掌握C++编译时打印:compile-time-printer的使用与原理