CPLD公话计费系统设计:基于EPM240T100C5的硬件与Verilog软件实现

需积分: 7 62 浏览量

更新于2024-07-21

1

收藏 1.4MB DOC 举报

"基于CPLD的公话计费器的设计"

这篇论文详细阐述了如何设计一个基于复杂可编程逻辑器件(CPLD)的公用电话计费系统。CPLD在这里扮演了核心角色,用于实现计费器的各种功能。设计涵盖了电路设计、软件设计以及程序仿真,以确保系统的完整性和准确性。

在硬件设计部分,主要采用了Altera公司的MAX II系列EPM240T100C5 CPLD芯片。这个芯片具有高度的灵活性和可配置性,适合于构建复杂的逻辑功能。外围电路包括:

1. 时钟电路:提供稳定的时间基准,对计费和控制信号的生成至关重要。

2. 按键电路:用户通过按键进行操作,如拨号、挂断等,同时可能包含功能键以执行特定任务。

3. 声光报警电路:当出现异常情况如通话时间超限或卡内余额不足时,发出警告。

4. 数码管显示电路:实时显示通话时间、卡内余额等关键信息。

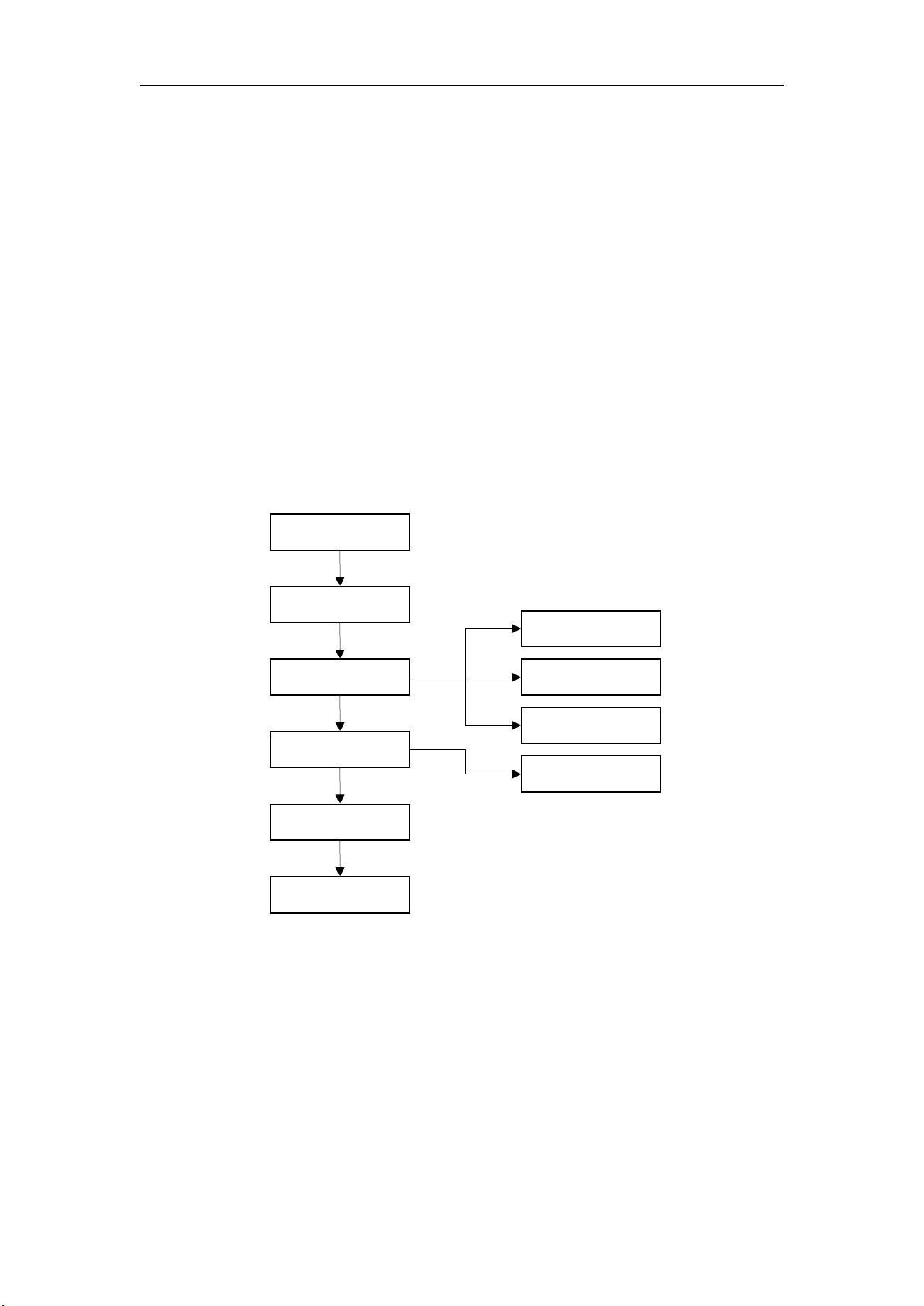

软件设计部分则采用Verilog HDL(硬件描述语言)进行编程,这是一种常用的语言,用于描述数字系统的结构和行为。设计遵循“自底向上”的方法,即首先设计并验证各个子模块,如:

- 时钟分频模块:调整时钟频率,以适应不同速度的需求。

- 按键去抖模块:消除按键操作中的机械抖动,确保稳定可靠的输入。

- 北京时间计时模块:同步真实时间,用于区分正常时段和优惠时段的计费。

- 通话计时计费模块:根据通话时长和费率进行精确计费。

- 控制模块:协调各部分工作,生成必要的控制信号。

- 声光报警模块:在需要时触发报警。

- 数码管显示模块:驱动数码管显示相关信息。

在完成子模块设计后,通过顶层模块将它们集成在一起,形成完整的计费系统。使用QuartusⅡ软件进行程序的调试和仿真,这包括对单个子模块的功能验证以及整个系统的综合仿真,确保设计的正确性和可靠性。

关键词:CPLD(复杂可编程逻辑器件)、Verilog(硬件描述语言)、QuartusⅡ(Altera公司的综合和仿真工具)、自底向上设计方法。这些关键词揭示了设计过程中涉及的关键技术和方法。

这个基于CPLD的公话计费器设计项目展示了如何利用现代数字逻辑设计技术来创建一个功能齐全、精确且用户友好的计费系统。从硬件电路到软件逻辑,每个环节都经过精心设计和严谨的测试,确保了计费器在实际应用中的高效运作。

277 浏览量

166 浏览量

2015-09-16 上传

155 浏览量

108 浏览量

533 浏览量

201 浏览量

216 浏览量

179 浏览量

邹小敏3

- 粉丝: 124

- 资源: 5

最新资源

- parser:使用生成语法模型的语义解析器归纳

- ShareSystem.zip

- 智慧交通总体解决方案.zip

- AirBnB_clone

- streamlit-One2

- video-freqtimeupdate:HTML5视频元素的频繁更新

- 可调时长的多波形显示设计(stm32)

- mimosa-ember-htmlbars:用于 Mimosa 的 Ember 特定的 htmlbars 编译器

- axopy:用于实现人机界面实验的Python库

- 智慧交通产业园建设思路(1).zip

- 网络作品集

- 汇川中型PLC的AM402和触摸屏IT7000E测试

- Simple-Scripts:一个包含我过去使用过的简单脚本的存储库

- 实验1 跑马灯实验_STM32F407LED_

- mup:标记预览器

- 基于FPGA的数字频率计vhdl(4位数码管).zip