AMBA 2.0: AHB与APB总线协议详解

需积分: 15 61 浏览量

更新于2024-07-19

收藏 426KB PPT 举报

"该文档详细介绍了AMBA版本2.0中的高级高性能总线(AHB)和先进外围总线(APB),涵盖了AHB的基本信号时序、总线主控、仲裁机制、HREADY输入/输出以及默认从控等关键概念,并通过实例展示了AHB系统和APB桥接的结构。"

在AMBA(Advanced Microcontroller Bus Architecture,高级微控制器总线架构)版本2.0中,AHB是设计用于高性能、高带宽的片上通信的一种标准接口。它支持多个总线主控器和从设备,以满足复杂的嵌入式系统的需求。AHB的主要目标是提高系统性能,同时保持低功耗。

**AHB基本信号和时序**

AHB的核心信号包括:

1. **HCLK**:所有AHB操作的时钟参考,确保所有设备在同一时间点同步。

2. **HADDR**:32位地址总线,用于指定数据传输的位置。

3. **HWRITE**:读写控制信号,当为高电平时,表示当前传输是写操作;为低电平时,表示是读操作。

4. **HREADY**:传输完成响应,由从设备发出,表明它已经准备好接收或发送数据。

5. **HRESP**:传输状态响应信号,用于报告传输的成功或错误状态,如OKAY、ERROR等。

6. **HWDATA**:写数据总线,主控器向从设备传输数据的通道。

7. **HRDATA**:读数据总线,从设备向主控器返回数据的通道。

**AHB总线主控**:AHB系统可以有多个主控器,它们可以并发发起事务。每个主控器都有一个独立的HSEL(选择)信号,用于选择目标从设备。

**AHB仲裁**:在AHB中,仲裁器负责决定哪个主控器有权访问总线。它可以基于优先级、轮询或其他策略来分配总线使用权。

**HREADY输入/输出**:HREADY信号是一个双向信号,用于在地址阶段和数据阶段提供握手,确保正确同步。主控器和从设备都可以通过这个信号来表明是否准备好进行下一个时钟周期的操作。

**APB桥接**:APB(Advanced Peripheral Bus)是AHB的一个低带宽、非流水线式的子总线,用于连接低速外设。AHB到APB桥允许AHB主控器通过APB与这些外设通信,从而节省带宽并优化性能。

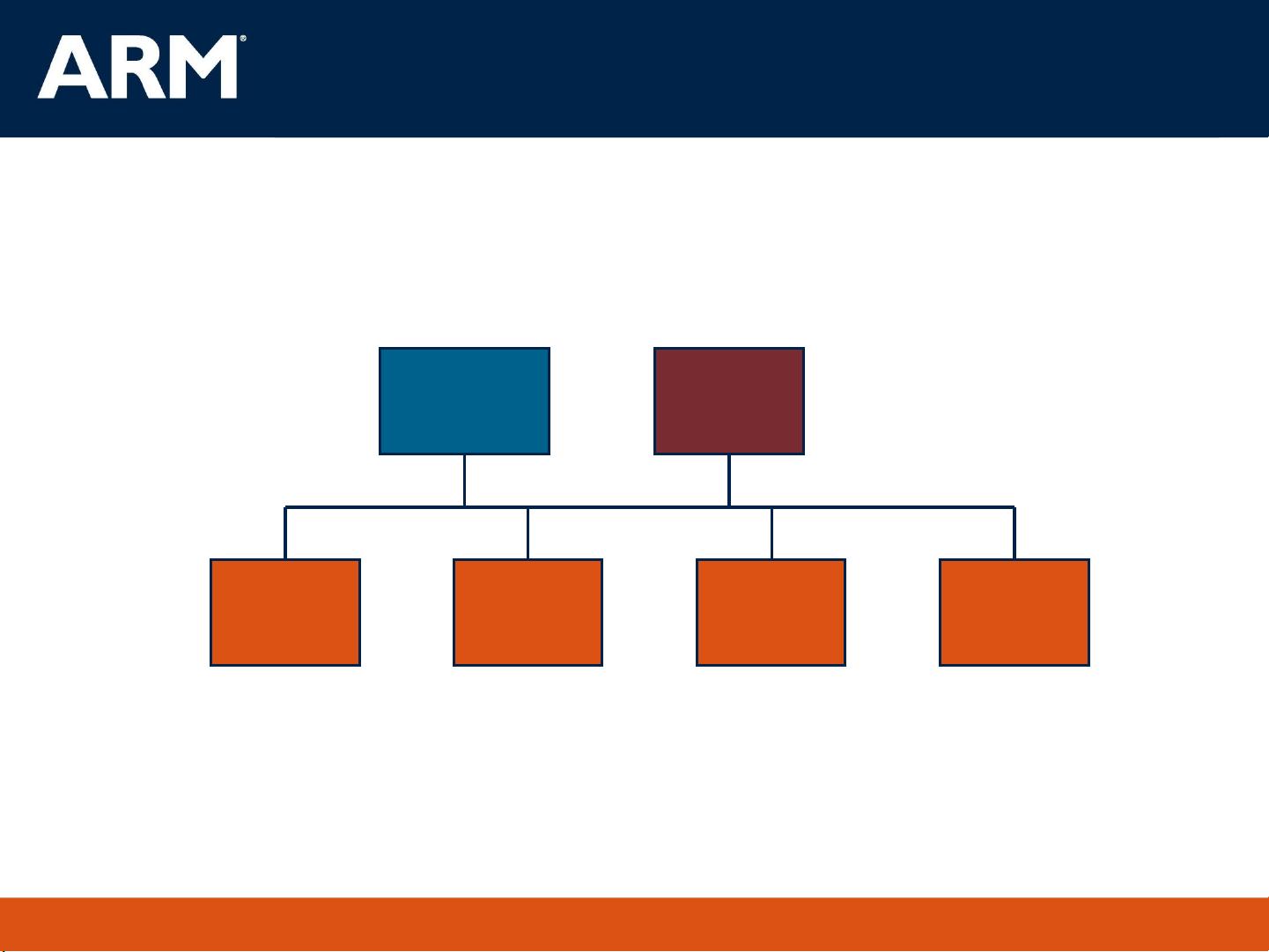

**示例系统**:示例系统中,包含高性能ARM处理器、高速片上RAM、外部存储器接口、DMA(直接存储器访问)主控器、APB桥接器、定时器、键盘、UART(通用异步收发传输器)、GPIO(通用输入输出)等组件。APB桥接器连接了多个APB主控器,如定时器、键盘和UART,它们通过APB总线与AHB总线交互。

AHB总线是构建高性能嵌入式系统的关键组成部分,其丰富的信号集和灵活的仲裁机制使其能够在多种应用场景下实现高效的数据交换。而APB则为连接低速外设提供了经济高效的解决方案。通过理解和应用这些概念,设计师能够构建出满足特定需求的复杂SoC(System-on-Chip)系统。

2191 浏览量

153 浏览量

2024-11-08 上传

220 浏览量

2024-11-08 上传

2024-10-28 上传

2024-10-28 上传

peixiancsdn

- 粉丝: 0

- 资源: 2

最新资源

- 小波功率谱用于降水、气温等的周期分析

- MPC模型预测控制-欠驱动船舶.zip

- torch_sparse-0.6.4-cp36-cp36m-linux_x86_64whl.zip

- vitamincalculator:给出不同维生素的计算器限制并计算您的每日剂量

- SteamAuth:NodeJS Steam身份验证器,登录和交易确认

- dkreutter.github.io

- Implementation-of-Graph-kernels:阅读有关图核的调查而编写的代码

- labelImgPackage.rar

- 公司营业室主任行为规范考评表

- torch_cluster-1.5.5-cp38-cp38-linux_x86_64whl.zip

- postnet-version-1.1B

- beavisbot:适用于plug.dj和dubtrack.fm的由node.js驱动的机器人

- FSDI103PROJECT2

- 导航菜单可拖动

- 编译so文件 Unity调用so文件样例

- 行政支援课课长