CycloneII NiosII 2C35开发板原理图详细资料

"CycloneII_NiosII_2C35_DB_SCH" 是一套关于CycloneII系列NiosII嵌入式处理器在2C35配置下的开发板(Schematic)资料,包含了最全的原理图设计,由Altera公司提供。文档可能涉及到多个版本的修订历史,例如00、01、02等,反映了设计的迭代和改进,以适应RoHS标准(Restriction of Hazardous Substances,有害物质限制)并进行了一些小的结构更新。

NiosII是Altera公司推出的一种软核处理器,适用于FPGA(Field-Programmable Gate Array)设计。CycloneII系列是Altera的第二代低成本FPGA系列,以其低功耗和高性价比而受到广泛应用。在2C35配置下,NiosII处理器被集成到CycloneII FPGA中,用于实现各种嵌入式系统设计。

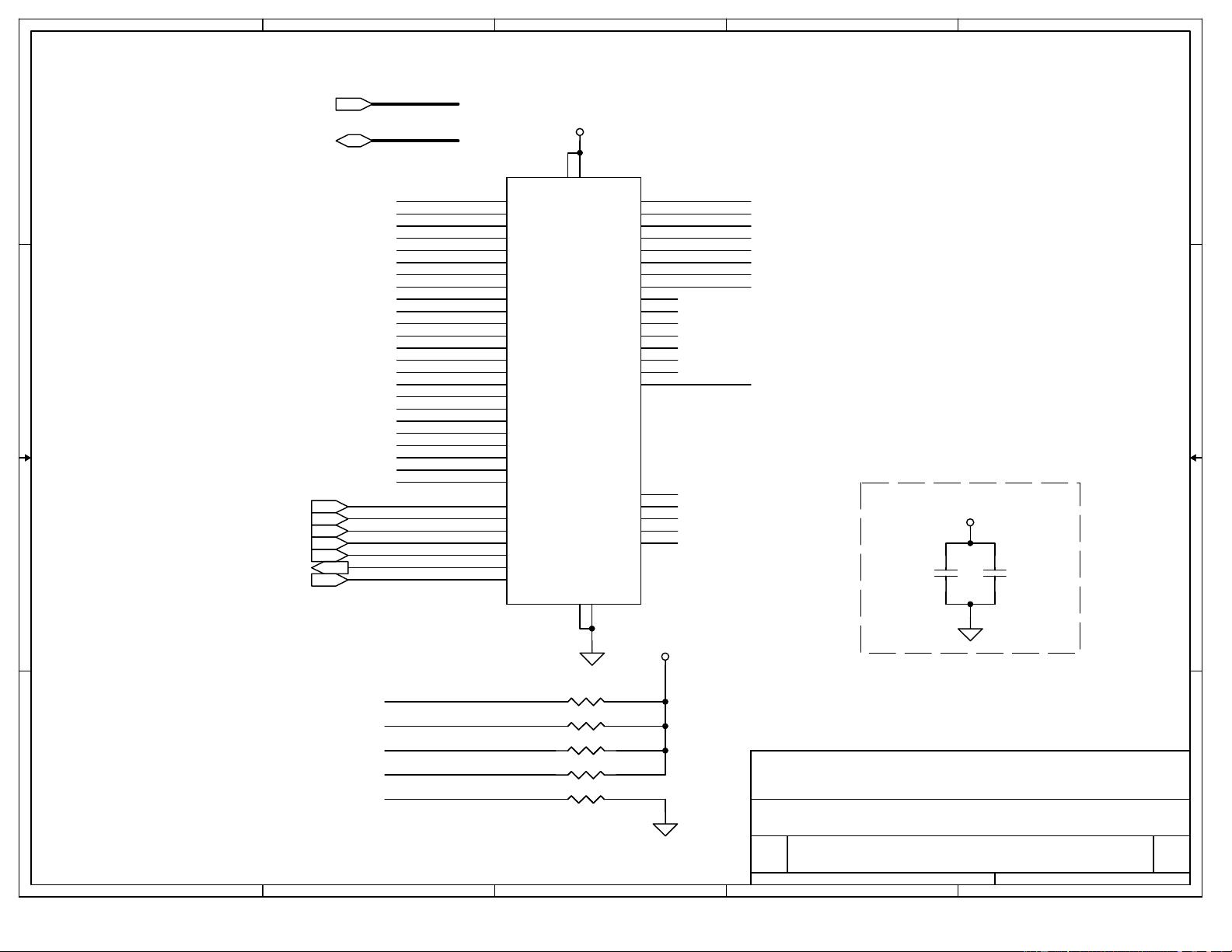

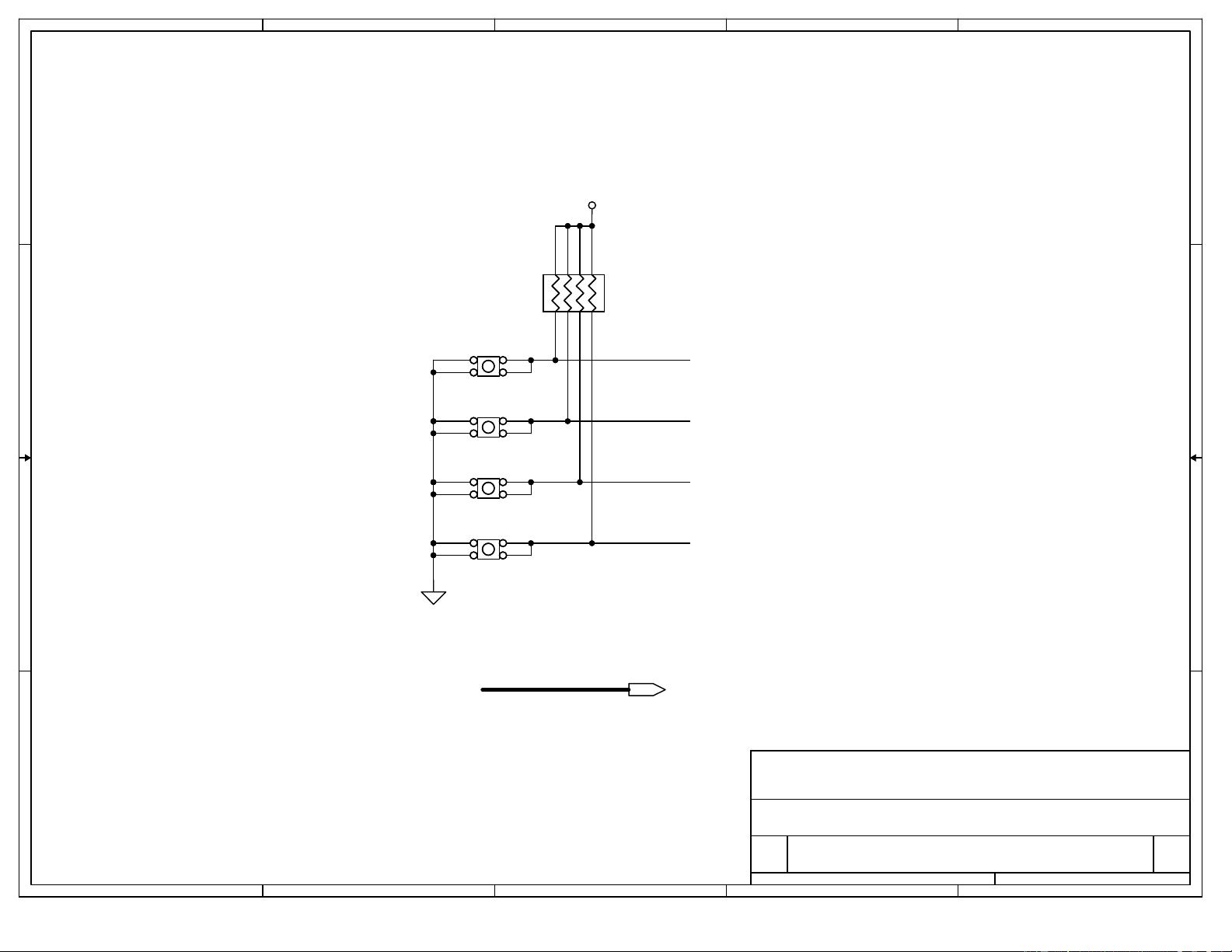

该资料集中的原理图详细描绘了NiosII开发板的硬件连接,包括以下几个关键部分:

1. **SRAM接口**:sram_CE1_n, sram_WE_n, sram_BE_n[3:0], sram_OE_n 和 sram_D[31:0] 分别代表SRAM的片选输入、写使能、字节使能、输出使能和数据总线。这些信号控制了SRAM的读写操作,确保数据正确存取。

2. **地址总线**:sram_A[20:0] 表示SRAM的地址线,用于指定要访问的数据存储位置。

3. **扩展接口**:proto1_IO[40:0] 和 proto2_IO[40:0] 可能是用于原型验证的输入/输出引脚,允许开发者连接外部设备或扩展功能。

4. **卡选择信号**:proto1_CARDSEL_n 可能用于选择不同的功能模块或板上子系统。

5. **其他未具体定义的信号**:在描述中没有详细说明的其他信号可能包括电源、时钟、复位以及其他必要的控制和状态信号,这些都是构建一个完整嵌入式系统所必需的。

通过这些详细的设计资料,开发者可以理解NiosII处理器如何与CycloneII FPGA的其他逻辑资源交互,以及如何配置外围接口,从而进行自定义的硬件加速器设计或系统级集成。对于学习FPGA设计、嵌入式系统开发以及了解Altera NiosII处理器的硬件实现来说,这套资料是非常宝贵的资源。

2022-07-13 上传

152 浏览量

152 浏览量

2022-09-19 上传

151 浏览量

2022-07-14 上传

2012-12-08 上传

2022-09-24 上传

2022-09-24 上传

gfjhuytkiuo

- 粉丝: 0

- 资源: 3

最新资源

- 抄算组抄表员考核内容和评分标准XLS

- jdk-11.0.10.zip

- pytorch-blockswap:块交换代码(ICLR 2020)

- algorithm

- Keras数据集.7z

- 360炫酷网址导航

- 公司设计管理专职行为规范考评表

- ab并发测试及说明.rar

- 贷款还款预测

- movie_app:React JS基础课程(2021更新)

- PyctureStream:使用Kafka,Spark Streaming和TensorFlow进行图像处理的PoC

- torch_cluster-1.5.6-cp38-cp38-linux_x86_64whl.zip

- Lowrate Screen Sharing-crx插件

- autocomplete:轻松查找英语词典中的单词

- 奥克斯企业文化全案剖析DOC

- CS50x的从零开始的迷宫式革命