FPGA实现的全数字锁相环设计与仿真

版权申诉

110 浏览量

更新于2024-06-29

1

收藏 1.39MB PDF 举报

该资源是一份关于基于FPGA的数字锁相环设计的学术论文,涵盖了锁相环技术的发展、研究意义、FPGA设计基础、锁相环的原理以及具体设计实现过程,包括数字鉴相器、K变模可逆计数器、脉冲加减器和N分频器的设计,最后还涉及了实验仿真与调试。

正文:

锁相环(PLL)技术在电子工程领域中起着至关重要的作用,尤其在通信、数据处理和信号同步等方面。基于FPGA(Field-Programmable Gate Array)的数字锁相环设计,能够灵活地实现高性能的频率和相位控制,具有广泛应用前景。FPGA因其可重构性,成为实现复杂数字逻辑系统的理想平台。

第一章介绍了锁相环的基本概念,阐述了锁相环在电子设备中的应用,即通过同步外部输入信号和内部振荡信号来确保设备的正确运行。锁相环由鉴相器、环路滤波器和压控振荡器等核心组件构成,实现频率跟踪和相位锁定。

第二章探讨了FPGA设计的基础,包括使用Verilog HDL进行硬件描述语言编程,以及FPGA的设计流程,包括逻辑综合、布局布线和功能仿真等步骤。

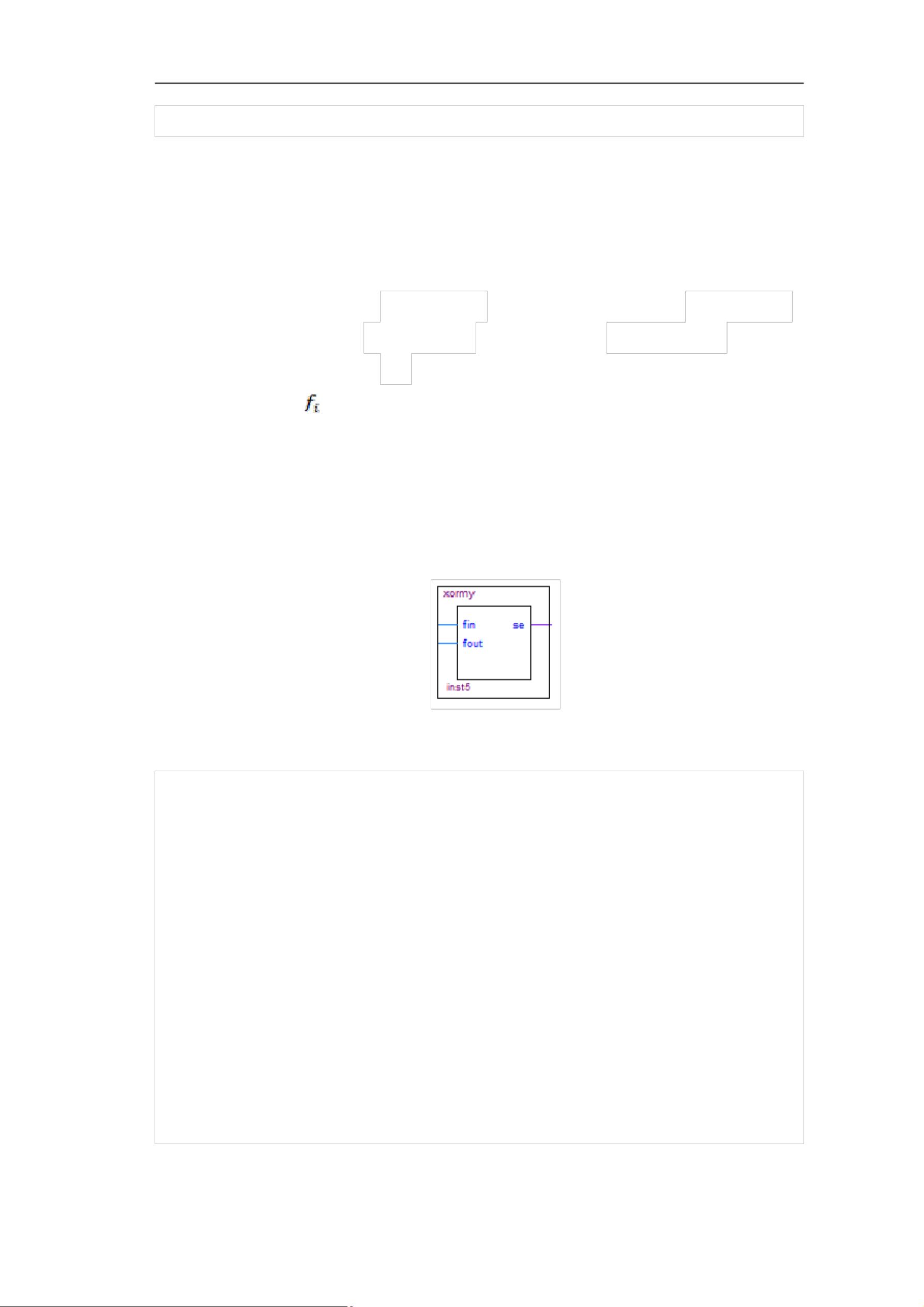

第三章深入解析了全数字锁相环的原理,指出其基本结构包含数字鉴相器、环路滤波器和压控振荡器。工作原理描述了如何通过鉴相器检测频率差,环路滤波器平滑误差信号,然后由压控振荡器调整频率,最终达到锁定相位的目的。

第四章详细介绍了数字锁相环的具体设计,包括:

1. 数字鉴相器的设计,它是锁相环的关键组件,负责比较输入参考信号与VCO输出信号的相位差,生成误差信号。

2. K变模可逆计数器,用于实现频率分频和倍频,以适应不同频率需求。

3. 脉冲加减器,用于在鉴相器输出的误差信号控制下增加或减少VCO的频率。

4. N分频器的设计,根据需要将输入信号分频,以匹配鉴相器的工作频率。

第五章详细描述了数字锁相环的仿真和系统实验过程,通过仿真验证设计的正确性和性能,系统实验则用于实际环境下的测试和调试,确保锁相环在不同条件下的稳定工作。

结束语部分可能总结了设计的成果、挑战和未来改进方向,而参考文献提供了进一步研究的资料来源。

这份文档对于理解FPGA上的数字锁相环设计有很高的价值,不仅包含了理论基础,还详细展示了实际设计步骤和实验验证,为相关领域的工程师和技术人员提供了宝贵的参考资料。

2023-11-27 上传

2023-07-11 上传

2023-07-14 上传

2023-06-24 上传

2024-01-25 上传

2023-12-23 上传

xxpr_ybgg

- 粉丝: 6715

- 资源: 3万+

最新资源

- zlib-1.2.12压缩包解析与技术要点

- 微信小程序滑动选项卡源码模版发布

- Unity虚拟人物唇同步插件Oculus Lipsync介绍

- Nginx 1.18.0版本WinSW自动安装与管理指南

- Java Swing和JDBC实现的ATM系统源码解析

- 掌握Spark Streaming与Maven集成的分布式大数据处理

- 深入学习推荐系统:教程、案例与项目实践

- Web开发者必备的取色工具软件介绍

- C语言实现李春葆数据结构实验程序

- 超市管理系统开发:asp+SQL Server 2005实战

- Redis伪集群搭建教程与实践

- 掌握网络活动细节:Wireshark v3.6.3网络嗅探工具详解

- 全面掌握美赛:建模、分析与编程实现教程

- Java图书馆系统完整项目源码及SQL文件解析

- PCtoLCD2002软件:高效图片和字符取模转换

- Java开发的体育赛事在线购票系统源码分析