Altera Cyclone IV FPGA器件手册解读

需积分: 12 123 浏览量

更新于2024-07-09

收藏 15.41MB PDF 举报

"FPGA_Cyclone IV 器件手册[中文]_(Altera).pdf"

本手册详细介绍了Altera公司的Cyclone IV FPGA系列,这是Altera在2011年推出的一系列高性能、低功耗的现场可编程门阵列(FPGA)器件。Cyclone IV系列是针对成本敏感型应用而设计的,它提供了卓越的性价比,适用于各种领域,包括工业控制、通信、消费电子和嵌入式系统。

1. Cyclone IV FPGA器件系列概述

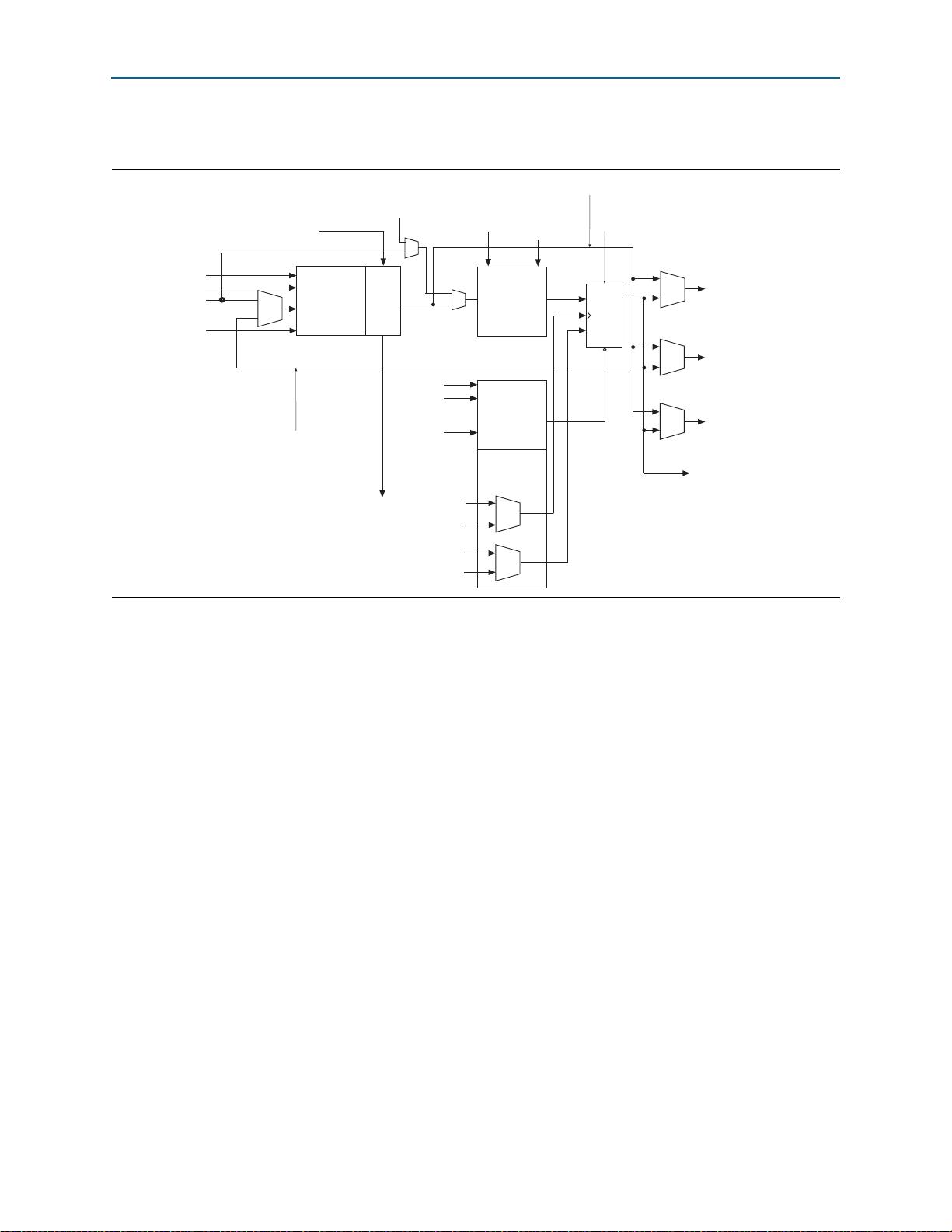

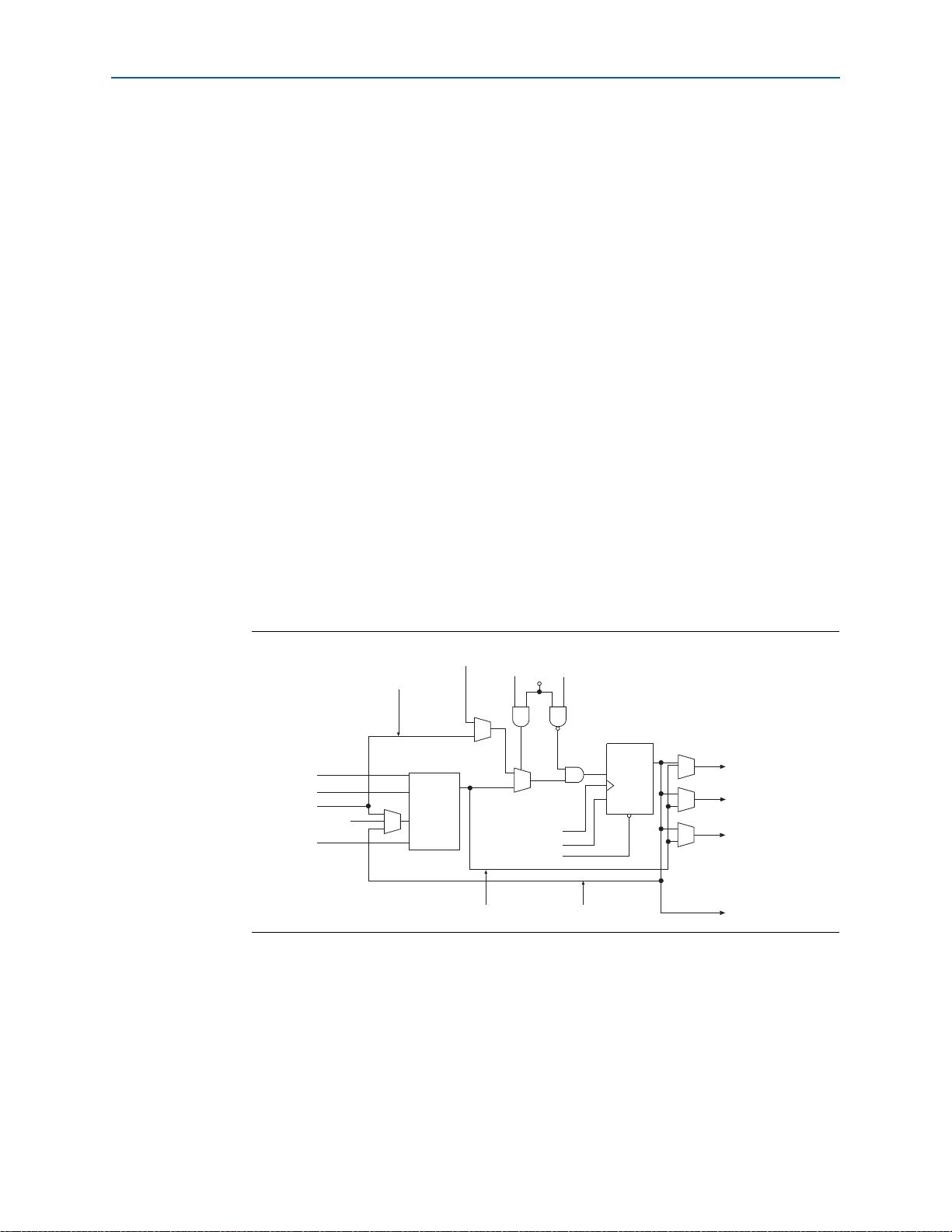

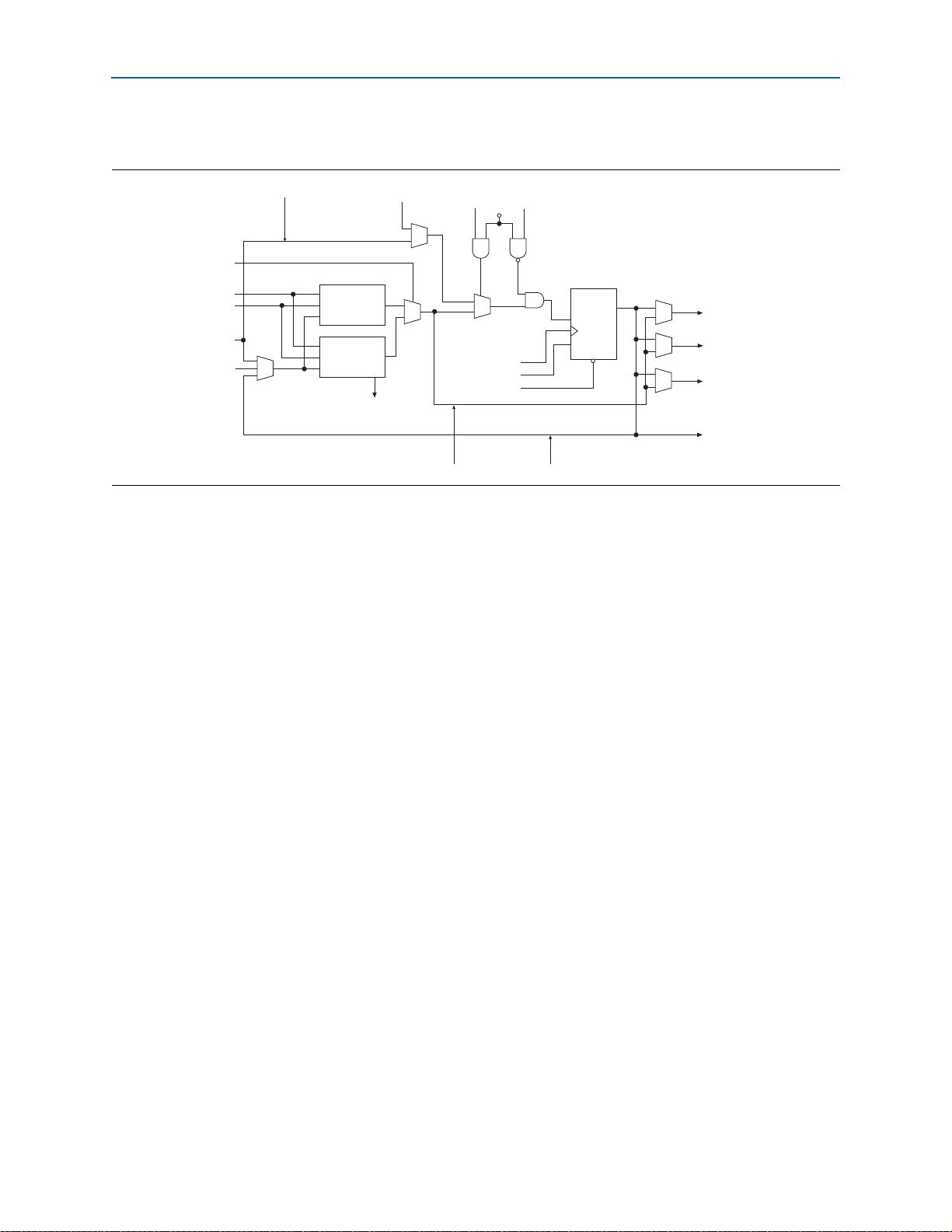

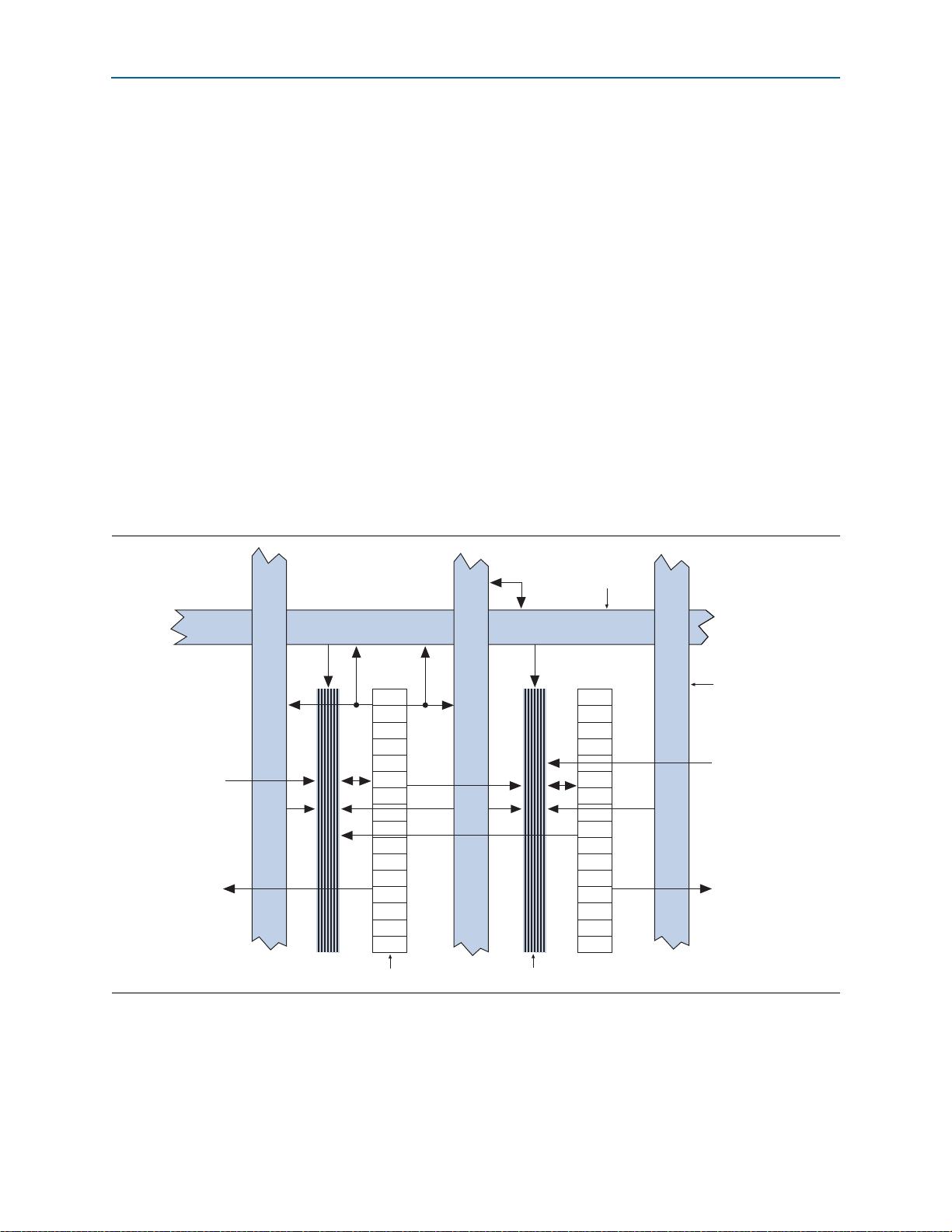

Cyclone IV系列是Altera FPGA产品线的一个重要组成部分,它旨在提供高效能、低功耗的解决方案。这一系列包括多个子系列,如Cyclone IV E、Cyclone IV G和Cyclone IV GX,以满足不同应用的需求。Cyclone IV器件集成了大量的逻辑单元、数字信号处理(DSP)块、嵌入式存储器以及丰富的I/O资源,以实现灵活的系统设计。

2. 设计灵活性

Cyclone IV FPGA提供广泛的硬核处理器系统(HPS),包括嵌入式Nios II处理器,使得用户能够构建高度集成的软核CPU系统。此外,该系列还支持Altera的HardCopy技术,允许用户在设计完成后将FPGA转换为ASIC,以进一步降低生产成本。

3. 功耗管理

Cyclone IV系列的一大亮点是其低功耗特性。通过采用创新的电源管理技术,如动态电压频率调整(DVFS)和部分重配置,设计者可以有效地控制和优化设备的能耗,这对于电池供电或对能源效率有严格要求的应用来说至关重要。

4. I/O性能与兼容性

Cyclone IV器件具有广泛的I/O标准支持,包括LVDS、PCI Express、 Gigabit Ethernet、DDR2/3内存接口等,确保了与多种外部设备和接口的无缝连接。这些I/O功能使得Cyclone IV成为各种高速数据传输应用的理想选择。

5. DSP增强

Cyclone IV FPGA包含专门优化的DSP块,能够高效执行浮点和定点运算,适合于视频处理、通信解码和图像处理等需要大量数学运算的应用。

6. 时序和性能

Cyclone IV系列在保持低功耗的同时,提供了出色的时序性能,能够满足高速设计的严格要求。其内部逻辑资源和布线架构经过精心优化,以实现快速的逻辑路径。

7. 设计工具与支持

Altera的Quartus II软件是Cyclone IV FPGA的主要设计工具,它提供了一套完整的开发环境,包括综合、布局布线、仿真和调试功能。此外,Altera还提供了丰富的IP核库、设计示例和在线技术支持,以协助开发者快速完成设计。

总结:

Cyclone IV FPGA器件手册为设计者提供了全面的技术指南,涵盖了器件架构、功能特性、设计流程和应用案例。无论是初学者还是经验丰富的工程师,都能从中获取必要的信息,以充分发挥Cyclone IV FPGA的优势,实现高效、节能且经济的设计方案。对于任何寻求在FPGA领域实施创新解决方案的人来说,这份手册都是不可或缺的参考资料。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2022-07-14 上传

2022-09-23 上传

2021-05-18 上传

2020-09-07 上传

123 浏览量

2019-11-07 上传

woochj

- 粉丝: 3

- 资源: 103

最新资源

- C# 开发经验 40种窗体常用代码

- 数据库考纲详解(绝对正确)

- 基于敏捷软件开发方法的基金管理信息系统开发

- 中国移动笔试试题及答案

- ARM嵌入式入门级教程

- 2009年研究生入学考试计算机统考大纲-完整版.pdf

- c#北大青鸟经典教程

- (2009 Wiley)LTE for UMTS:OFDMA and SC-FDMA Based Radio Access

- Proteus元件中英文名对照

- XML开发实务.pdf

- FFT算法的一种FPGA实现

- linux学习资料.pdf

- 有关TCP、Ip的嵌入式知识

- 达内面试笔记,分享(C++、Java).pdf

- DIV+CSS布局大全

- Linux的进程管理.doc