VHDL编程FPGA函数信号发生器设计

需积分: 20 157 浏览量

更新于2024-07-31

收藏 325KB DOC 举报

"EDA设计信号发生器,使用VHDL语言在FPGA上实现8选一的多功能信号发生器,可生成三角波、方波、锯齿波等。设计包括自顶向下的模块化结构,包含波形生成、选择、复位及控制功能。"

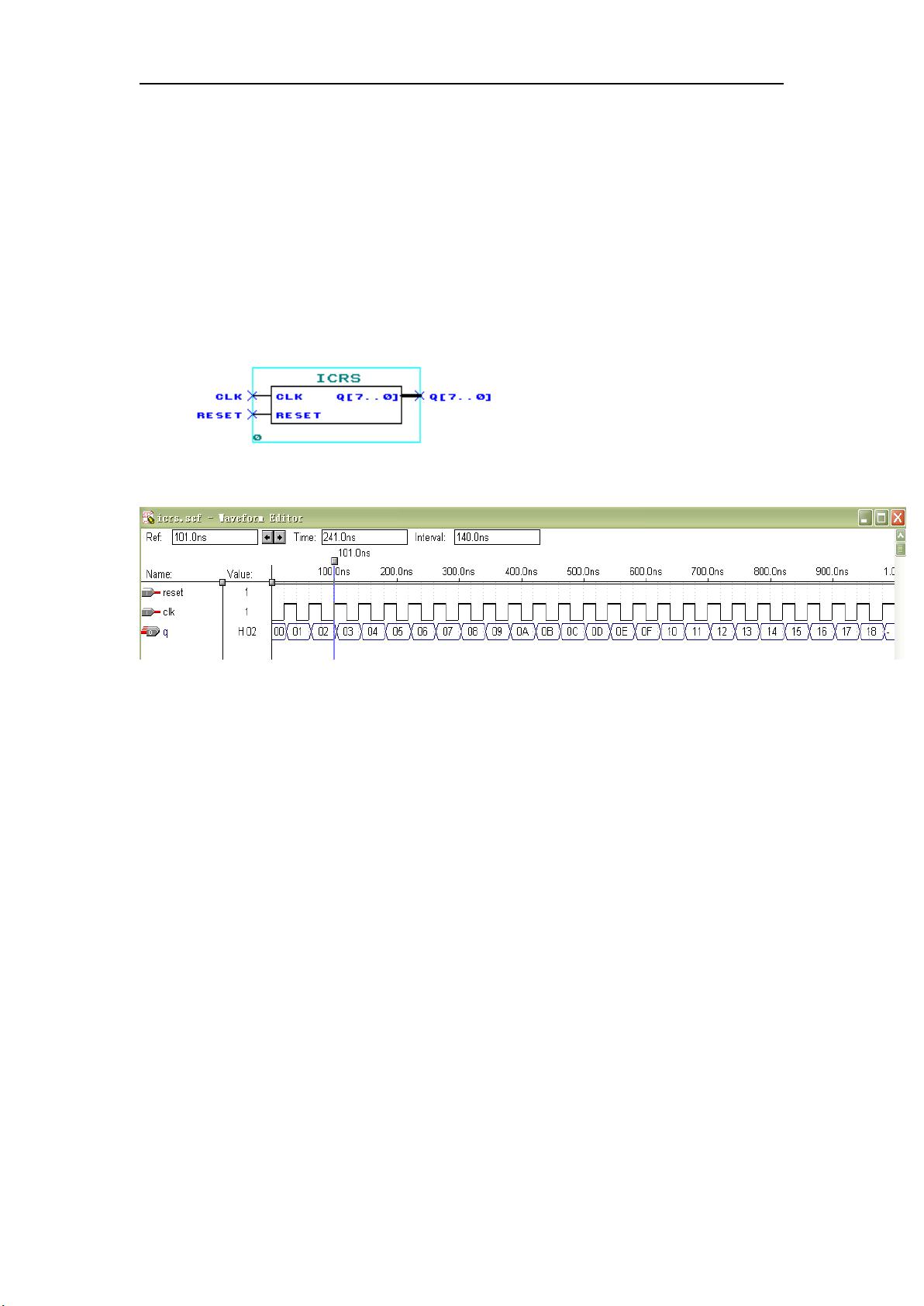

在电子设计自动化(EDA)领域,信号发生器是必不可少的工具,用于产生各种类型的电信号,如三角波、方波、锯齿波等,以供测试和调试其他电子设备。在本设计中,采用VHDL语言编程,利用现场可编程门阵列(FPGA)实现了一个8选1的多功能信号发生器。VHDL是一种硬件描述语言,它允许工程师以抽象的方式描述数字系统的逻辑,便于硬件的模拟和实现。

设计的关键部分包括:

1. **波形生成模块**:每个波形(如三角波、方波、锯齿波等)都有对应的生成模块。这些模块通过特定的算法和逻辑实现特定波形的生成。例如,三角波可能通过累加和除以最大值的方式得到,而方波则通过比较和阈值判断生成。

2. **选择模块**:该模块负责根据用户的输入或选择信号,决定输出哪种波形。它通常包括一个多路选择器,根据控制信号的高低电平或编码选择不同的波形输出路径。

3. **复位功能**:提供复位信号以重置系统状态,确保每次实验或测试的开始都能从预设状态开始。

4. **控制模块**:通过按键或输入信号,用户可以控制波形的选择和输出。这可能涉及到时序逻辑设计,处理输入信号并生成适当的控制信号。

5. **时钟输入**:FPGA设计通常依赖于时钟信号来同步其内部操作。时钟是所有数字系统的心脏,对于生成周期性的波形至关重要。

在方案选择中,本设计最终选择了基于FPGA和VHDL的方案,因为这种方式提供了更高的灵活性和可编程性,可以方便地修改和扩展波形生成逻辑,同时避免了传统方案中的电路复杂性和干扰问题。此外,通过计算机仿真和实际硬件验证,可以确保设计的正确性和稳定性。

总结来说,这个EDA设计信号发生器项目展示了VHDL语言在实现复杂数字系统中的强大能力,同时也体现了FPGA作为可重构硬件平台的优越性。这种设计不仅满足了教学和实验的需求,也为实际应用提供了可行的解决方案。通过这样的设计,学习者可以深入理解数字逻辑、信号处理以及硬件设计的原理。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2010-01-10 上传

2023-06-14 上传

2008-12-02 上传

2011-06-20 上传

2011-01-18 上传

2010-05-31 上传

guduhanyan

- 粉丝: 2

- 资源: 36

最新资源

- ghaction-publish-ghpages:将内容发布到GitHub Pages

- HTML5 Video Speed Control-crx插件

- 人工智能实验2020年秋季学期.zip

- PyPI 官网下载 | vector_quantize_pytorch-0.4.0-py3-none-any.whl

- form:将您的Angular2 +表单状态保留在Redux中

- Tensorflow_practice:딥러닝,머신러닝

- Dijkstra.rar_matlab例程_matlab_

- 任何点复选框

- 人工智能写诗.zip

- Parstagram:使用私有存储服务器模仿Instagram

- mod-1白板挑战牌卡片sgharms测试webdev资金

- Slack Panels-crx插件

- PyPI 官网下载 | vectorian-0.9.2-cp38-cp38-macosx_10_9_x86_64.whl

- react-card-component:React卡组件Libaray

- 人工智能与实践 bilibili.zip

- Architecture-Website