Arria V FPGA的Avalon-ST接口详解:PCIe协议设计与应用

需积分: 11 50 浏览量

更新于2024-07-18

1

收藏 1.66MB PDF 举报

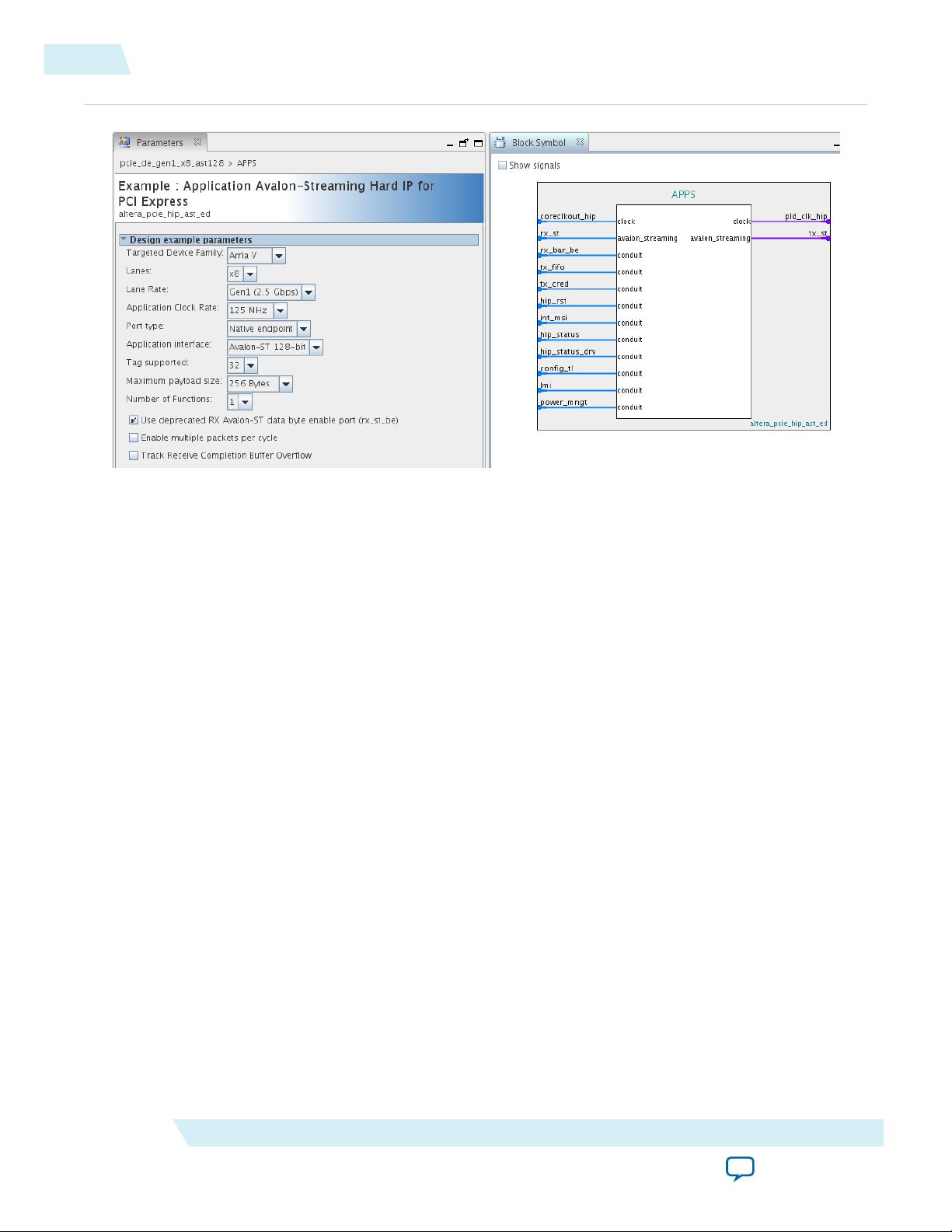

本文档主要介绍了Altera公司Arria V系列FPGA中的PCI Express (PCIe) 接口,特别是使用Avalon Streaming (Avalon-ST) 界面的配置方法和设计流程。Arria V FPGA集成了一个可配置的、硬化的PCIe协议栈,兼容PCI Express Base Specification 2.1或3.0标准,提供了高度灵活性,但同时也要求开发者对PCIe协议有深入理解。

文章详细内容包括:

1. **功能特性**:文档首先概述了Avalon-ST接口的特点,强调其灵活性以及与PCIe协议的兼容性。对于那些希望利用该接口进行PCIe设计的用户来说,这些特性是关键。

2. **版本更新**:提到了文档最后更新的时间和所针对的 Quartus Prime 设计套件版本,确保读者使用的是最新且最适用的信息。

3. **设备家族支持**:文档列出了Arria V系列FPGA的具体型号,帮助用户确定他们的硬件是否支持PCIe接口和Avalon-ST接口。

4. **配置选项**:介绍了不同配置的选择,包括可能的接口参数设置和性能等级推荐,以优化资源利用率。

5. **设计步骤**:

- **Qsys设计流程**:文档详细指导用户如何使用Quartus Prime Software中的Qsys工具进行系统级设计,包括创建系统架构、生成测试台和设计文件。

- **模拟与仿真**:通过模拟示例设计来验证接口的正确性和行为,这对于设计验证至关重要。

- **综合与编译**:解释了如何在Quartus Prime中合成设计,物理布局的理解,以及最终的编译过程。

- **修改与扩展**:指南中还包含了如何根据项目需求修改预设的示例设计,以及如何将PCIe IP核心作为单独组件通过IP Catalog导入到设计中。

6. **参数设置**:着重讨论了Avalon-ST系统的设置选项,如系统时钟、数据宽度等,这些设置直接影响到接口的性能和兼容性。

这份文档为Altera Arria V FPGA的用户提供了丰富的PCIe接口设计指南,包括从入门到高级应用所需的知识和技术细节,有助于用户高效地集成和调试PCIe功能到自己的设计中。对于那些希望在FPGA上实现PCIe通信的工程师来说,这是一个不可或缺的参考资源。

436 浏览量

143 浏览量

176 浏览量

2024-10-29 上传

164 浏览量

111 浏览量

143 浏览量

2024-10-29 上传

2024-10-29 上传

qq_35959980

- 粉丝: 0

- 资源: 1

最新资源

- encapsulamento

- 3D花瓶模型效果图

- learnC-4-macro

- 首页列表翻页教程网(带手机) v3.74

- Pan

- bdsegal.github.io

- FP-PSP-SERVER

- awesome-playgrounds:一系列令人敬畏的Xcode Swift游乐场,围绕诸如计算机科学,数学和物理等主题的交互性和指导性使用而集中

- login-mypage

- CKEditor v4.7.1

- engrid-scripts

- 麻将厅3D模型设计

- CodeFun:存放代码示例的地方

- automationpractice:与Azure DevOps集成的测试项目

- 塞恩·普勒

- prettyconf:用于设置代码分离的可扩展库