TMS320LF240x CPU内核结构解析:输入定标移位器与乘法器

需积分: 4 11 浏览量

更新于2024-08-01

收藏 701KB PDF 举报

"哈工大DSP课件---第3章CPU内核结构"

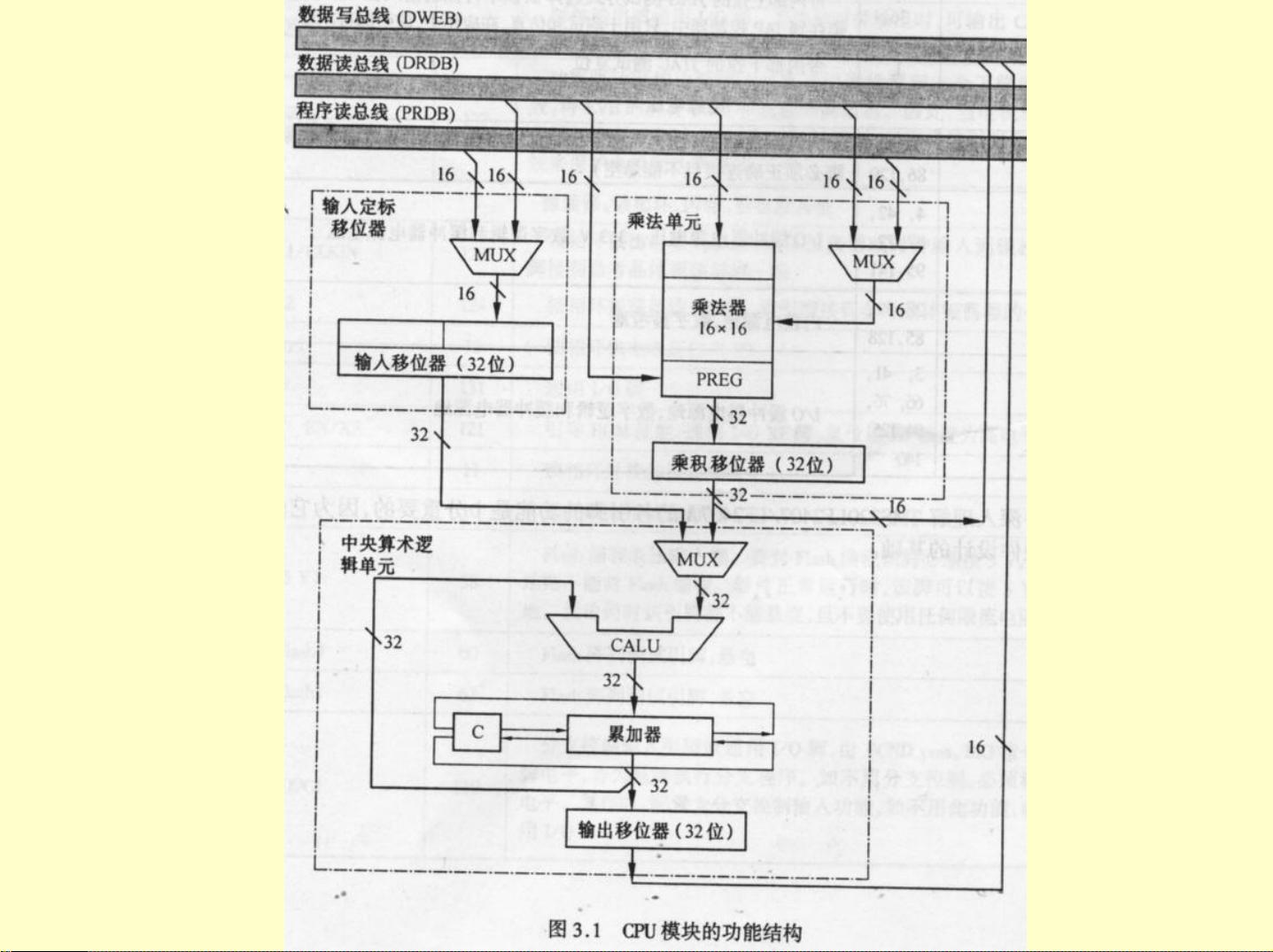

在数字信号处理(DSP)领域,理解CPU内核结构是至关重要的,尤其是对于哈工大的TMS320LF240x DSP芯片。本章主要探讨了CPU的功能模块和时钟模块,这两个部分构成了DSP处理器的核心。

3.1 CPU功能模块

CPU功能模块包含了输入定标移位器、中央算术逻辑单元(CALU)和乘法器。输入定标移位器的作用在于将16位的数据转换成32位,以便在CALU中进行更复杂的计算。这一过程支持0-15位的左移,并根据状态寄存器ST1的SXM位来决定是否进行符号扩展。乘法器是一个关键组件,能够在一个机器周期内完成16×16位的有符号或无符号乘法,产生的32位乘积被存储在乘积寄存器(PREG)中。

3.1.1 输入定标移位器

输入定标移位器不仅用于调整数据宽度,还在算术定标和逻辑操作中起到关键作用。它可以对输入数据进行左移,左移时LSB设为0,MSB根据SXM位进行符号扩展。移位的次数由指令中的常量或TREG中的值控制。

3.1.2 乘法器

哈工大的DSP芯片内建16×16位的硬件乘法器,能在单个机器周期内快速产生32位乘积。所有的乘法指令默认执行有符号乘法,乘积结果也是一个32位的二进制补码数。乘法器的两个输入来自TREG和数据或程序存储器,乘积结果则存储在PREG中,可以通过乘积定标移位器进行进一步处理。

3.1.3 乘积定标移位器

乘积定标移位器提供四种不同的移位方式,由状态寄存器ST1的PM位指定。这四种方式有助于执行乘法/累加操作、小数运算和小数乘积调整。例如,左移1位可以去除二进制补码乘法的额外符号位,而右移6位则可以对乘积进行定标,适用于累加器在128次乘积累加后的结果处理。

时钟模块虽然在提供的内容中没有详细描述,但在任何CPU设计中都是不可或缺的。时钟模块通常管理着整个系统的时序,包括时钟频率的生成和分配,确保各个模块协同工作,保证指令执行的准确性和实时性。

通过深入学习这些内容,我们可以了解到TMS320LF240x DSP芯片如何高效地执行数字信号处理任务。对于那些想要在DSP领域深入研究的人来说,理解CPU内核结构及其组件的工作原理是至关重要的,这有助于优化算法,提高系统性能。哈工大的这个DSP课件无疑为学习者提供了宝贵的教育资源。

2010-04-01 上传

2010-04-01 上传

115 浏览量

119 浏览量

111 浏览量

hnuhpu2009

- 粉丝: 0

最新资源

- 《ASP.NET 4.5 高级编程第8版》深度解读与教程

- 探究MSCOMM控件在单文档中的兼容性问题

- 数值计算方法在复合材料影响分析中的应用

- Elm插件支持Snowpack项目:热模块重载功能

- C++实现跨平台静态网页服务器

- C#开发的ProgaWeatherHW气象信息处理软件

- Memory Analyzer工具:深入分析内存溢出问题

- C#实现文件批量递归修改后缀名工具

- Matlab模拟退火实现经济调度问题解决方案

- Qetch工具:无比例画布绘制时间序列数据查询

- 数据分析技术与应用:Dataanalys-master深入解析

- HyperV高级管理与优化使用手册

- MTK6513/6575智能机主板下载平台

- GooUploader:基于SpringMVC和Servlet的批量上传解决方案

- 掌握log4j.jar包的使用与授权指南

- 基础电脑维修知识全解析