6 GS/s 高速数模转换器:InP HBT工艺提升SFDR至63 dB

12 浏览量

更新于2024-08-31

收藏 966KB PDF 举报

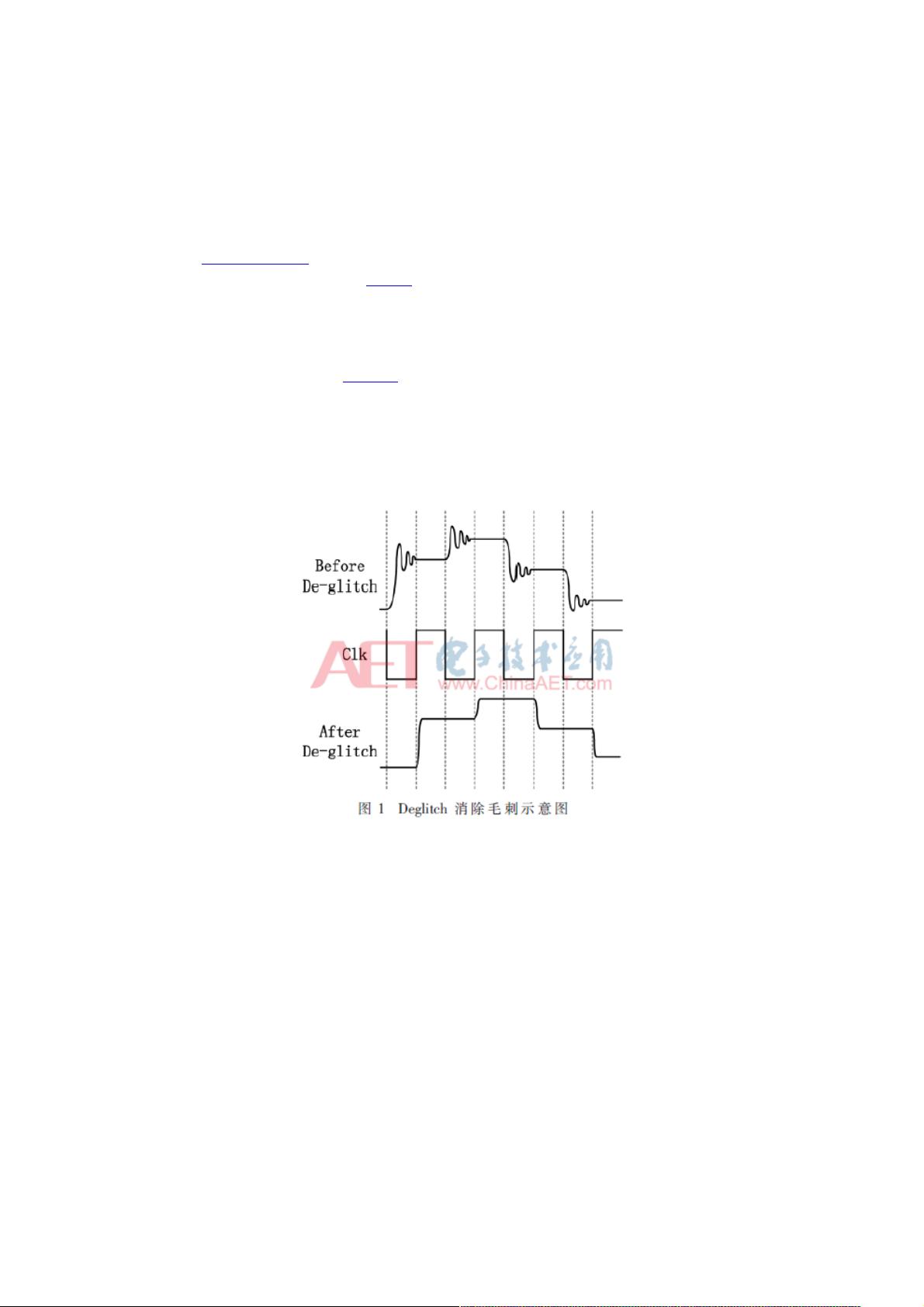

"本文介绍了一款基于0.7微米InP HBT工艺设计的12位6 GS/s高速电流舵型数模转换器(DAC),该设计通过改进电流源开关结构和引入去毛刺电路,显著提高了SFDR,达到63 dB以上。电路的非线性误差低,DNL为0.75 LSB,INL为0.5 LSB。去毛刺电路在高频下能提升SFDR 10 dB,优化了动态特性。"

高速数模转换器(DAC)在现代通信系统中扮演着至关重要的角色,特别是在宽带通信领域。12位分辨率和6 GS/s的采样率使得这款DAC成为高性能应用的理想选择。电流舵结构因其高线性度和快速响应而在高采样率DAC设计中被广泛采用。然而,这种结构在高频操作时面临谐波失真增加和输出阻抗不稳定的问题,同时,开关切换产生的毛刺会降低SFDR。

为了解决这些问题,设计者采用InP异质结双极晶体管(HBT)工艺,其ft高达280 GHz,提供了高速性能。通过优化电流源开关结构,提高了输出阻抗的稳定性和整体性能。此外,引入去毛刺(Deglitch)电路是一种创新策略,它可以有效地消除开关切换期间的毛刺,从而改善SFDR。仿真结果显示,该电路的DNL(差分非线性)达到了0.75 LSB,INL(积分非线性)为0.5 LSB,表明了极高的线性度。

去毛刺电路的工作原理是通过精确的采样时序控制,确保在DAC输出切换时保持恒定的模拟信号值,避免毛刺的出现。这不仅提升了第一奈奎斯特域内的SFDR,而且还能在不牺牲信号幅度和动态性能的情况下扩展到更高的频率范围。与传统的去毛刺技术相比,这种方法更注重第一奈奎斯特域内的性能优化,避免了信号衰减和频繁的电平切换。

SFDR是衡量 DAC 输出信号质量的关键指标,它表示在输出信号中最大无杂散功率与信号功率之间的差值,反映了转换器抑制谐波和噪声的能力。该设计的SFDR超过63 dB,意味着在宽频范围内,转换器能够产生非常纯净的模拟信号,这对于高分辨率的通信和信号处理应用至关重要。

这款基于InP HBT的12位6 GS/s DAC展示了优秀的性能,其创新的电路设计和去毛刺技术为高速、高精度的数模转换提供了新的解决方案,对于推动宽带通信系统的发展具有重要意义。

2020-10-15 上传

2019-08-16 上传

2018-09-24 上传

2019-08-17 上传

2021-03-06 上传

2021-03-20 上传

2020-07-08 上传

2021-03-06 上传

2021-03-04 上传

weixin_38516386

- 粉丝: 5

- 资源: 899

最新资源

- MATLAB新功能:Multi-frame ViewRGB制作彩色图阴影

- XKCD Substitutions 3-crx插件:创新的网页文字替换工具

- Python实现8位等离子效果开源项目plasma.py解读

- 维护商店移动应用:基于PhoneGap的移动API应用

- Laravel-Admin的Redis Manager扩展使用教程

- Jekyll代理主题使用指南及文件结构解析

- cPanel中PHP多版本插件的安装与配置指南

- 深入探讨React和Typescript在Alias kopio游戏中的应用

- node.js OSC服务器实现:Gibber消息转换技术解析

- 体验最新升级版的mdbootstrap pro 6.1.0组件库

- 超市盘点过机系统实现与delphi应用

- Boogle: 探索 Python 编程的 Boggle 仿制品

- C++实现的Physics2D简易2D物理模拟

- 傅里叶级数在分数阶微分积分计算中的应用与实现

- Windows Phone与PhoneGap应用隔离存储文件访问方法

- iso8601-interval-recurrence:掌握ISO8601日期范围与重复间隔检查