Altera设备中的IEEE 1149.1 (JTAG) 边界扫描测试

需积分: 13 57 浏览量

更新于2024-07-22

1

收藏 365KB PDF 举报

"这篇应用笔记介绍了在Altera设备中如何使用IEEE 1149.1(JTAG)边界扫描测试技术,旨在帮助用户在复杂的印刷电路板(PCB)设计中实现有效的测试策略,以应对传统测试方法的挑战。"

在电子工程领域,随着印制电路板(PCB)设计的复杂度日益增加,对全面测试的需求变得至关重要。随着表面贴装封装和PCB制造工艺的进步,板子变得更小,传统的测试方法,如外部探针和“钉床”测试夹具,难以实施。这导致了PCB节省的空间成本被传统测试方法增加的成本所抵消。

为了解决这一问题,1980年代,联合测试行动组(Joint Test Action Group,简称JTAG)制定了一种边界扫描测试(Boundary-Scan Testing, BST)的规范,后来被标准化为IEEE Std. 1149.1标准。这个测试架构允许高效地测试具有紧密引脚间距的PCB上的组件,解决了传统测试方法无法应对的难题。

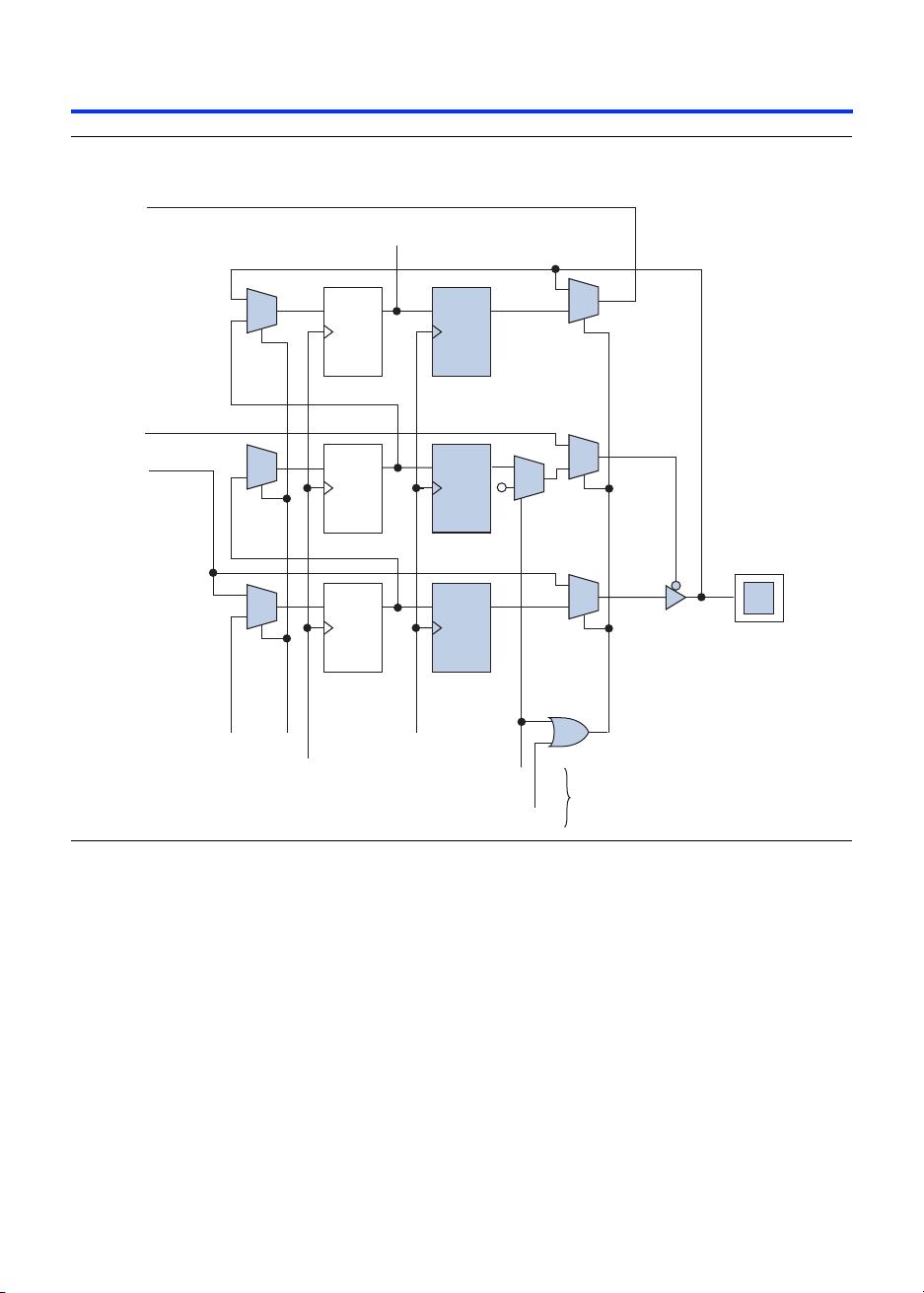

IEEE 1149.1,也称为JTAG,其核心是边界扫描链(Boundary-Scan Chain),它包含了一系列边界扫描单元(Boundary-Scan Cells, BSC)。这些BSC能够对引脚施加信号,或者在设备正常运行时捕获来自引脚或内核逻辑的数据。这种非侵入式的测试方法使得无需物理探针即可完成测试,大大提高了测试的便利性和效率。

在Altera设备中,应用JTAG技术进行边界扫描测试,可以实现以下功能:

1. **引脚功能验证**:BSCs可以模拟输入信号,检测输出,从而验证每个引脚的正确连接和功能。

2. **内部逻辑测试**:通过JTAG接口,可以访问并测试器件内部的逻辑单元,确保其在实际操作中的正确性。

3. **故障定位**:在生产测试阶段,若发现故障,JTAG可帮助定位具体是哪个BSC或内部逻辑出现问题。

4. **在线调试**:在系统运行时,JTAG可用于实时收集和分析数据,辅助调试过程。

5. **编程与配置**:JTAG还可以用于器件的编程和配置,尤其是对于现场可编程门阵列(FPGA)等可重构器件。

6. **系统级测试**:通过将多个设备连接到同一个JTAG链,可以进行整个系统级别的测试和故障排查。

IEEE 1149.1(JTAG)边界扫描测试为现代电子设计提供了一种强大的测试工具,它在减少测试成本、提高测试覆盖率和简化生产流程方面具有显著优势。在使用Altera设备时,掌握和利用JTAG技术是提升产品质量和可靠性的重要手段。

255 浏览量

2160 浏览量

226 浏览量

811 浏览量

点击了解资源详情

点击了解资源详情

139 浏览量

190 浏览量

磁场OS

- 粉丝: 38

- 资源: 625

最新资源

- WMAN633:2021年Spring与Rota博士进行的定量生态学

- playground:一种新型的虚拟事件平台:penguin:

- ember-audio:Ember插件,可与Web Audio API超级EZ一起使用

- 行业分类-设备装置-压缩机内部空间划分结构.zip

- 哈尔滨工业大学同义词词林扩展版.rar

- 305372complier2563

- NStudio-开源

- Battleship-Clone

- ember-share:一个Ember插件,可使用ngrok(https:ngrok.com)与世界分享您的本地Ember应用程序

- jena-workspace:用于Apache Jena代码的工作区域

- javascript-jquery:一个Java

- OpenCV for Unity 2.3.3-1,支持安卓,IOS,Windows,WebGL,Linux,MacOS

- 【参赛作品】低成本的智能家居联网控制解决方案-电路方案

- ember-artisans:在Ember.js中使用网络工作者的抽象层

- android-sdk_r24.4.1-windows.7z

- 易语言源码ACCESS数据库分类统计.rar