九人表决器电路设计:会议决策的数字逻辑实现

需积分: 26 88 浏览量

更新于2024-09-13

3

收藏 186KB DOC 举报

"九人表决器电路设计是一个数字逻辑电路课程设计项目,旨在设计一个能够处理最多九个人投票的表决器。该表决器考虑了弃权情况,并能根据投票结果显示‘否决、通过、再议’等字样,通过七段显示译码器展示投票人数。设计者需要掌握组合逻辑和时序逻辑电路,熟悉数字电路芯片的使用,并在实践中培养创新意识。"

在设计九人表决器的过程中,以下几个关键知识点得以体现:

1. 组合逻辑电路:表决器中的逻辑门(如AND、OR、NOT、NAND、NOR等)组合起来,实现对输入信号的逻辑运算,比如计算同意、反对和弃权的票数。

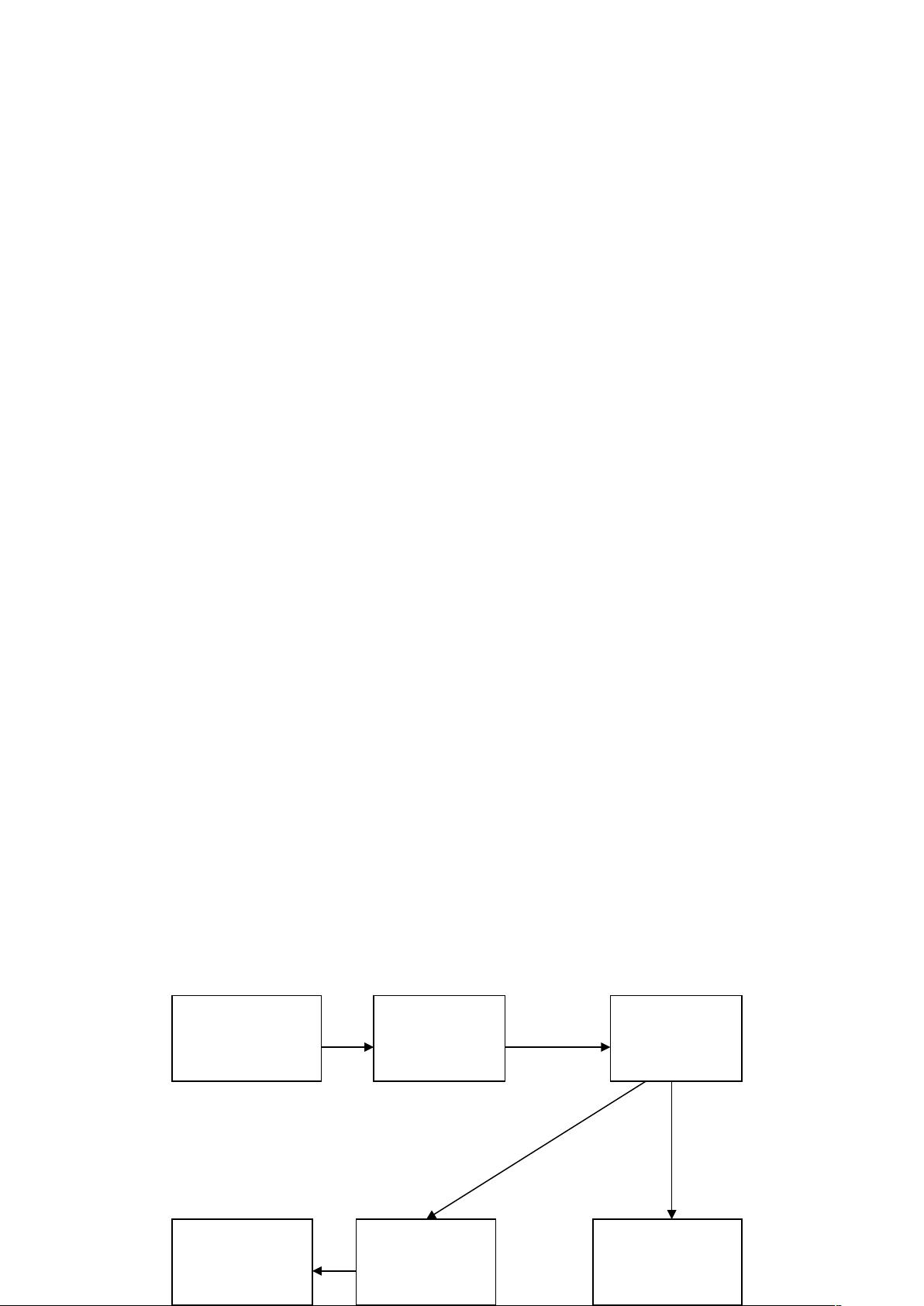

2. 时序逻辑电路:计数器用于记录每次投票的脉冲,累加投票数,这涉及到时序逻辑电路的设计,如同步计数器或异步计数器。

3. 数值比较器:比较器用于比较计数器的结果与预设阈值(例如,半数以上同意或反对),决定投票结果。

4. 七段显示译码器:将数字转换成对应的字符显示,如“同意”、“反对”、“弃权”,以便于用户直观了解投票状态。

5. 元器件选择:设计者需要考虑不同类型的数字集成电路(IC),如74系列或其他类似的逻辑门、计数器和译码器芯片,以满足电路的功能需求。

6. 电路优化:通过改进电路设计,使其逻辑更合理、更人性化,可能是通过简化逻辑路径、减少延迟或提高可靠性。

7. 创新意识:在设计中,可能需要创新解决方案,例如优化显示方式、增加额外功能,或者改进现有电路结构以提高效率。

8. 电路原理图绘制:设计者需绘制电路原理图,明确各个组件的连接关系,以便于制造和调试。

9. 硬件设计和实施:实际制作电路板,焊接元件,进行硬件测试,确保电路按预期工作。

10. 使用说明:编写详细的使用指南,解释如何操作表决器,包括如何发起投票、读取结果以及可能遇到的问题和解决办法。

11. 课程设计体会:设计者会从这个过程中学习到理论知识与实践操作的结合,增强问题解决能力,理解电路设计的复杂性和挑战性。

通过这个项目,学生不仅能巩固课堂所学,还能提升独立解决问题和创新思考的能力,为将来在电子工程或相关领域的职业生涯打下坚实基础。

2020-05-10 上传

2021-10-06 上传

2022-11-17 上传

2009-06-30 上传

点击了解资源详情

点击了解资源详情

点击了解资源详情

SiNianNaMoLei

- 粉丝: 0

- 资源: 1

最新资源

- [PHP.5.&.MySQL.5基础与实例教程.随书光盘].PHP.5.&.MySQL.5

- [PHP.5.&.MySQL.5基础与实例教程.随书光盘].PHP.5.&.MySQL.5

- Core J2EE Patter.pdf

- 深入浅出struts2

- S7-200自由口通讯文档

- 在tomcat6.0里配置虚拟路径

- LR8.1 操作笔记

- ASP的聊天室源码,可进行聊天

- RealView® 编译工具-汇编程序指南(pdf)

- Java连接Mysql,SQL Server, Access,Oracle实例

- 易我c++,菜鸟版c++教程。

- 软件性能测试计划模板

- SUN Multithread Programming

- 城市酒店入住信息管理系统论

- Learning patterns of activity using real-time tracking.pdf

- bus hound5.0使用 bus hound5.0使用 bus hound5.0使用