Verilog入门:组合电路与多路选择器详解

需积分: 10 58 浏览量

更新于2024-07-21

1

收藏 2.79MB PPT 举报

Verilog设计初步与入门是一份针对初学者的实用教程,专注于可编程逻辑器件(FPGA)设计中的Verilog语言基础。Verilog是一种硬件描述语言,常用于电子设计自动化(EDA)中,用于描述数字电路的行为。本教程主要分为四个部分:

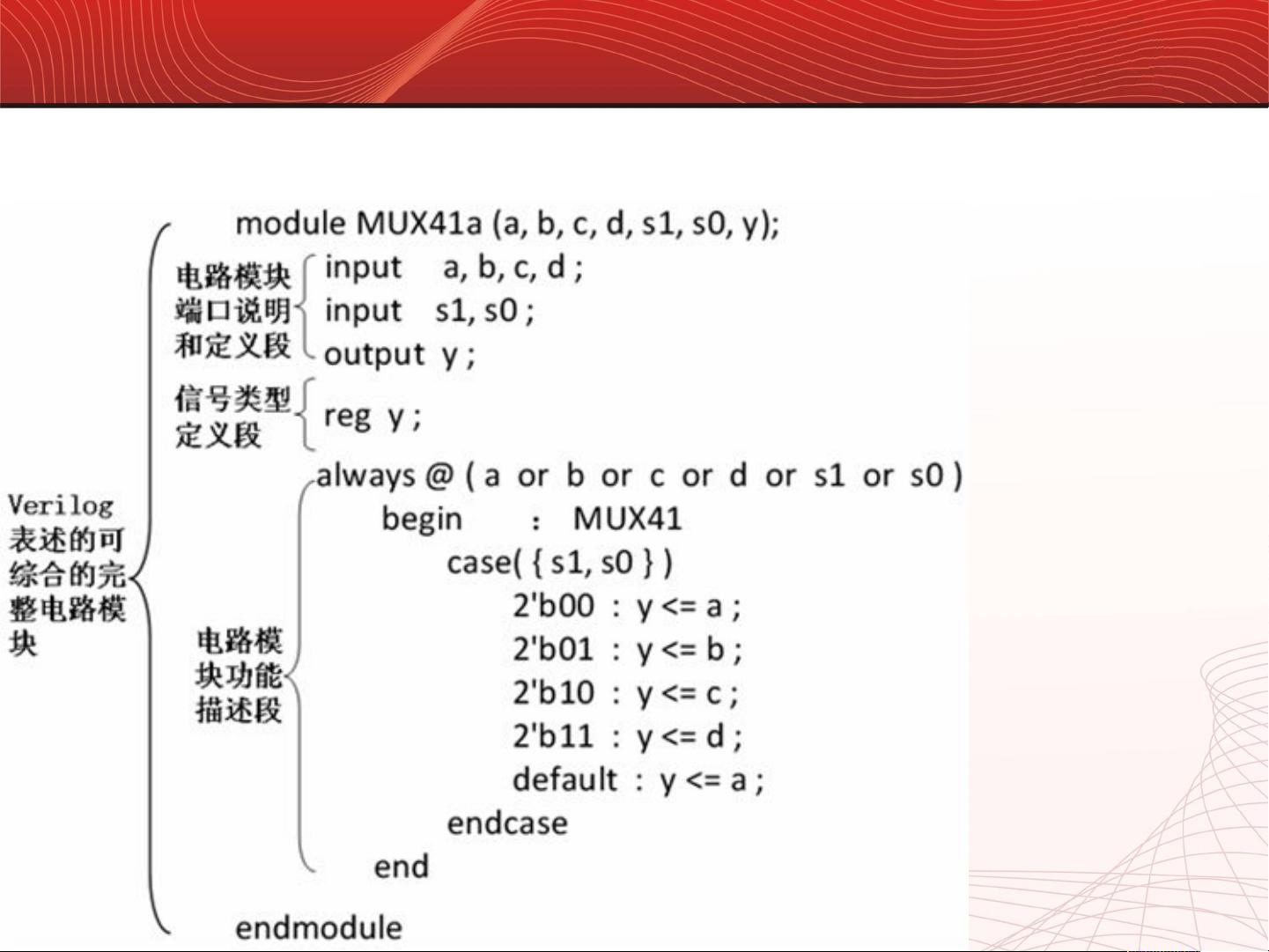

1. 组合电路的Verilog描述:这部分首先介绍了Verilog的基本概念,如模块表达式、端口语句、信号名和端口模式。通过实例,如12选1和24选1多路选择器,学员可以学习到如何使用`assign`语句和条件操作符来实现逻辑功能。对于12选1多路选择器,其基本结构是`module MUX21a(a, b, s, y);`,其中`input`端口接收输入信号,`output`端口输出结果,通过`assign`语句根据`s`的选择信号决定`y`的输出。

2. 寄存器和条件语句:在设计更复杂的电路时,如24选1多路选择器,引入了`reg`类型的变量,这表示内部状态存储,用`always @(event) begin ... endcase`结构配合`case`语句实现多路分支控制。在这个例子中,当多个输入条件同时变化时,Verilog会根据`case`中的匹配规则更新`y`的值。

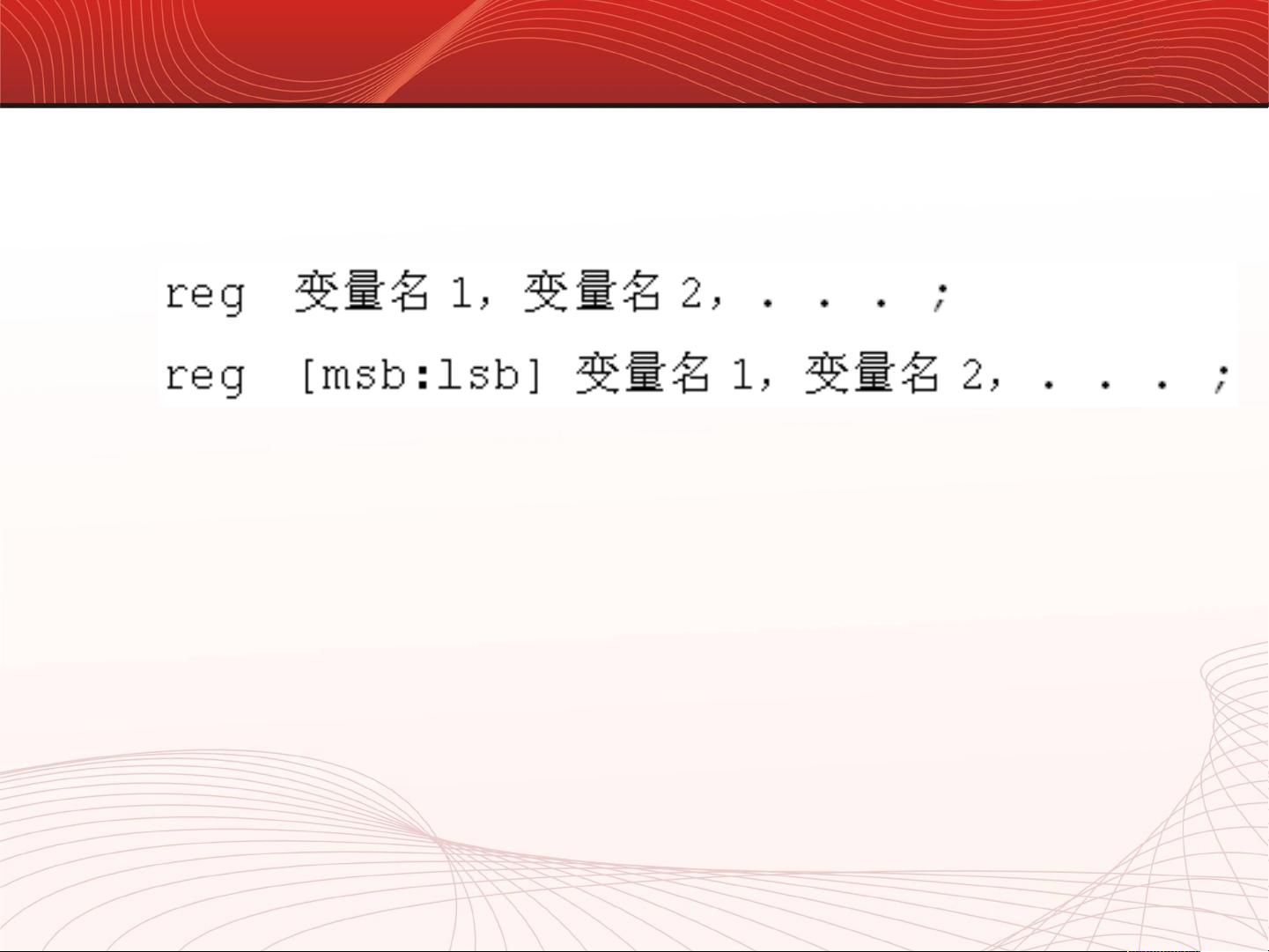

3. 数据类型和变量声明:课程强调了在Verilog中正确选择数据类型的重要性。`wire`是默认的数据类型,适用于无状态的信号;而`reg`用于需要保持状态的信号,如存储单元。例如,在`top`模块中,`rega`和`b`被声明为`reg`类型,以便在`initial`块中的时间延迟(`#5`)后更新它们的值。

4. 模块设计和模块间交互:最后,讲解了如何将一个模块(如多路选择器`DUT`)嵌入到更大的系统中。`wire`和`input/output`端口被用来连接不同模块之间的信号,确保数据流的正确传递。

这份教程提供了Verilog语言的入门知识,帮助学生理解基本的电路构建、数据类型选择以及模块化设计原则,为后续深入学习和实际应用打下坚实的基础。通过逐步实践,初学者能够熟练地使用Verilog进行FPGA设计。

2010-12-20 上传

2021-10-07 上传

2021-07-07 上传

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

点点海的风

- 粉丝: 5

- 资源: 3

最新资源

- 俄罗斯RTSD数据集实现交通标志实时检测

- 易语言开发的文件批量改名工具使用Ex_Dui美化界面

- 爱心援助动态网页教程:前端开发实战指南

- 复旦微电子数字电路课件4章同步时序电路详解

- Dylan Manley的编程投资组合登录页面设计介绍

- Python实现H3K4me3与H3K27ac表观遗传标记域长度分析

- 易语言开源播放器项目:简易界面与强大的音频支持

- 介绍rxtx2.2全系统环境下的Java版本使用

- ZStack-CC2530 半开源协议栈使用与安装指南

- 易语言实现的八斗平台与淘宝评论采集软件开发

- Christiano响应式网站项目设计与技术特点

- QT图形框架中QGraphicRectItem的插入与缩放技术

- 组合逻辑电路深入解析与习题教程

- Vue+ECharts实现中国地图3D展示与交互功能

- MiSTer_MAME_SCRIPTS:自动下载MAME与HBMAME脚本指南

- 前端技术精髓:构建响应式盆栽展示网站