0.25μm工艺下高性能采样保持电路设计提升高速ADC性能

77 浏览量

更新于2024-08-30

收藏 191KB PDF 举报

随着数字信号处理技术的飞速发展,模数转换器(ADC)作为模拟与数字世界之间的关键接口,其性能要求日益提高,特别是在低电压、高速度的场景中。本文针对这一需求,设计了一种专为高速ADC应用的采样保持电源电路。采样保持电路作为流水线ADC前端的重要组成部分,能够有效减少采样歪斜问题,确保信号的准确转换。

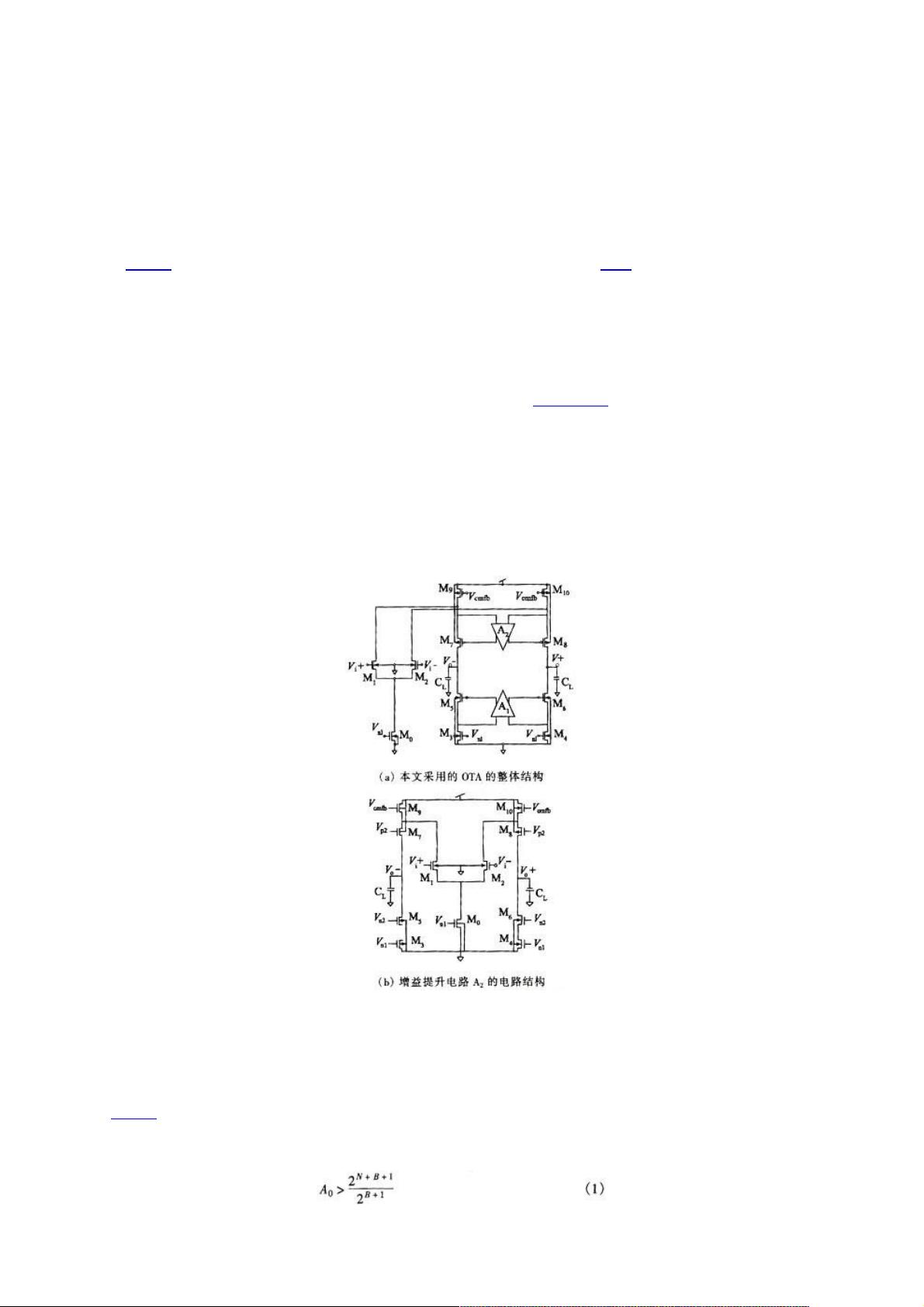

设计工作基于TSMC 0.25μm CMOS工艺,该电路的核心是一个具有高增益和高带宽的运算放大器(OTA)。作者特别选择了折叠式共源共栅的运放结构,如图1(a)所示,这种结构在低电压环境下表现优秀,兼顾高速、高频和低功耗特性。输入端采用NMOS管以减少寄生电容的影响,确保信号处理的精确性。

文章进一步探讨了增益自举电路,如图1(b),避免了单端输入-单端输出运放的功耗增加和电流镜结构可能带来的镜像极点问题。通过这种方式,放大器A2采用NMOS管以保证足够的输出摆幅,同时保持良好的频率响应。

设计的采样保持电路旨在构建一个适用于10位,100MS/s的流水线ADC,这意味着电路需要满足高分辨率和高速率的需求。在设计过程中,重点考虑了跨导运算放大器的结构选择,以及其性能参数如增益、带宽、噪声等因素,这些都是决定采样保持电路性能的关键因素。

通过仿真分析,文章详尽展示了设计过程和结果,为高性能的高速ADC系统提供了重要的电路支撑。本文的研究成果对于提升ADC的整体性能,尤其是在高速、低功耗应用中的稳定性,具有重要意义。

622 浏览量

161 浏览量

551 浏览量

282 浏览量

598 浏览量

302 浏览量

185 浏览量

353 浏览量

395 浏览量

weixin_38506182

- 粉丝: 3

最新资源

- VB通过Modbus协议控制三菱PLC通讯实操指南

- simfinapi:R语言中简化SimFin数据获取与分析的包

- LabVIEW温度控制上位机程序开发指南

- 西门子工业网络通信实例解析与CP243-1应用

- 清华紫光全能王V9.1软件深度体验与功能解析

- VB实现Access数据库数据同步操作指南

- VB实现MSChart绘制实时监控曲线

- VC6.0通过实例深入访问Excel文件技巧

- 自动机可视化工具:编程语言与正则表达式的图形化解释

- 赛义德·莫比尼:揭秘其开创性技术成果

- 微信小程序开发教程:如何实现模仿ofo共享单车应用

- TrueTable在Windows10 64位及CAD2007中的完美适配

- 图解Win7搭建IIS7+PHP+MySQL+phpMyAdmin教程

- C#与LabVIEW联合采集NI设备的电压电流信号并创建Excel文件

- LP1800-3最小系统官方资料压缩包

- Linksys WUSB54GG无线网卡驱动程序下载指南