简易计时闹钟Verilog实现-亢红梅第四次大作业

需积分: 9 76 浏览量

更新于2024-09-05

收藏 866KB PDF 举报

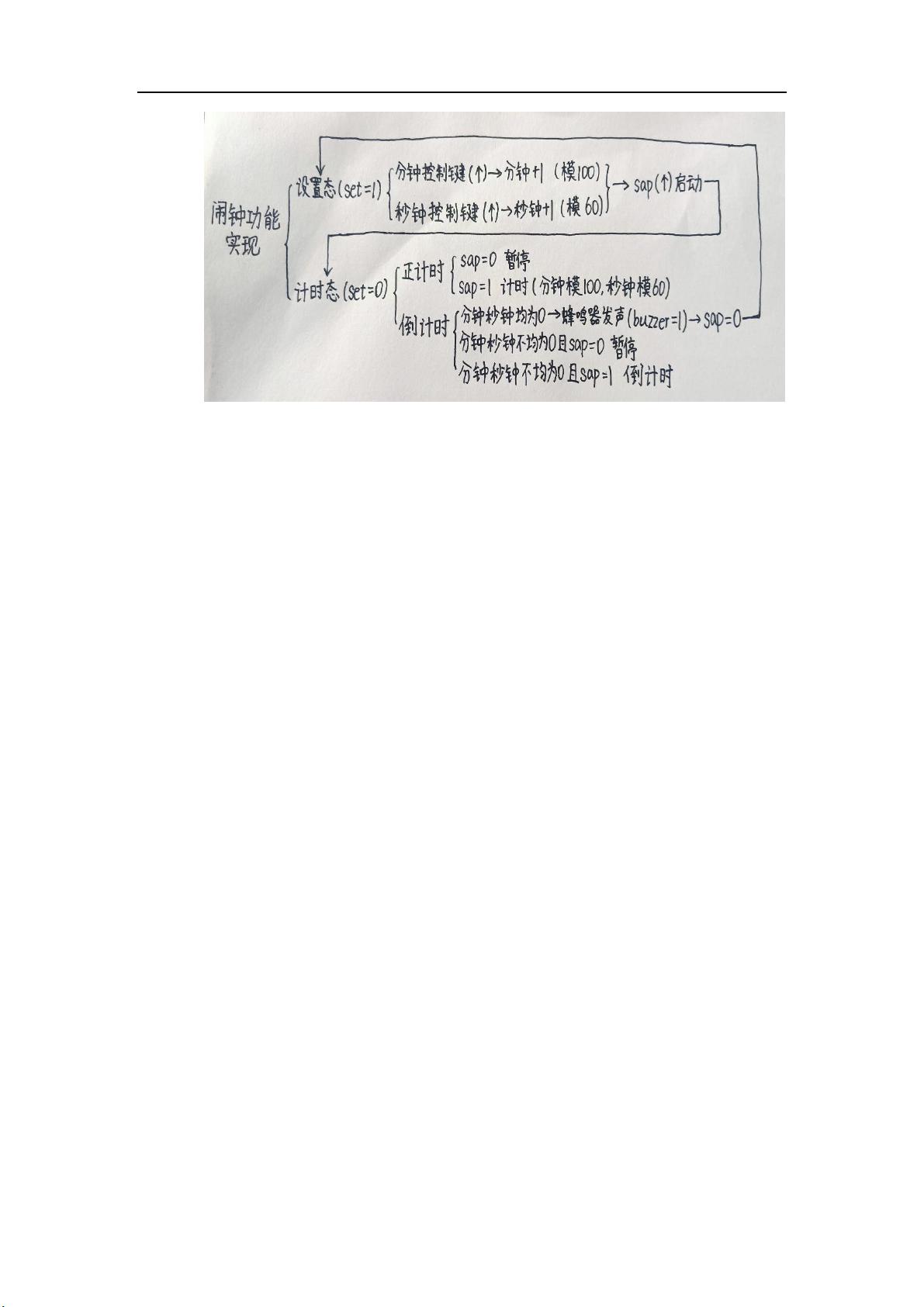

"报告介绍了使用Verilog语言实现一个简易计时闹钟的设计,该计时闹钟具有四位数码管显示分钟和秒,以及三个控制按键,包括分键、秒键和启动/暂停键。功能包括设置态和计时态,允许用户设定时间并进行正计时或倒计时。在设置态下,分秒键可调整时间,启动/暂停键开始计时。正计时可暂停,倒计时到零时发出蜂鸣警示。设计思路涉及将闹钟分为设置态和计时态两个模块,通过输入信号控制输出的分钟和秒显示及蜂鸣器状态。"

在Verilog设计中,这个计时闹钟的核心逻辑可以分为以下几个部分:

1. 设置态模块:当分钟键和秒键同时被按下时,系统进入设置态,此时分钟和秒被清零。在此状态下,每次按下分键,分钟值加1,超过99则回零;同理,按下秒键,秒加1,超过59则回零。系统保持在设置态,直到启动/暂停键被按下,此时当前设置的时间值被保存。

2. 计时态模块:一旦启动/暂停键被按下,系统进入计时态。在这个状态下,根据初始设置值(0000表示正计时,非零值表示倒计时)开始计时。在正计时模式,启动/暂停键可暂停和恢复计时。在倒计时模式,当计时到达零时,蜂鸣器会发出警示,直到再次按下启动/暂停键,系统返回设置态,并显示之前设置的时间,同时蜂鸣器停止发声。

3. 输入和输出信号处理:系统接收四个输入信号:分钟控制键mc、秒控制键sc、启动/暂停键sap和时钟脉冲控制自动计时clk。根据这些信号,产生五个输出:分钟十位mten、分钟个位munit、秒钟十位sten、秒钟个位sunit以及蜂鸣器工作状态buzzer。在Verilog代码中,这些信号的处理将涉及到组合逻辑和时序逻辑。

4. 状态机实现:为了实现设置态和计时态的切换,可以采用状态机(FSM,Finite State Machine)设计方法。状态机包括两个状态:设置态(SET)和计时态(TIMER)。状态机根据输入信号的变化更新其状态,并根据当前状态产生相应的输出。

5. 计数器设计:分钟和秒的计数可以通过计数器实现。在正计时中,计数器递增;在倒计时中,计数器递减。计数器需要能够处理溢出情况,例如分钟超过99或秒超过59时进行重置。

6. 条件判断和逻辑操作:Verilog代码中会包含多个if-else语句来处理不同的操作,如判断是否在设置态、判断计时方向(正计时或倒计时)、判断是否需要清零或加1等。

7. 时钟同步:计时器的更新通常与时钟信号同步,确保计时的精确性。在Verilog中,这通常通过posedge或negedge时钟边沿检测来实现。

8. 综合和仿真:完成Verilog代码编写后,需要进行逻辑综合,将其转化为硬件描述语言,然后通过硬件仿真验证其功能是否符合预期。

这个计时闹钟设计涉及到基础的数字逻辑、状态机设计、计数器构造以及输入输出信号的处理,是Verilog学习中的一个典型应用实例。通过这个项目,开发者可以深入理解数字系统的设计原理,并实践Verilog编程技巧。

174 浏览量

365 浏览量

292 浏览量

2022-09-24 上传

398 浏览量

174 浏览量

2019-09-17 上传

weixin_42950619

- 粉丝: 0

最新资源

- Kribosw 主文件分析与应用

- GitHub项目树状导航插件octotree发布新版

- 农机服务效益分析Excel模板下载

- cLaunch v12.04:基于tdLaunch代码的PocketPC Today屏幕启动器

- 创建自定义npm包页面的Node.js命令行工具

- Red5 实例演示与压缩工具应用解析

- CS研究生分享学习数据结构与算法的旅程

- 大型公关营销活动成功案例分析与参考指南

- WebXR精选游戏体验:谷歌师兄的leetcode刷题笔记

- HTML中压缩包子文件的使用技巧

- 农村义务教育贫困生免杂费资金分配Excel模板

- Academic Kickstart:搭建个性化学术网站指南

- 易语言实现数据库与树形框无限分类管理

- 房产手机应用演示程序

- 脚本引擎:一种多功能命令行工具,支持Python与Shell脚本

- Python实现对抗熵最小化在语义分割领域自适应研究