Verilog HDL入门教程:硬件描述语言基础

需积分: 10 106 浏览量

更新于2024-07-31

收藏 8.85MB PPT 举报

"这是一份关于Verilog HDL基础知识的PPT教程,旨在帮助初学者了解和学习硬件描述语言。"

Verilog HDL是硬件描述语言的一种,它为电子设计人员提供了一种强大的工具,用于描述和建模复杂的数字逻辑系统。作为与电子设计自动化(EDA)工具交互的语言,HDL的主要作用是创建设计文件,这些文件可以被用于建立行为级的仿真模型,并最终转化为实际的电路实现。

1.1 硬件描述语言HDL

HDL允许设计者以一种结构化的高级语言来表述电路的行为和结构,这使得对电路逻辑的理解和分析变得简单。通过HDL,设计可以被仿真,以验证其功能正确性。然后,这些设计可以被自动综合成符合特定工艺要求的逻辑网表,进一步生成电路布局,最终用于ASIC(应用专用集成电路)芯片的设计,或者编程到CPLD(复杂可编程逻辑器件)和FPGA(现场可编程门阵列)中。

1.2 Verilog HDL历史

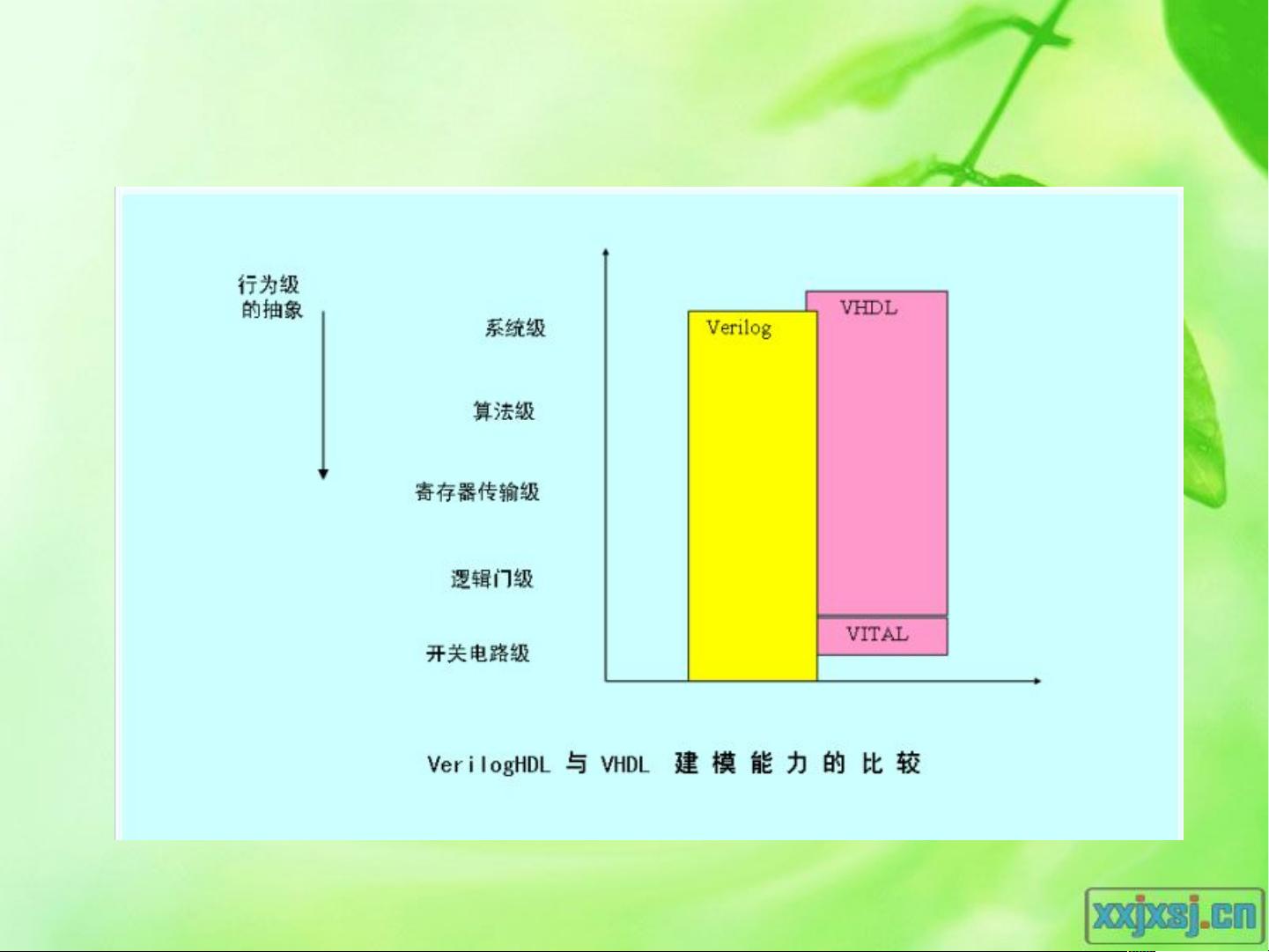

Verilog HDL起源于C语言,因此它的语法和结构与C语言有诸多相似之处,这使得对于熟悉C语言的人来说,学习Verilog相对较为容易。尽管VHDL比Verilog出现得晚,但它更早被标准化(IEEE 1706-1985)。然而,Verilog由于其简洁性和易用性,逐渐成为应用最为广泛的硬件描述语言之一。

Verilog HDL的使用带来了很多好处。首先,它使得电路功能的描述直观,便于计算机进行逻辑分析。其次,设计与实现过程可以分开,使得设计者可以专注于逻辑设计,而将电路实现留给EDA工具。此外,由于逻辑设计与具体的制造工艺分离,设计可以在不同的工艺条件下重复使用。最后,Verilog HDL使得多个人协同工作,高效设计大规模的复杂逻辑电路成为可能。

Verilog HDL的应用包括行为级建模、功能仿真、时序分析和逻辑综合等。设计者可以使用它来描述电路的连接、功能、抽象级别和时序特性,以及并行性。通过这些特性,Verilog HDL成为现代电子设计不可或缺的一部分,尤其在数字系统设计领域,其重要性不言而喻。

这份PPT教程涵盖了Verilog HDL的基础知识,是初学者了解这一语言的宝贵资源,包括其基本概念、历史和用途,为深入学习和实践打下坚实的基础。

125 浏览量

421 浏览量

点击了解资源详情

108 浏览量

104 浏览量

2022-09-24 上传

2011-04-19 上传

684 浏览量

cailn2000

- 粉丝: 0

- 资源: 2

最新资源

- Wikipedia Link Expander-crx插件

- mod_gnutls:基于GnuTLS的Apache HTTPD的TLS模块

- java jspt包.rar

- gomail:使用redis作为go(golang.org)编写的数据存储的邮件发件人

- 神经网络智能控制系统的研发.rar

- minimal-move-typing

- CSS3仿Facebook表情包图标动画特效

- IOCP方式实现异步套接字源码 v2.0 支持多线程-易语言

- Condensed Grid Bookmarks-crx插件

- eirini版本:Eirini项目的Helm版本

- HT32_STD_5xxxx_FWLib_v017_5137.zip

- iOSInterviewquestions:interview:laptop::woman_technologist_light_skin_tone:iOS面试问题摘要

- PBJVision(iPhone源代码)

- The Helper+ by TheFunnelToolbox.com-crx插件

- 易语言鼠标连发器-易语言

- facial_expression_reg