基于FPGA的5级流水线CPU设计与实现

需积分: 15 29 浏览量

更新于2024-07-28

1

收藏 1.59MB DOC 举报

"5级流水CPU设计与实现基于FPGA和VHDL"

本文档详细阐述了一种使用VHDL语言在FPGA上实现的5级流水线CPU的设计过程。5级流水线CPU是一种优化处理器性能的技术,它将CPU的工作流程分为五个阶段:取指(IF)、译码(ID)、执行(EX)、访存(MA)和回写(WB),每个阶段都在不同的时间片中执行,从而提高指令执行的速度。

在设计过程中,采用了自顶向下和模块化的设计策略。首先,设计者通过Quartus II,一款由Altera公司开发的FPGA设计软件,来定制和集成各个功能单元。这些单元包括取指部分(IF),负责从内存中读取指令;译码部分(ID),解析指令并准备操作;执行部分(EX),执行指令操作;前向部分(FU),用于数据前向传递以避免流水线中的数据冲突;访存部分(MA),处理内存访问请求;回写部分(WB),将执行结果写回到寄存器或内存;以及冲突检测部分(HD),确保流水线中没有数据冲突。

时序设计是整个CPU设计的关键,需要精确计算各阶段的时间延迟以保证流水线的顺畅运行。在概念设计阶段,设计者会确定每个阶段的基本操作和它们之间的关系。而在结构级设计阶段,会进一步细化逻辑结构,包括总体逻辑结构和关键分模块结构设计,如控制逻辑、算术逻辑单元(ALU)等。

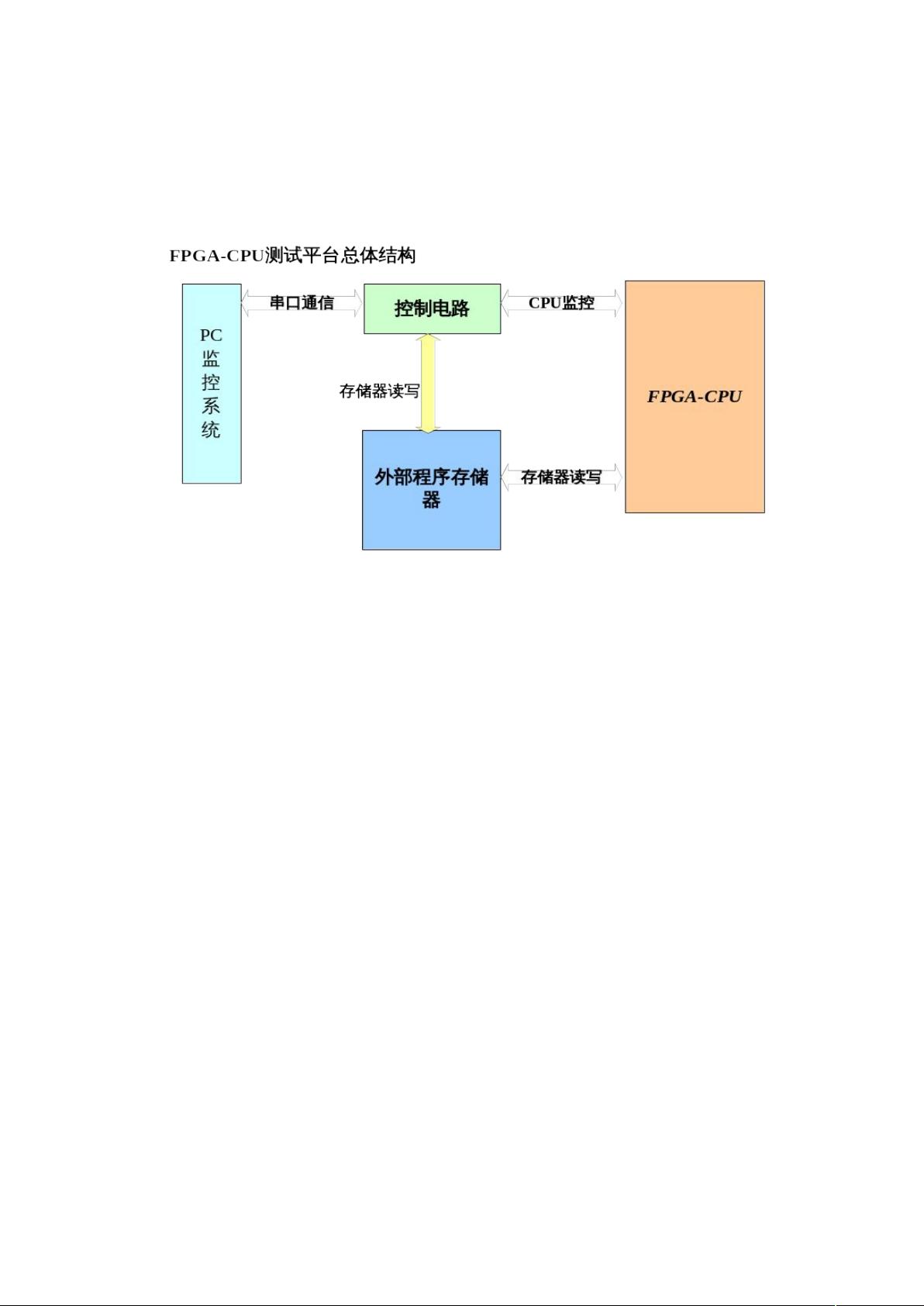

测试报告部分详细描述了如何对设计进行验证。这通常包括编写初始化程序来测试CPU的各个功能,并分析测试结果以评估其性能。通过比较实际运行情况与预期行为,可以判断CPU是否正确实现了五级流水线操作,并能有效地执行指令。

实验总结强调了FPGA技术在CPU设计中的优势,如灵活性、可靠性及可扩展性。这种设计方法使得CPU可以根据具体需求进行定制,适应不同的应用场景。此外,实验者在设计过程中不仅加深了对硬件和软件交互的理解,还提升了综合运用计算机基础知识和专业技能的能力。

关键词:FPGA,CPU,Quartus II,流水线,VHDL

通过这个项目,学生不仅学习了硬件描述语言VHDL,还掌握了FPGA上的CPU设计原理和实践,这为他们未来在嵌入式系统、数字逻辑设计等领域的工作打下了坚实的基础。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2024-05-19 上传

2021-02-10 上传

2016-03-19 上传

150 浏览量

168 浏览量

2024-08-27 上传

weinidan

- 粉丝: 0

- 资源: 2

最新资源

- 火炬连体网络在MNIST的2D嵌入实现示例

- Angular插件增强Application Insights JavaScript SDK功能

- 实时三维重建:InfiniTAM的ros驱动应用

- Spring与Mybatis整合的配置与实践

- Vozy前端技术测试深入体验与模板参考

- React应用实现语音转文字功能介绍

- PHPMailer-6.6.4: PHP邮件收发类库的详细介绍

- Felineboard:为猫主人设计的交互式仪表板

- PGRFileManager:功能强大的开源Ajax文件管理器

- Pytest-Html定制测试报告与源代码封装教程

- Angular开发与部署指南:从创建到测试

- BASIC-BINARY-IPC系统:进程间通信的非阻塞接口

- LTK3D: Common Lisp中的基础3D图形实现

- Timer-Counter-Lister:官方源代码及更新发布

- Galaxia REST API:面向地球问题的解决方案

- Node.js模块:随机动物实例教程与源码解析