"Vivado实现七段数码管学号显示及计数器功能的设计与实验报告"

需积分: 5 12 浏览量

更新于2024-01-16

11

收藏 916KB PDF 举报

本实验基于Vivado实现了七段数码管的显示,并通过Verilog编程实现了学号的显示以及其原理。本次实验是《EDA原理及应用》课程的一部分,设计内容为控制七段数码管的显示。实验者为SUN,就读于北京化工大学。

实验内容分为三个部分。首先是静态显示一个数字,如11111111,并可通过开关切换显示为22222222。其次是静态显示学号后8位。最后是显示计数值,范围从0到100,以0.1秒的时间递增。实验所需的器件包括硬件开发板xc7a75tfgg484和Vivado。

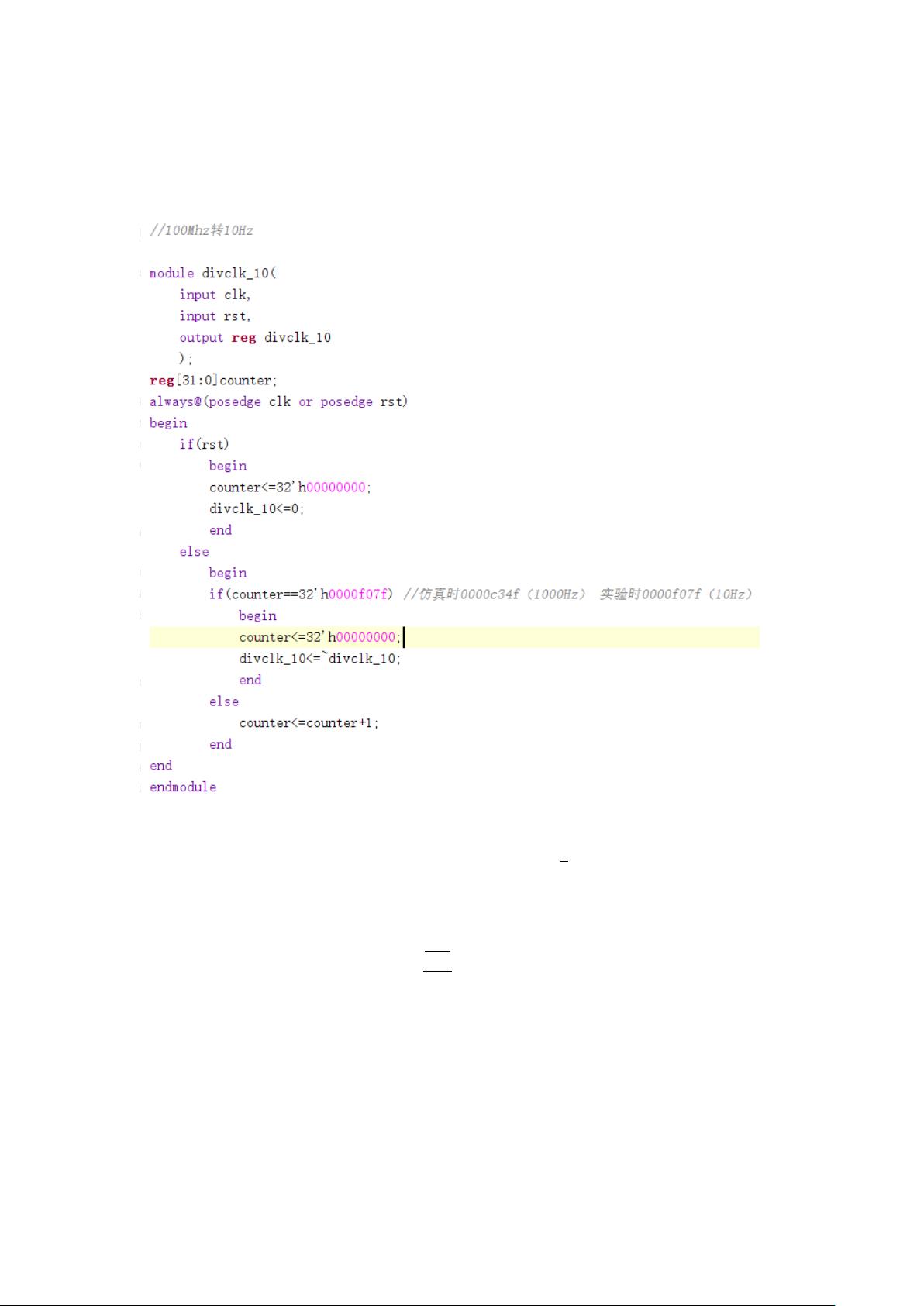

实验的具体过程如下。首先是实验设计思路。实验需要的频率为扫描频率,即人眼无法分辨的频率。因此需要将实验板提供的100MHz分频为所需频率,即分频器,且分频因子取61567。然后确定实验的输入端口与输出端口的数量,即5个输入端口,15个输出端口。输入端口包括rst、clk和[2:0] BTN,输出端口包括[7:0] pin和[6:0] shuma1。其中[7:0] pin端口负责送片选信号,[6:0] shuma1端口负责送段码。同时,通过8进制计数器实现了数字8的显示。

接下来是Verilog编程的实现。通过Verilog编程,实现了七段数码管的控制显示。在编程中,需要考虑时序逻辑和组合逻辑的设计。时序逻辑需要考虑时钟信号的控制和寄存器的使用,而组合逻辑需要根据输入信号来计算输出信号的逻辑关系。在学号的显示原理中,通过Verilog编程,实现了静态显示学号后8位的功能。

实验的最终效果是成功的。七段数码管能够按照设计要求显示相应的数字和学号后8位,并且能够正确显示计数值从0到100的变化,且递增时间为0.1秒。在实验中,硬件开发板xc7a75tfgg484和Vivado软件都发挥了重要作用,保障了实验的顺利进行。

总的来说,这次实验通过Vivado实现了七段数码管的显示,并通过Verilog编程实现了学号的显示,加深了对EDA原理的理解和应用。同时,实验中的设计思路和器件的选取也得到了实际的运用。这对于课程的学习和理论知识的巩固具有重要的意义。

STDRM

- 粉丝: 0

- 资源: 4

最新资源

- Control App for ESI MAYA22 USB:这是ESI MAYA22 USB音频接口的控制应用程序-开源

- phonebook_backend:电话簿的后端React APP

- CHIP8

- learn-mysql

- form-data-helper:替换 FormData 对象的 Javascript 插件。 用例

- 行业分类-设备装置-同步媒体处理.zip

- link-rest-dropwizard:一个简单的项目,演示将LinkRest与Dropwizard一起使用

- MediaPcInstaller:将grub2,Lakka和OpenElec安装到磁盘并设置为启动

- v-date-picker

- flutter-disenos-seccion8:Flutter课程的全新第8节

- 易语言聊天菜单源码-易语言

- Methods-of-collecting-and-processing-data-from-the-Internet

- 行业分类-设备装置-可高效稳定拔除钢结构体钢板桩的水利湖泊防洪堤修建机.zip

- welcome:xyao99的主页!

- request-api:简单的要求

- certifiacte-generator:在线证书生成器