异步FIFO设计详解与应用实例

需积分: 42 181 浏览量

更新于2024-07-26

收藏 844KB PDF 举报

本资源是一份由深圳市华为技术有限公司研究管理部文档中心编写的关于FIFO(First-In-First-Out,先进先出)的深入探讨文档,名为“异步FIFO解决方案”。该文档详细介绍了FIFO在跨时钟域应用中的关键特性,特别关注了空和满信号的产生机制,以及如何确保FIFO的稳定性和正确操作。

文档首先从引言开始,概述了FIFO的基本概念和在通信系统中的重要作用。然后,分为两大部分:同步FIFO和异步FIFO的设计。同步FIFO通常在时钟同步的系统中使用,设计部分讨论了读写地址和使能信号的生成,以及空满标志的产生,强调了它们对数据传输的准确性和一致性的重要性。

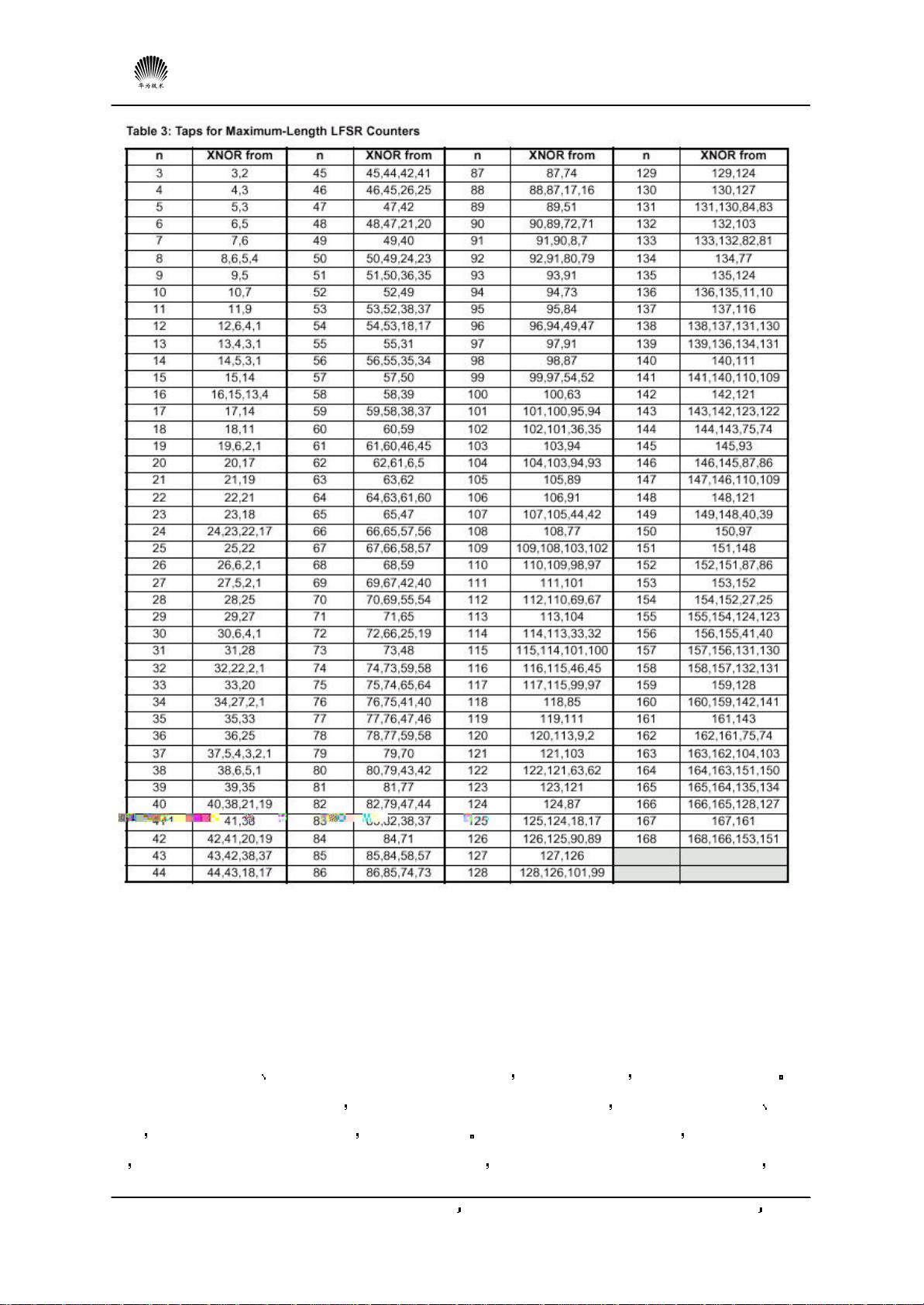

异步FIFO的设计部分更加复杂,因为需要处理不同时钟域之间的协调。这里详细解释了如何实现空和满信号的几乎空/几乎满状态,并通过逻辑分段如LFSR(线性反馈移位寄存器)来确保这些信号的准确性。此外,文档还涉及了双端口RAM在FIFO结构中的应用,以及针对FIFO稳定性的分析,包括自我保护机制和解决可能产生的不定态传播问题的方法。

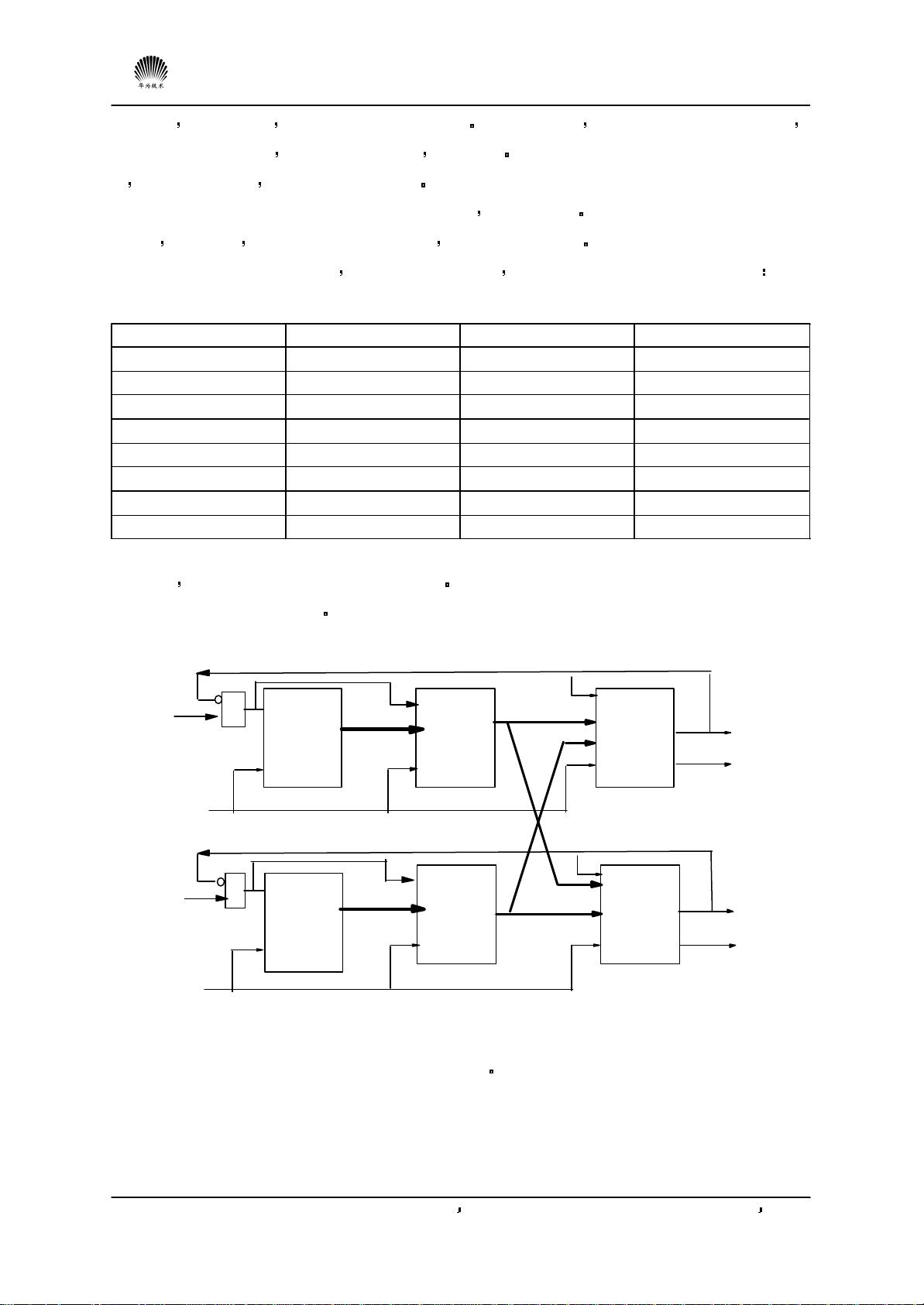

为了增强理解和实用性,文档还包含了一系列图解,如读写时序图、信号状态机示意图、位宽变换示意图等,直观展示了FIFO的工作原理和实际操作流程。附录部分提供了一些应用实例,例如位宽变换FIFO和同步FIFO的实际设计案例,帮助读者更好地理解和应用这些理论知识。

这份文档不仅提供了FIFO设计的基本原则,还深入探讨了异步FIFO的特殊挑战及其解决方案,对于从事嵌入式系统设计、硬件工程师或对FIFO工作原理感兴趣的读者来说,具有很高的参考价值。由于其详尽的内容和实用的指导,这份文档适合用于教学、研究或工程实践中的设计决策和优化。

点击了解资源详情

246 浏览量

230 浏览量

2020-10-23 上传

139 浏览量

2015-08-08 上传

sunny2096

- 粉丝: 0

最新资源

- C#实现程序A的监控启动机制

- Delphi与C#交互加密解密技术实现与源码分析

- 高效财务发票管理软件

- VC6.0编程实现删除磁盘空白文件夹工具

- w5x00-master.zip压缩包解析:W5200/W5500系列Linux驱动程序

- 数字通信经典教材第五版及其答案分享

- Extjs多表头设计与实现技巧

- VBA压缩包子技术未来展望

- 精选多类型导航菜单,总有您钟爱的一款

- 局域网聊天新途径:Android平台UDP技术实现

- 深入浅出神经网络模式识别与实践教程

- Junit测试实例分享:纯Java与SSH框架案例

- jquery xslider插件实现图片的流畅自动及按钮控制滚动

- MVC架构下的图书馆管理系统开发指南

- 里昂理工学院RecruteSup项目:第5年实践与Java技术整合

- iOS 13.2真机调试包使用指南及安装