FPGA数字钟设计与实现教程

需积分: 9 157 浏览量

更新于2024-07-17

收藏 1.16MB DOCX 举报

"Lab2 FPGA数字钟设计实验_Q17_V2.docx"

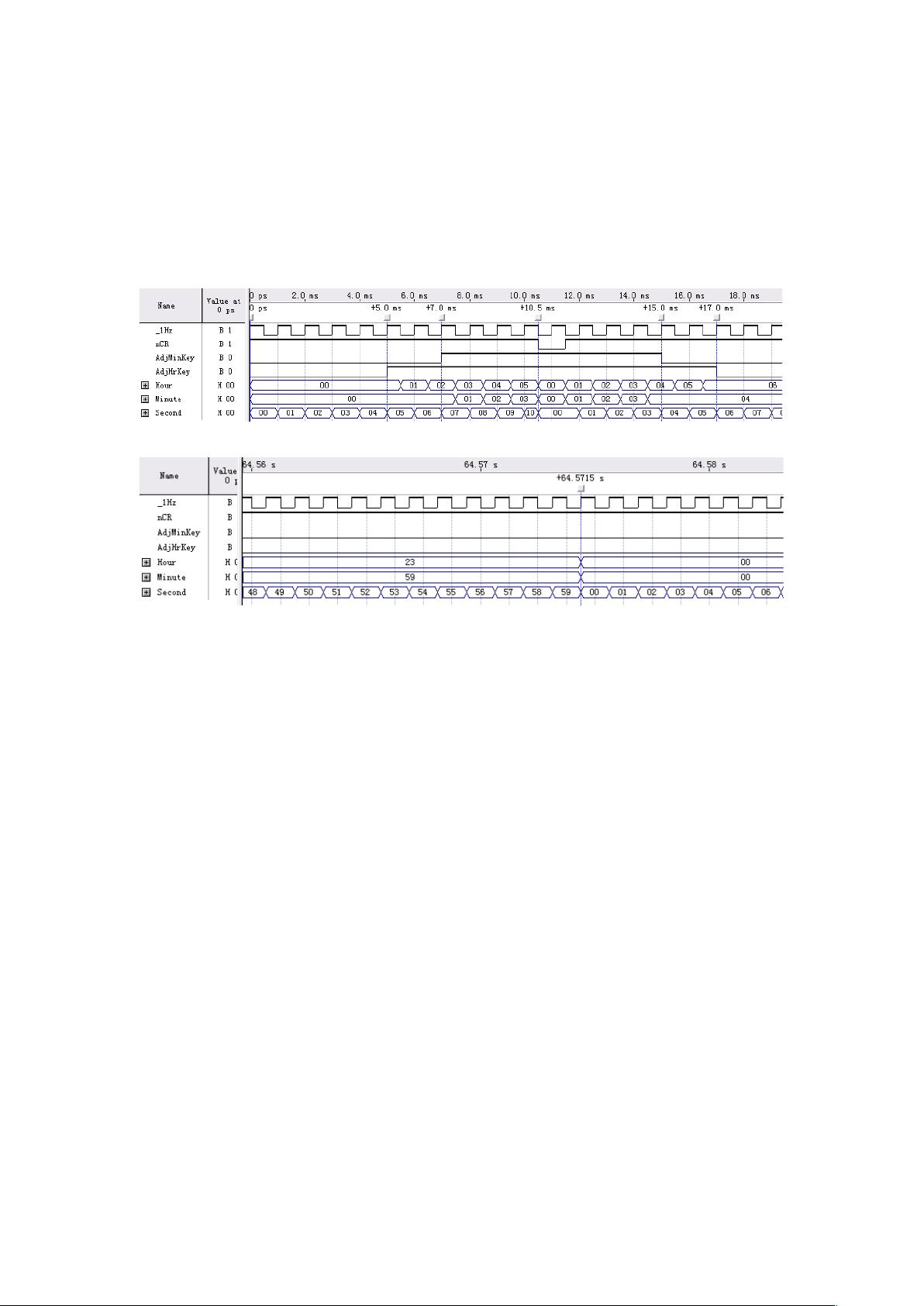

本实验主要围绕FPGA技术,通过设计一个多功能数字钟来训练学生的实践能力。实验目标是构建一个能够准确显示24小时制时间、具备校正功能、整点报时功能以及闹钟功能的数字钟。实验中,学生将使用DE2开发板,利用其内置的50MHz晶振源CLOCK_50作为时钟信号,并通过共阳极数码管显示时间。

首先,数字钟的核心功能包括:

1. **准确计时**:设计的数字钟需能精确地显示时、分、秒,以24小时制计时。

2. **分、时校正**:提供1Hz的校正脉冲,允许用户校正时间。

3. **整点报时**:在59分51秒、53秒、55秒和57秒时播放500Hz低音,59分59秒时播放1kHz高音,以模拟广播电台的报时方式,声音持续1秒。

4. **闹钟功能**:允许用户设定闹钟时间,闹铃持续1分钟,输出500Hz和1kHz交替的方波信号,且持续1秒。设有停止闹铃的控制键。

5. **显示与控制**:使用DE2开发板上的数码管HEX7至HEX2显示时间,使用拨动开关或按键作为控制输入,外接扬声器播放报时和闹铃声音。

设计过程中,数字钟的电路结构通常包含以下几个部分:

1. **振荡器**:产生稳定的高频脉冲,作为时间基准。实验中可使用555定时器与RC电路产生1kHz振荡器,进一步分频得到1Hz秒脉冲。

2. **分频器**:将高频脉冲转换为标准秒脉冲。

3. **计数器**:采用BCD码计数,秒计数器、分计数器和小时计数器依次递进,形成时间的循环计数。

4. **译码显示**:计数器的输出经过译码器转化为数码管可以显示的信号。

5. **控制逻辑**:实现校正、报时和闹钟功能的逻辑控制。

在FPGA实现数字钟的优势在于其灵活性和可编程性,可以根据需求方便地修改和扩展功能。通过编写VHDL或Verilog代码,可以将上述逻辑功能集成到一个可配置的逻辑器件中,实现数字钟电路的硬件级设计。

在实际操作中,学生需要了解和掌握以下知识点:

- FPGA的基本工作原理和VHDL/Verilog语言基础。

- 数字电路设计,包括计数器、分频器、译码器和多路选择器的实现。

- 时序逻辑设计,理解和运用同步和异步电路的概念。

- 数码管显示驱动电路的设计。

- 振荡器和分频器的电路设计与分析。

- 逻辑控制信号的生成与处理,如按键和拨动开关的读取。

- 软硬件协同设计,结合 Quartus II 或其他FPGA开发工具进行仿真和下载。

通过这个实验,学生不仅能学习到FPGA的基础知识,还能提升数字系统设计和动手实践的能力。

2018-07-19 上传

2021-04-08 上传

2021-11-30 上传

2021-10-04 上传

2021-09-26 上传

2021-10-11 上传

2021-10-22 上传

2022-11-30 上传

qq_40389306

- 粉丝: 0

- 资源: 1

最新资源

- GNU make中文手册

- 单片机声控智能小车,单片机控制电路主要由一片89C2051和一片89C52组成。89C2051主要实现对路面黑线的软件检测与纠错;89C52 则作为整个控制部分的核心,负责车速检测、电动机驱动、数据显示等功能。

- 数字集成电路的分类、特点、使用方法

- 电磁干扰与电磁兼容浅谈

- C#面向对象设计模式纵横谈

- 考研专用的计算机组成原理课件

- DWR中文文档!!!!

- PCI设备初始化编程的过程

- Freescale Codewarrior5.0快速入门

- 解释器模式基础,初学者好用的

- Eclipse – 整合开发工具(基础篇

- Verilog的基础知识

- c#窗体重构 窗体重构教程

- 软件设计考试复习题,考试必考

- C常用编程范例参考学习资料

- Elements of Information Theory.pdf